См. 32.

Приведение минимизированной логической функции к базису «ИЛИ-НЕ».

См. 32.

Приведение минимизированной логической функции к базису «И-НЕ».

См. 32.

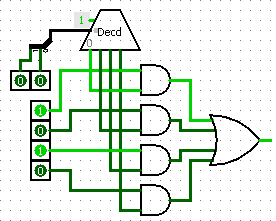

38 Дешифраторы: определение, УГО, области применения, функциональная схема на примере дешифратора 2-4.

Дешифратор – комбинационная схема, обладающая N адресными входами, одним разрешающим входом E и  выходами. На адресные входы подается двоичное число, которое в своем десятичном представлении задает номер выхода. На выходе – унитарный код.

выходами. На адресные входы подается двоичное число, которое в своем десятичном представлении задает номер выхода. На выходе – унитарный код.

Области применения:

· в составе схем управления другими устройствами для последовательной подачи разрешающих сигналов

· в составе схем преобразователей кодов

· для реализации логических функций

Дешифраторы: определение, УГО, области применения, реализация логических функций на дешифраторах достаточной разрядности.

см. 38.

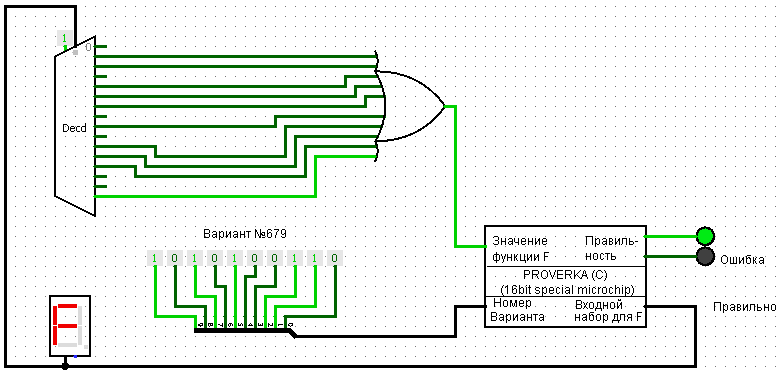

| A | B | C | D | F(A,B,C,D) |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

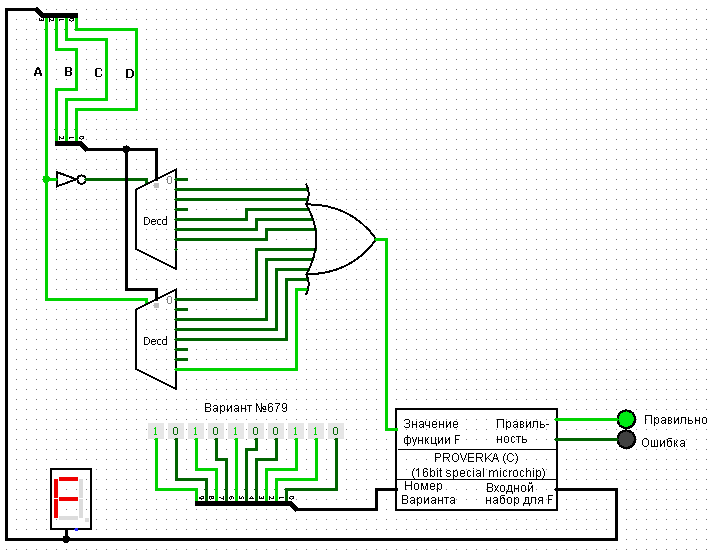

Реализация функции при помощи дешифратора 4-16.

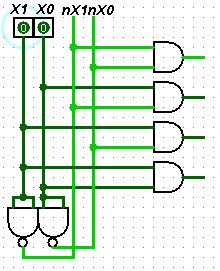

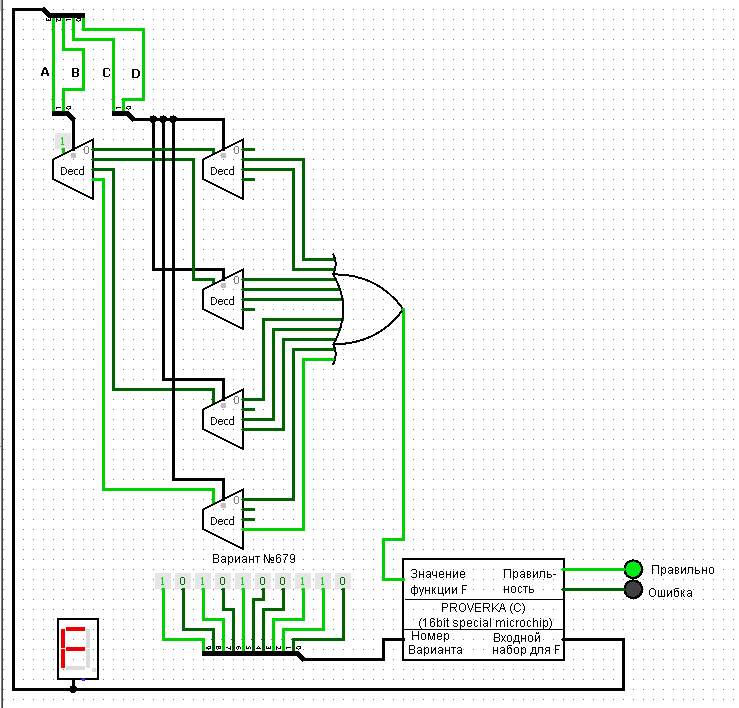

Реализация функции при помощи дешифраторов 3-8.

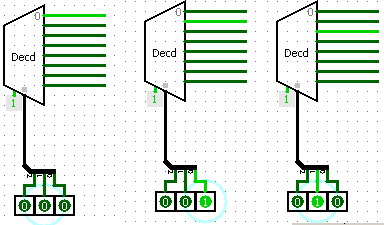

Реализация функции при помощи дешифраторов 2-4.

Дешифраторы: определение, УГО, области применения, реализация логических функций на дешифраторах меньшей разрядности, чем количество переменных.

см. 40.

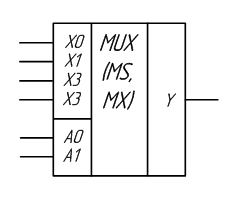

41 Мультиплексоры: определение, УГО, области применения, функциональная схема мультиплексора на примере мультиплексора 4-1.

Мультиплексор – комбинационная схема, имеющая  информационных входов, N адресных входов, (разрешающий вход – опционально) и одним выходом.

информационных входов, N адресных входов, (разрешающий вход – опционально) и одним выходом.

Области применения:

· “Ленивая” реализация логических функций, когда минимизацией можно пренебречь.

· В качестве коммутатора N к 1:

o Для преобразования параллельного кода в последовательный.

o Для поочердного подключения многих источников информации к одному потребителю.

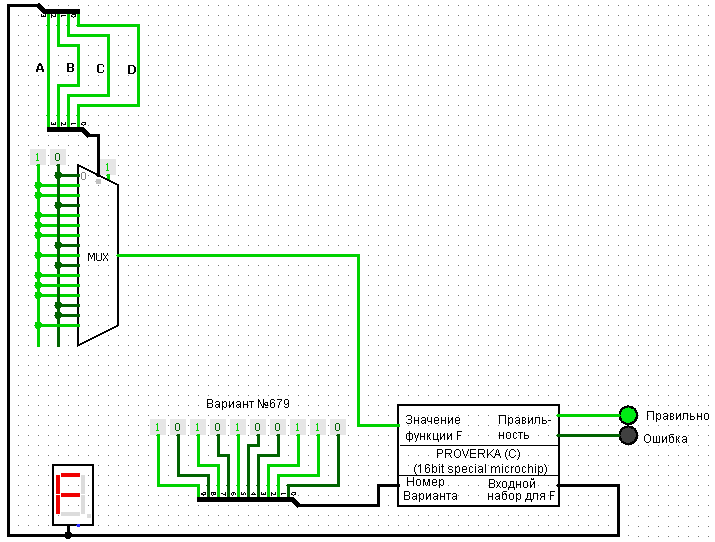

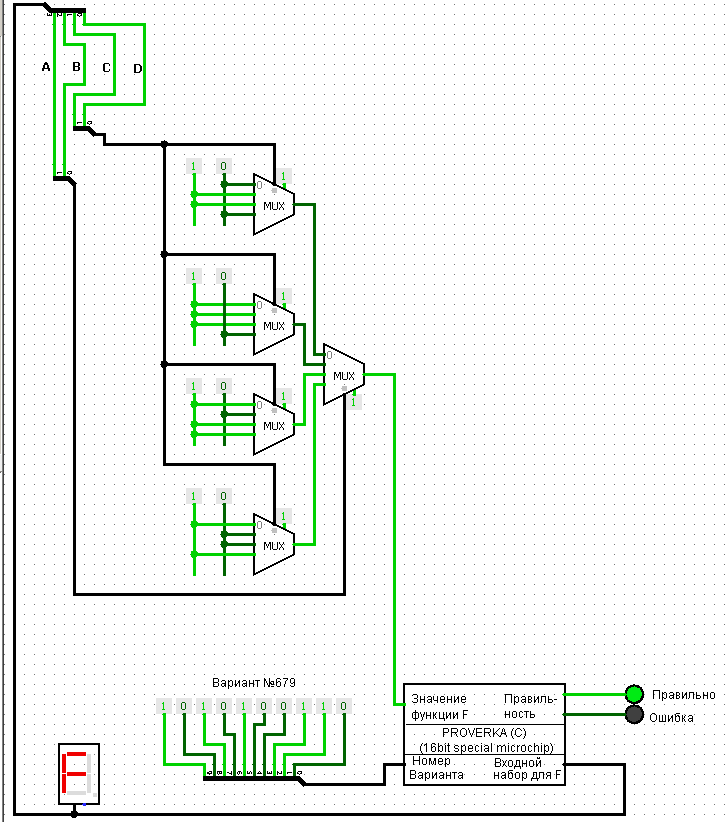

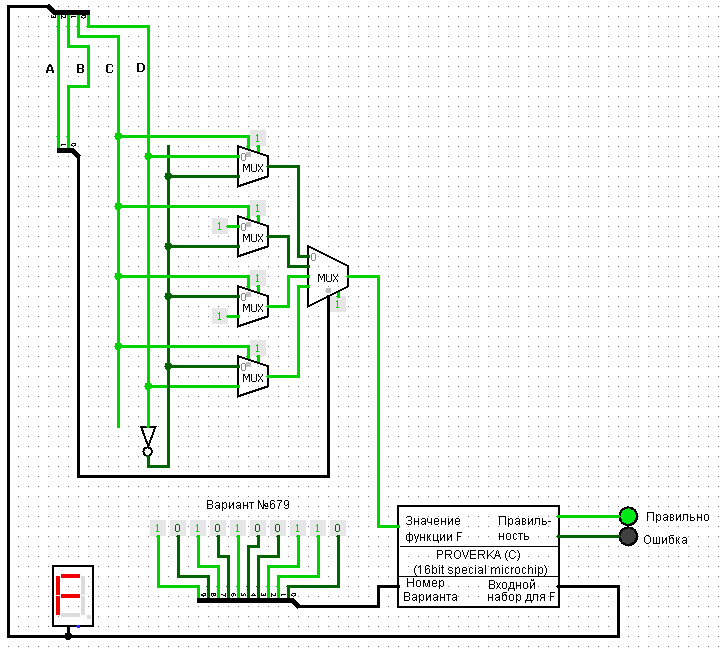

Мультиплексоры: определение, УГО, области применения, реализация логических функций на мультиплексорах достаточной разрядности.

см. 41

Таблица истинности.

| A | B | C | D | F(A,B,C,D) |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

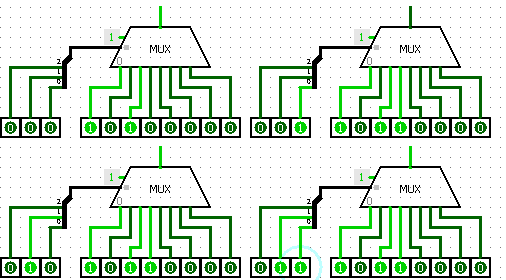

Реализация функции при помощи мультиплексора 16-1.

Реализация функции при помощи мультиплексора 8-1.

Реализация функции при помощи мультиплексоров 4-1.

Реализация функции при помощи мультиплексоров 2-1 и одного мультиплексора 4-1.

Дата: 2019-04-23, просмотров: 598.