Способы преобразования напряжения в код. Процесс преобразования напряжения в код можно реализовать разными способами. На практике наибольшее распространение получили три метода:

- метод последовательного счета, при котором входная аналоговая величина уравновешивается последовательно накапливаемой суммой одинаковых минимальных эталонов, называемых квантами. Момент равенства входной величины и суммы эталонов определяется с помощью одного сравнивающего устройства. Результат преобразования характеризуется числом квантов, накопленных при формировании суммы;

- метод поразрядного кодирования, при котором входная величина последовательно сравнивается с суммой эталонов, накопленных за предыдущие циклы сравнения. «Вес» каждого эталона равен i квантам, где i последовательно принимает значения n-1, n-2, ..., 2, 1, 0 (n - число разрядов АЦП). Если результат сравнения на i-м шаге положителен (входная величина больше накопленной суммы), то соответствующий эталон прибавляется к сумме, и в i-м разряде выходного регистра устанавливается 1. В противном случае эталон не добавляется, разряд устанавливается в 0 и следует переход к следующему, более «легкому» эталону. Сравнение входной величины и суммы эталонов выполняется последовательно одним сравнивающим устройством, результат преобразования характеризуется совокупностью единиц и нулей в выходном регистре;

- метод параллельного сравнения, при котором входная величина одновременно сравнивается с полной совокупностью эталонов, равных 1, 2, 4, 8, ..., n-1 квантам. Результат преобразования характеризуется количеством компараторов, отметивших равенство или превышение входной величины по отношению к данному эталону, и представляется последовательностью единиц и нулей. Для получения выходного позиционного кода требуется соответствующее преобразование этого промежуточного результата.

Как видно, каждый метод требует разных аппаратурных затрат (числа эталонов и компараторов) и обеспечивает разное время преобразования. В зависимости от системных требований выбирается тот или иной метод.

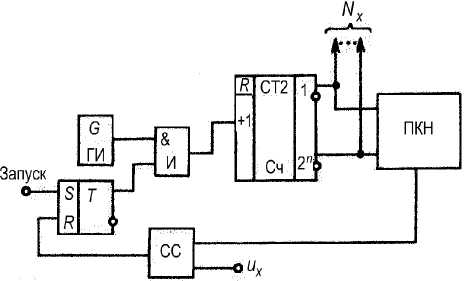

Преобразователь последовательного счета (с обратной связью). Для реализации принципа последовательного счета, который был кратко описан выше, требуется один эталон, равный кванту. Он многократно используется для уравновешивания входной аналоговой величины. Именно в таком виде этот принцип реализован в преобразователе «напряжение - код» (ПНК), структурная схема которого показана на рис. 10.1.

Рисунок 10.1

Импульс запуска через элемент И поступает на счетчик. Обратная связь реализована с помощью преобразователя код- напряжение (ПКН): выходы счетчика соединены с входами ПКН и при поступлении на счетчик очередного импульса вместе с увеличением на единицу его содержимого возрастает на одну «ступеньку» напряжение на выходе ПКН. Величина приращения напряжения за один такт равна кванту. Компаратор (схема сравнения СС) закроет элемент И, когда выходное напряжение ПКН достигнет уровня входного сигнала ux. Состояние счетчика в этот момент является цифровым выходным сигналом ЦАП.

Основной недостаток этого простого способа - зависимость времени преобразования от уровня входного сигнала, причем это время может быть довольно велико (2n периодов тактовых импульсов для n-разрядного преобразователя при входном сигнале, близком по уровню к величине полного диапазона преобразования).

В модифицированном варианте АЦП последовательного счета - так называемом «следящем» АЦП - используется реверсивный счетчик. Схема сравнения выдает разные сигналы в зависимости от соотношения между входным сигналом и выходным напряжением ПКН (с точностью до величины кванта). В зависимости от знака рассогласования между uвх и uПКН импульс, поступающий на вход счетчика, либо суммируется с его содержимым, либо вычитается из него.

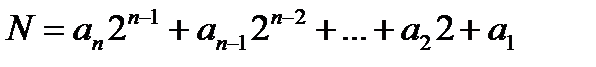

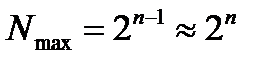

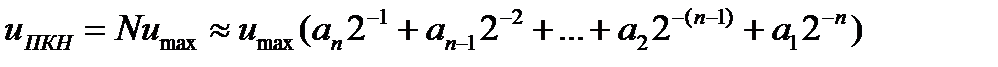

Для реализации метода последовательного приближения необходим цифро-аналоговый преобразователь типа «код - напряжение». Обычно преобразователи этого типа выполняют по параллельной схеме: преобразование во всех разрядах происходит одновременно с учетом «веса» разряда. Если на вход такого ПКН подается код:

и максимальному значению кода  соответствует выходное напряжение umax, то коду N будет соответствовать напряжение

соответствует выходное напряжение umax, то коду N будет соответствовать напряжение

Видно, что выходной сигнал состоит из п слагаемых, каждое из которых имеет свой коэффициент деления, определяемый номером данного разряда.

Последнее соотношение реализуется двумя способами: 1) матрицей с полным набором весовых сопротивлений и 2) матрицей с двумя весовыми сопротивлениями.

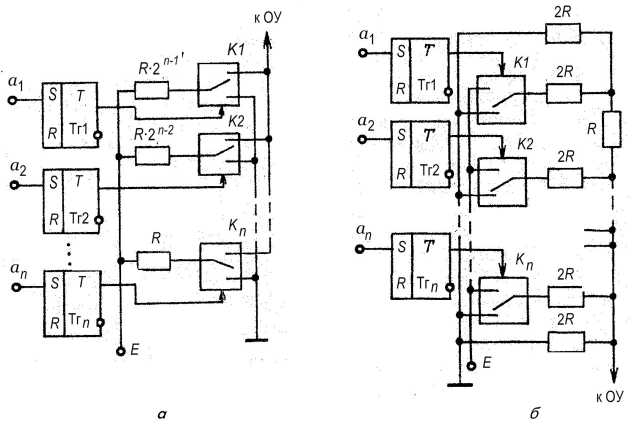

В первом случае весовые сопротивления выбираются равными Rx2n-i. На рис. 10.2, а приведена схема такого ПКН. Входной код поступает на разрядные триггеры Тг1, Тг2, ..., Тгп, управляющие разрядами ПКН через двухпозиционные ключи. Если в i-м разряде кода имеется 1, то ключ Ki подсоединит резистор Rx2n-1 к входу суммирующего ОУ. В противном случае этот вход будет заземлен.

Рисунок 10.2

Недостаток преобразователя с полным набором весовых сопротивлений - необходимость точного подбора сопротивлений в широком диапазоне номиналов. Особенно трудно сделать это при реализации ПКН посредством интегральной технологии. Этот недостаток отсутствует во втором типе преобразователя - с двумя номиналами весовых сопротивлений (R и 2R), структурная схема которого показана на рис. 10.2, б.

В этом типе ПКН коэффициент деления реализуется путем соответствующего расположения ветви, поскольку коэффициент передачи напряжения от одной ветви к следующей равен 1/2. Каждая ветвь составляет для источника питания нагрузку 3R, а выходное сопротивление ПКН постоянно и равно 2R/3 независимо от значения кода на входе ПКН. Наличие в i-м разряде единицы создаст на входе ОУ составляющую напряжения, равную по величине 2-(n-i)E/3.

При использовании ПКН необходимо учитывать, что при срабатывании токовых переключателей различия во времени коммутации, сдвиги уровня выходного аналогового сигнала и паразитные емкости вызывают появление выбросов выходного напряжения. Выброс максимальной амплитуды до 50% значения полной шкалы происходит, когда ключи всех разрядов срабатывают одновременно (например, при переходе от кода 011...1 на код 100...0). Выброс может длиться несколько сотен наносекунд и в быстродействующих схемах нужно предусматривать в составе таких ЦАП специальные сглаживающие устройства.

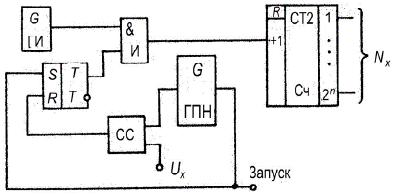

Преобразователь с промежуточным преобразованием напряжения во временной интервал. Схема преобразователя такого типа изображена на рис. 10.3, а; временная диаграмма его работы показана на рис. 10.3, б.

Такой ПНК состоит из преобразователя временного интервала в код и двух дополнительных узлов: генератора пилообразного напряжения ГПН и схемы сравнения СС, выполняющих преобразование напряжения во временной интервал.

Импульс запуска поступает на ГПН, который начинает вырабатывать пилообразное напряжение Un; одновременно импульс запуска с помощью триггера Тг открывает элемент И и импульсы ГИ поступают на счетчик Сч. В момент равенства Uп и Ux срабатывает схема СС, формируя признак конца временного интервала. Соответствующий импульс ставит триггер Тг в нулевое состояние, и импульсы ГИ перестают поступать на счетчик (работа преобразователя временного интервала в код была рассмотрена выше).

Рисунок 10.3

Для рассмотренного типа преобразователя справедливо соотношение:

Uп = Uп0 + at, (10.1)

где Un0 - начальный уровень пилообразного напряжения; a - скорость изменения напряжения. Так как при Ux = Un имеем t = Tx, то из (10.1) можно найти значение искомого временного интервала:

Tx = (Ux - Uп0)/a. (10.2)

Если не учитывать погрешности преобразования временного интервала в код, то из (10.2) следует, что выходной код N = Тх/ tги= (Ux – Uп0)/atrи, где tги - период следования импульсов ГИ.

Интегрирующие преобразователи. В преобразователе такого типа использовано накопление заряда конденсатором при протекании среднего тока, поступающего на аналоговый вход. Этот заряд сравнивается с зарядом, обеспечиваемым эталонным током, после чего анализируются соответствующие временные соотношения. Простота интегрирующих преобразователей обеспечивает им наилучшее соотношение между высокой точностью и малой стоимостью по сравнению с любыми аналого-цифровыми устройствами.

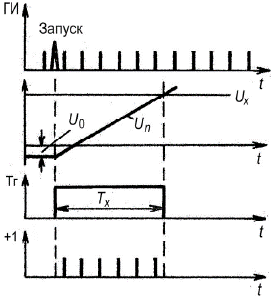

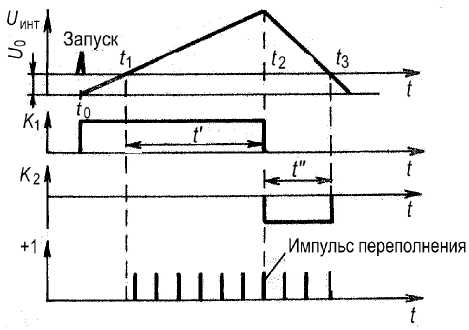

Наиболее совершенным является метод двойного, или компенсационного интегрирования. Традиционная структура интегрирующих АЦП содержит два основных блока: аналоговый, выполняющий преобразование входного напряжения в длительность временного интервала, и цифровой, обеспечивающий измерение временного интервала и формирования сигналов управления аналоговым блоком. Структурная схема такого преобразователя приведена на рис. 10.4; временные диаграммы - на рис. 10.5.

Рисунок 10.4 Рисунок 10.5

Импульс запуска поступает в момент времени t0 и, воздействуя на триггер Тг1, с его помощью открывает ключ K1, после чего преобразуемое напряжение Ux подается на вход интегратора Инт.

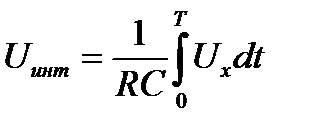

Выходное напряжение интегратора изменяется по следующему закону:

где RC - эквивалентная постоянная времени интегратора. Выходное напряжение интегратора подается на один их входов схемы сравнения СС, на второй вход которой подается постоянное напряжение U0. До начала интегрирования Uинт < U0, а в процессе интегрирования Uинт растет. В момент времени t1 напряжение Uинт становится равным U0 и схема сравнения срабатывает. Выходной импульс схемы СС (выход 1) перебрасывает триггер Тг3, в результате чего открывается элемент И и импульсы генератора ГИ начинают поступать на счетчик Сч. Интегрирование напряжения Ux производится в течение фиксированного промежутка времени ∆t = t2 - t1. Конец этого временного интервала фиксируется счетчиком, который в момент времени t2 выдает импульс переполнения, поступающий на триггеры Тг1 и Тг2.

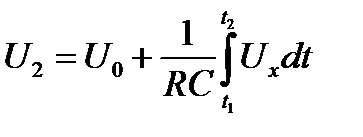

К моменту времени t2 напряжение на выходе интегратора достигает величины

(10.3)

(10.3)

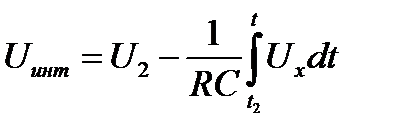

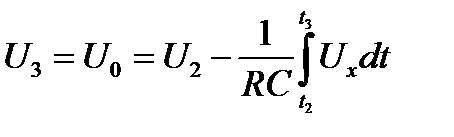

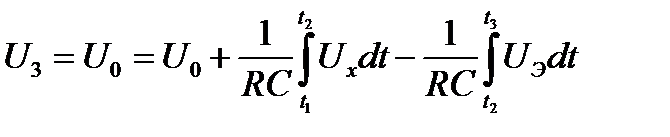

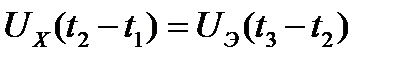

Вследствие появления импульса переполнения счетчика Сч и переброса триггеров Тг1 и Тг2 ключ К1 закрывается, а ключ К2 открывается; при этом вход интегратора переключается с напряжения Ux на напряжение Uэ, имеющее полярность, обратную полярности напряжения Ux. После момента t2 импульсы генератора ГИ продолжают поступать на счетчик Сч, а напряжение на выходе интегратора начинает уменьшаться по следующему закону:

(10.4)

(10.4)

Когда напряжение на выходе интегратора уменьшится до значения U0, схема сравнения перейдет в исходное положение и по выходу 2 перебросит триггеры Тг2 и Тг3 в нулевое состояние. При этом сигнал с выхода триггера Тг2 разомкнет ключ К2 и напряжение Uэ отключится от входа интегратора, а сигнал с выхода триггера Тг3 запретит подачу импульсов ГИ на счетчик. В счетчике будет зафиксирован код N = ∆Т/ tги, где ∆Т - временной интервал между моментами t2 и t3.

Если (10.4) представить для момента времени t = t3, то получим:

или, подставив значение U2 из (10.3),

(10.5)

(10.5)

Если считать, что напряжения UХ и UЭ постоянны во время интегрирования, то из (10.5) получим:

а так как t2 – t1 = 2ntги , где п - число разрядов в счетчике, то N = (Ux / UЭ) 2n .

Можно отметить следующие положительные свойства этого типа ПНК:

а) получающийся в результате преобразования код прямо пропорционален входному напряжению;

б) медленные вариации частоты генератора и медленные изменения эквивалентной постоянной времени не сказываются на точности преобразования;

в) влияние всех видов помех во входном сигнале уменьшается; если время интегрирования выбрано равным периоду частоты питающей сети, то аддитивная сетевая помеха полностью подавляется, поскольку интеграл от синусоидальной функции в пределах периода равен нулю.

Основной недостаток преобразователей подобного типа состоит в том, что на результатах преобразования сказываются неидеальность интегратора (отклонение закона интегрирования от линейного) и появление дрейфа в его выходном напряжении.

Контрольные вопросы:

1 Способы реализации процесса преобразования напряжения в код

2 Объясните принцип работы преобразователя последовательного счета

3 В чем сущность модифицированного варианта АЦП последовательного счета?

4 Расъясните схему по которой выполняют преобразователь типа «код - напряжение».

5 В чем преимущество схемы преобразователя с двумя номиналами весовых сопротивлений (R и 2R)?

6 Расъясните схему преобразователя с промежуточным преобразованием напряжения во временной интервал.

7 Какой принцип заложен в основу интегрирующих преобразователей?

8 Положительные свойства и основной недостаток интегрирующих ПНК.

Лекция 11 Преобразователи напряжения в код, построенные по принципу поразрядного кодирования. Преобразователи напряжения в код, построенные по принципу параллельного сравнения

Преобразователи напряжения в код, построенные по принципу поразрядного кодирования

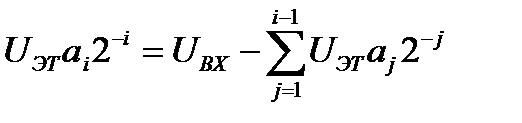

Алгоритм работы преобразователей этого типа сводится к последовательному выполнению операции деления входного напряжения на эталонное напряжение старшего разряда, затем - полученного остатка на эталонное напряжение следующего разряда и т.д. Для двоичного кода i-й такт преобразования состоит в определении разрядного коэффициента кода аi, удовлетворяющего соотношению:

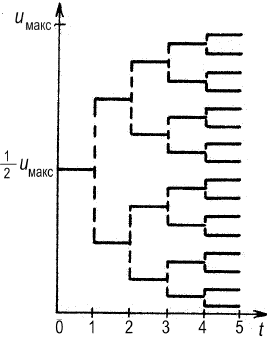

Генерируемое дискретное напряжение сходится к уровню входного аналогового сигнала путем ряда последовательных приближений, причем каждый шаг равен половине предыдущего шага (рис. 11.1).

Рисунок 11.1

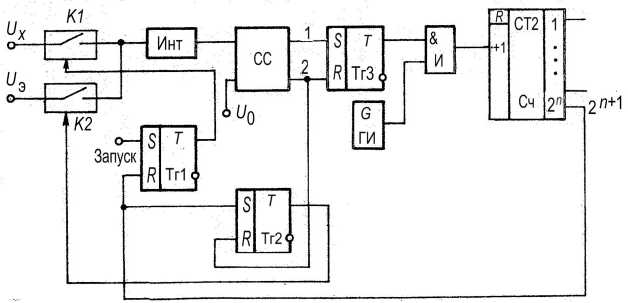

Алгоритм последовательного приближения обычно реализуется следующим схемным способом.

Процессом аналого-цифрового преобразования управляет регистр последовательной аппроксимации РПА (он состоит из сдвигающего регистра Рг и триггеров памяти Тг1 - Тгn), ЦАП, формирующего выходной код, и логических схем управления).

Преобразование начинается с поступлением импульса запуска. Триггер старшего разряда Тгn устанавливается в 1, а все остальные - в 0. Одновременно 1 записывается в сдвигающий регистр.

Если Uвх > Un = Uэт /2 (Un - входное напряжение ЦАП, соответствующее единице старшего разряда), то на выходе компаратора импульс отсутствует и 1 в Тгn сохранится. Если Uвх < Un, то выходной импульс компаратора через соответствующую схему И установит Тгn в состояние 0. Одновременно произойдет сдвиг в сдвигающем регистре и в следующий триггер памяти запишется 1. Таким же образом выполняются все остальные циклы. Следует заметить, что регистры последовательной аппроксимации выпускаются в виде отдельных микросхем (типа К155ИР17).

Скорость АЦП последовательного приближения определяется временем срабатывания логических схем, внутреннего ЦАП и компаратора и при фиксированной частоте линейно зависит от числа разрядов. Этот способ обеспечивает недорогое при среднем (порядка 1 МГц) быстродействии техническое решение. Он использован в отечественных микросхемах типа К1108ПВ1 и К1108ПВ2 [5].

Дата: 2019-04-23, просмотров: 886.