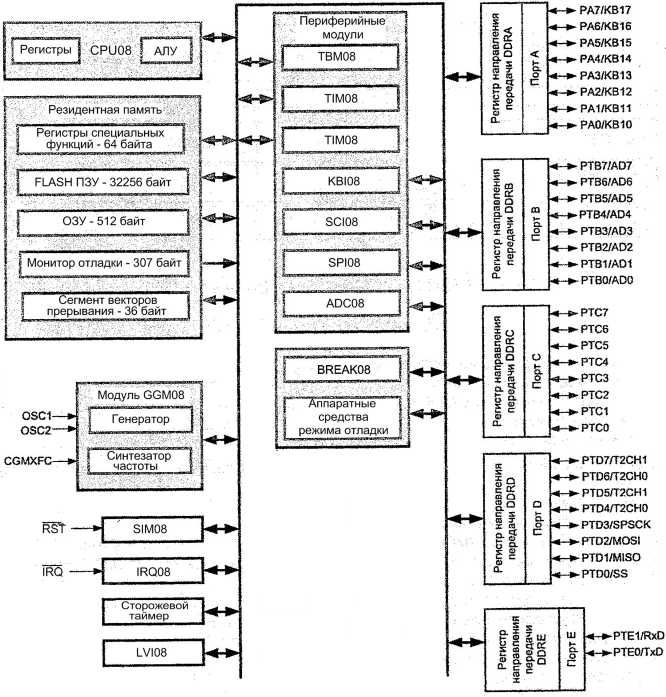

Узлы ОМК и организацию их взаимодействия рассмотрим на примере микроконтроллера семейства НС08 (рис. 13.2).

Центральный процессор выполняет операции над 8-разрядными операндами, поддерживает 11 способов адресации, имеет команды умножения и деления. Он содержит АЛУ и пять регистров:

1) аккумулятор - 8-разрядный регистр для хранения операндов и результатов операций;

2) индексный 16-разрядный регистр участвует в формировании адреса операнда, а также может использоваться для промежуточного хранения результатов и как источник одного из операндов в операциях умножения и деления;

3) программный счетчик - 16-разрядный регистр, содержащий адрес текущей команды или адрес операнда, используемого в текущей команде;

4) указатель стека - 16-разрядный регистр, содержащий адрес верхушки стека;

5) регистр слова состояния процессора - 8-разрядный регистр, содержит шесть флагов условий: переноса, нулевого результата, отрицательного результата, переполнения, дополнительного переноса и бит глобальной маски прерывания.

Рисунок 13.2

Система команд процессора CPU08 включает 90 команд, которые делятся на шесть групп:

- команды загрузки и пересылки (всего 13 команд) осуществляют перемещение данных между ячейками памяти и регистрами центрального процессора;

- арифметические команды (14 команд) выполняют операции сложения, вычитания, инкремента и декремента, однобайтового и двухбайтового сравнения, умножения и деления;

- логические команды и команды сдвигов (15 команд) - логическое И, ИЛИ, Исключающее ИЛИ, различные операции сдвига, операция взятия обратного и дополнительного кода;

- команды битового процессора (всего 6 команд) устанавливают в определенные состояния отдельные биты в ячейках ОЗУ или в регистрах;

- команды управления ходом вычислительного процесса (40 команд), в состав которых входят: команды условных и безусловных переходов, вызова подпрограмм и обслуживания прерываний;

- команды перехода к режимам пониженного энергопотребления (2 команды) переводят МК в режим ожидания или останова.

Режимы работы

1. Режим исполнения прикладной программы. Работа при номинальной частоте генератора; активизированы все необходимые периферийные модули.

2. Режим ожидания. Для экономии энергии понижается частота таймера и может быть отключена часть периферийных устройств.

3. Режим останова. Вводится с помощью команды STOP. Вся периферия неактивна.

4. Режим отладки. Обеспечивает программирование и отладку МК с помощью последовательного интерфейса с ведущим персональным компьютером.

Резидентная память состоит из энергонезависимого запоминающего устройства (FLASH ПЗУ), основного ОЗУ, регистров специальных функций, монитора отладки и сегмента векторов прерываний.

Функциональная программа обычно хранится в памяти типа FLASH, константы - в перепрограммируемом ПЗУ с электрическим стиранием (EEPROM ПЗУ), которое имеет режим побайтного программирования. Такая организация позволяет в ходе выполнения программы изменять содержимое EEPROM ПЗУ. Время перепрограммирования - менее 1 с.

В состав ОЗУ ОМК входит оперативное ЗУ статического типа.

Модуль FLASH-памяти имеет в своем составе повышающий преобразователь напряжения, который позволяет выполнять стирание и программирование FLASH ПЗУ под управлением программы, размещенной в ОЗУ, без подключения внешнего источника напряжения программирования.

Аналого-цифровые преобразователи. Характерная особенность НС08 - интегрированный на кристалле ОМК модуль многоканального аналого-цифрового преобразователя ADC08 (АЦП). Многоканальный аналоговый коммутатор на его входе служит для подключения одного из источников аналоговых сигналов. Выбор источника сигнала для измерения осуществляется посредством записи номера канала коммутатора в соответствующие разряды регистра управления АЦП.

АЦП выполняется по схеме последовательного приближения или поразрядного уравновешивания. Разрешающая способность в разных моделях ОМК составляет от 8 до 12 бит, время преобразования - от 5 до 32 мкс, число каналов - от 8 до 12.

Модуль системной интеграции SIM08 управляет всеми подсистемами микроконтроллера. Он формирует множество сигналов, которые обеспечивают совместное функционирование центрального процессора, блоков памяти и периферийных модулей. В частности, он содержит контроллер прерываний, который производит сбор и ранжирование внутренних и внешних запросов, формирует вектор текущего прерывания в соответствии с таблицей приоритетов, управляет процедурой перехода к выполнению подпрограммы перехода и выходом из нее.

Модуль управления питанием CGM08 состоит из генератора и синтезатора частоты. Он обеспечивает тактирование от генератора кварцевого резонатора или от синтезатора частоты, который позволяет снизить частоту резонатора.

Порты ввода/вывода. В процессоре НС08 имеется 33 двунаправленные линии ввода/вывода: порт А - для сканирования клавиатуры, порт В - аналоговые входы встроенного АЦП; порты С, D, E - для связи с выходами периферийных модулей.

Контроллеры последовательного ввода/вывода. Задачи, которые решаются с помощью контроллеров последовательного ввода/вывода, могут быть условно разделены на три группы:

1) связь встраиваемой микропроцессорной системы с системой управления верхнего уровня;

2) связь с внешними по отношению к ОМК периферийными устройствами, а также с датчиками физических величин с последовательным выходом;

3) интерфейс связи с локальной сетью в мультимикропроцессорных системах.

В составе ОМК семейства НС08 имеются два контроллера последовательного интерфейса - синхронного и асинхронного. Модуль синхронного интерфейса (SPI08) предназначен для высокоскоростного обмена между ОМК и периферийными микросхемами, такими как АЦП и ЦАП, FLASH-память большой емкости и др.

Модуль асинхронного интерфейса (SCI08) организует обмен с устройствами управления верхнего уровня. Аппаратные средства SCI08 делятся на две подсистемы: приемника и передатчика. Основу каждой подсистемы составляют сдвиговый регистр и буферный регистр данных.

Модуль сброса при некорректных операциях и адресах IRQ08 срабатывает, когда появляется запрещенная команда (она не может интерпретироваться существующей системой команд) или несуществующий (для данной серии микроконтроллеров) адрес.

Модуль сторожевого таймера генерирует сигнал RESET через определенное время, если его не сбросить внутри этого временного интервала. Для осуществления этого сброса программист должен регулярно вставлять в программу команду сброса этого таймера.

Аппаратные средства режима отладки формирует необходимые уровни сигналов для перевода микроконтроллера в отладочный режим работы (IRQ, RST, частота тактирования и т.д.). Модуль BREAK08 реализует остановы по контрольным точкам, в которых можно проверить содержимое регистров. Для этого в регистр модуля заносится абсолютный адрес контрольной точки и запускается программа, которая сравнивает его с кодом на внутренней магистрали адреса. При равенстве кодов генерируется прерывание, микроконтроллер переходит на программу монитора отладки, которая считывает его внутренние программно доступные регистры в память и отображает их на экране дисплея.

Контрольные вопросы:

1 Перечислите виды средств переработки информации в АСУ реального времени.

2 Дайте определения скалярного, суперскалярного и векторного процессоров.

3 Приведите определение микроконтроллера.

4 В чем различия ОМК с CISC-архитектурой и RISC-архитектурой?

5 Разъясните модульную структуру ОМК.

6 Состав МК CISC-типа.

7 Назначение центрального процессора МК CISC-типа.

8 Какие команды входят в систему команд процессора CPU08?

9 Режимы работы МК CISC-типа.

Лекция 14 Функционирование узлов микроконтроллера RISC-типа

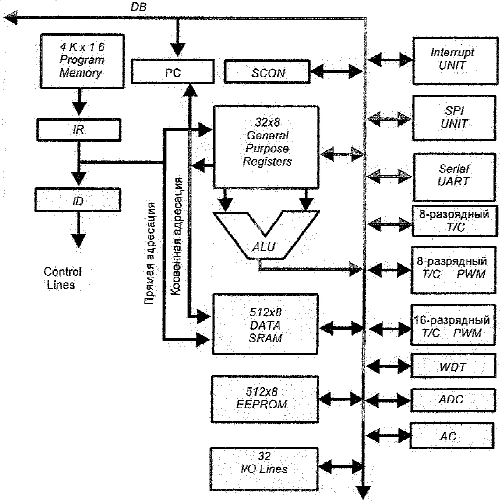

Типичными представителями RISC-процессоров являются 8-разрядные микроконтроллеры общего назначения фирмы Atmel Corp. Их архитектуру рассмотрим на примере БИС АТ90S8535 (рис. 14.1).

Рисунок 14.1

Основой архитектуры являются раздельные шины и области памяти для команд и данных (гарвардская архитектура). Разрядность шины памяти программ расширена до 16 бит. В микроконтроллере используется технология конвейеризации, вследствие чего цикл «выборка-выполнение» команды существенно сокращен. Одноуровневый конвейер в общем потоке позволяет выполнять короткие команды за один машинный цикл - за один период тактовой частоты.

Структурная схема контроллера содержит (см. рис. 14.1):

- арифметико-логическое устройство (ALU), выполняющее 133 различных команды; разрядность обрабатываемого слова - 8 бит;

- регистровый файл (General Purpose Register), состоящий из регистров общего назначения, занимает младшие 32 байта в общем адресном пространстве; шесть из 32 регистров могут использоваться как три 16-разрядных указателя адреса при косвенной адресации данных;

- память команд (Program Memory), которая содержит 4К 12-разрядных ячеек FLASH-памяти с числом циклов перезаписи не меньше 1000 и с способностью самопрограммирования, то есть микроконтроллер способен самостоятельно, без внешнего программатора изменять содержимое ячеек памяти программ. Это дает возможность записать во внешнюю энергонезависимую память несколько рабочих версий программы, а потом по мере необходимости или по реакции на внешние или внутренние логические условия перегружать рабочие программы в тот же микроконтроллер без извлечения его из печатной платы;

- память данных, состоящая из внутренней оперативной статической памяти SRAM и энергонезависимой памяти с электрическим стиранием EEPROM. Этот тип памяти используется для хранения промежуточных данных, констант, таблиц перекодировок, калибровочных коэффициентов и т.п. Число циклов перезаписи - не менее 100000;

- периферия, традиционно состоящая из 8-разрядных портов последовательного ввода/вывода (Serial UART) с блоком управления (SCON), таймеров/счетчиков (T/C) и контроллера прерываний (PC). Число независимых линий портов вода/вывода - до 53. Каждый разряд порта может быть запрограммирован на ввод или на вывод информации. Мощные выходные драйверы обеспечивают токовую нагрузочную возможность 20 мА по линии порта при максимальном значении 40 мА. Таймеры/счетчики могут работать как таймеры от внутреннего источника опорной частоты и как счетчики внешних событий с внешним тактированием.

Периферийными устройствами являются только блок последовательного периферийного интерфейса (SPI), сторожевой таймер (WDT) и аналоговый компаратор (AC). Блок SPI предназначен для последовательного ввода и вывода данных и используется для программирования микроконтроллера после его установки на печатную плату. Сторожевой таймер предназначен для перезапуска программы при появлении сбоя в ходе ее выполнения: программа, которая работает без сбоя, периодически сбрасывает сторожевой таймер, не допуская его переполнения. Аналоговый компаратор сравнивает по величине напряжения сигналы, поступающие на два его входа; результат используется во внутренних цепях микроконтроллера;

- аналого-цифровой преобразователь (ADC) построен по классической схеме поразрядного уравновешивания с устройством выборки/хранения. Каждый из аналоговых входов может быть соединен со входом устройства выборки/хранения через аналоговый мультиплексор. Разрядность АЦП составляет 10 бит. АЦП может работать в двух режимах - однократное преобразование по любому выбранному каналу и последовательный циклический опрос всех каналов.

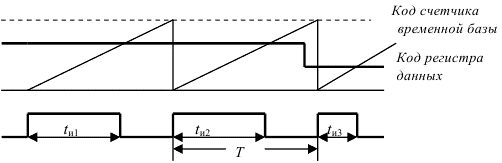

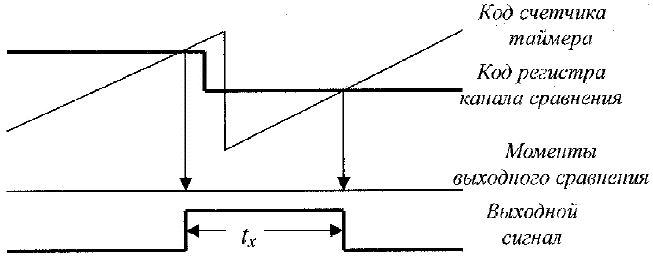

В режиме широтно-импульсной модуляции (ШИМ-генератор) на выходе блока формируется последовательность импульсов с периодом, равным периоду работы счетчика временной базы, и с длительностью, пропорциональной коду в регистре данных (рис. 14.2). Назначение счетчика команд (R), контроллера прерываний (PC) и дешифратора команд (D) общеизвестно.

Многие МК имеют специализацию, т.е. специальные встроенные функциональные особенности архитектуры.

Рисунок 14.2

Контрольные вопросы:

1 Приведите примеры типичных представителей RISC-процессоров.

2 Опишите архитектуру RISC-процессора на примере БИС АТ90S8535.

3 Какие основные узлы содержит структурная схема контроллера RISC-типа?

4 Перечислите периферийные устройства МК RISC-типа.

5 Последовательность импульсов, формируемые на выходе блока ADC в режиме широтно-импульсной модуляции (ШИМ-генератор).

Лекция 15 Специализированные микроконтроллеры

Однокристальные микроконтроллеры с интегрированными устройствами высокоскоростного ввода/вывода ориентированы на решение задач управления объектами и процессами в реальном масштабе времени. Структурная схема содержит:

• модуль центрального процессора (ЦП);

• контроллер памяти;

• контроллер прерываний;

• сервер периферийных транзакций;

• ПЗУ;

• блок АЦП с устройством выборки/хранения и мультиплексором;

• встроенный трехканальный ШИМ-генератор;

• последовательный порт,

• порты ввода/вывода;

• сторожевой таймер;

• модуль высокоскоростного ввода/вывода.

Модуль ЦП состоит из АЛУ, регистра признаков, устройства микропрограммного управления и регистрового файла, который представляет собой массив регистров, т.е. ОЗУ статического типа. ЦП связан с контроллером памяти, контроллером прерываний и встроенными периферийными устройствами внутренней 16-разрядной шиной.

Контроллер памяти осуществляет операции выборки/записи данных во внешнюю или внутреннюю память данных или команд. В состав контроллера памяти входит 4-байтная очередь команд.

Контроллер прерываний предназначен для эффективного управления в реальном времени. Обработки запросов прерываний осуществляется с учетом установленного уровня приоритета. В качестве запросов прерываний могут использоваться:

• внешние сигналы;

• запросы от интегрированных периферийных устройств;

• команды вызова подпрограмм обработки прерываний.

Сервер периферийных транзакций выполняет функции периферийного процессора ввода/вывода и освобождает ЦП от выполнения некоторых типичных операций ввода/вывода. Сервер периферийных транзакций работает по прерываниям, но обслуживает их не программно, а аппаратно.

ПЗУ масочного типа или однократно программируемое емкостью от 8К×8 до 32К×8 байт.

В однократно программируемом ПЗУ (OTPROM - One-Time Programmable ROM) программированию подлежат только те разряды, которые после программирования должны содержать «0».

АЦП состоит из аналогового мультиплексора, устройства выборки/хранения и АЦП, выполненного по способу поразрядного уравновешивания. Разрядность преобразователя - 8 двоичных разрядов. Время выборки - 1 мкс, время преобразования 10 - 20 мкс.

Модуль высокоскоростного ввода/вывода предназначен для формирования периодических во времени сигналов (например, сигнала ШИМ для прямого цифрового управления инверторами напряжения приводов переменного или постоянного тока) и непосредственного измерения временных интервалов между внешними событиями. Информация о событии и времени генерации события в виде команды записывается в ассоциативную память. Каждая команда задает:

• тип события (сброс или установка потенциала на внешнем контакте, запуск АЦП, запуск программных таймеров);

• способ реагирования ЦП на событие - информация о том, будет ли генерироваться прерывание для обслуживания события;

• номер таймера (0 или 1), используемый для контроля текущего реального времени;

• время генерации события.

В каждом машинном такте (100 нс при тактовой частоте 20 МГц) происходит сравнение времени генерации события с реальным временем, которое отсчитывает таймер. Если они совпадают, то генерируется заданное командой событие.

Встроенный трехканальный ШИМ-генератор имеет ограничения на частоту сигналов (39,1 и 19,5 кГц) и не имеет ограничений на скважность импульсов: она регулируется от 1/255 до 1 с дискретностью 1/255. Он эффективно используется для прямого цифрового управления электронными коммутаторами, а также для формирования аналоговых задающих сигналов в цифроаналоговых системах управления.

Последовательный порт представляет собой универсальный синхронно-асинхронный приемопередатчик, который может настраиваться на один синхронный режим и три асинхронных.

Массив процессора событий реагирует на такие типы внешних событий: переход сигнала на внешнем выводе из логической единицы в логический нуль и наоборот; переключение уровня сигнала на внешнем выводе. Модуль процессора событий содержит 16-разрядный счетчик временной базы и некоторое количество универсальных каналов захвата/сравнения.

Универсальные каналы захвата/сравнения в процессоре событий могут работать в одном из трех режимов: 1) режим входного захвата; 2) режим выходного сравнения; 3) режим широтно-импульсной модуляции (ШИМ).

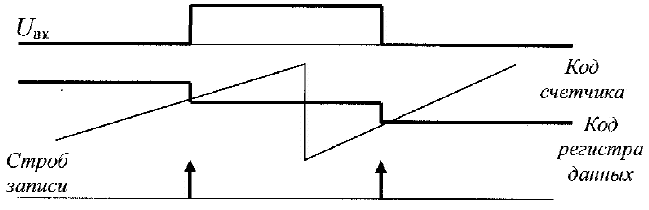

Принцип действия входного захвата такой (рис. 15.1): схема детектора событий «наблюдает» за уровнем напряжения uвх на одном из входов МК. При изменении уровня логического сигнала вырабатывается строб записи, и текущее состояние счетчика таймера записывается в 16-разрядный регистр данных. Разность кодов даст длительность входного сигнала.

Рисунок 15.1

Принцип действия канала выходного сравнения таков (рис. 15.2): многоразрядный цифровой компаратор непрерывно сравнивает изменяющийся во времени код счетчика таймера с кодом, который записан в 16-разрядном регистре канала сравнения. В момент равенства кодов на одном из выводов МК устанавливается заданный уровень логического сигнала.

Рисунок 15.2

В режиме ШИМ на выводе ОМК формируется последовательность импульсов с периодом, равным периоду работы счетчика временной базы. Длительность импульса прямо пропорциональна коду в регистре данных канала.

Однокристальные микроконтроллеры с интегрированными средствами управления двигателями предназначены для прямого цифрового управления преобразовательными устройствами электроприводов. Кроме рассмотренных выше блоков ОМК, схема содержит дополнительные линии портов и сложный генератор периодических сигналов.

Однокристальный микроконтроллер с интегрированными средствами цифровой обработки имеет традиционную архитектуру, но дополнительно содержит цифровой сигнальный процессор для реализации функции цифрового регулятора. Это позволило:

- повысить производительность ЦП за счет уменьшения времени выборки из памяти программ и данных;

- использовать конвейерный режим с одновременным выполнением четырех команд для уменьшения времени машинного цикла;

- применить аппаратные средства умножения и деления;

- дополнить систему команд специальными командами (умножение с накоплением, повторение, автоматизация обновления данных в таблицах последовательных выборок), оптимизированными для решения задач построения цифровых фильтров и регуляторов.

Микропроцессоры

Структура микропроцессора i8086

Микропроцессор i8086 - это 16-разрядное устройство с быстродействием до 2,5 млн. оп/с и объемом адресуемой памяти 1 Мбайт. Он ориентирован на параллельное выполнение циклов исполнения команд и выборки последующих команд и условно может быть разделен на две части, работающие асинхронно: устройство обработки операндов и устройство обработки команд.

Устройство обработки операндов предназначено для выполнения операций по обработке данных. В функции устройства обработки команд входит: формирование 20-разрядного физического адреса памяти, выборка команд и операндов из памяти, организация очередности команд, запоминание результатов выполнения команд в памяти.

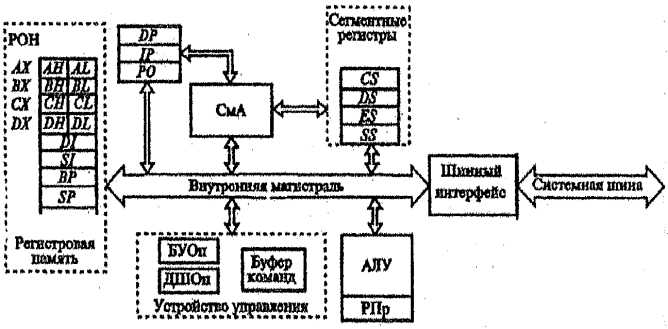

В состав микропроцессора входят следующие блоки и устройства (рис. 15.3):

1) арифметико-логическое устройство (АЛУ);

2) устройство управления, содержащее:

- буфер команд - регистровую память объемом 6 байт, предназначенную для хранения очереди команд (команды, выполняемой в данный момент) и заполняющуюся очередными командами, считываемыми из основной памяти по мере освобождения;

- дешифратор операций (ДшОп);

- блок управления операциями (БУОп), который формирует управляющие сигналы для всех блоков микропроцессора в соответствии с расшифрованным кодом операции;

Рисунок 15.3

3) внутренняя регистровая память, состоящая из восьми регистров общего назначения (РОН), четыре из которых допускают раздельное использование младших и старших разрядов, что позволяет работать как с байтами, так и с 16-разрядными словами;

4) регистр адреса команды (указатель команд IP), в который помещается смещение адреса выполняемой команды относительно базового адреса;

5) регистр адреса данных (указатель данных DP), определяющий смещение адреса данных относительно базового адреса;

6) регистр признаков (РПр), содержащий признаки результата выполненной команды (получение нулевого результата, получение отрицательного результата, наличие переноса из третьего разряда в четвертый или займа из четвертого разряда в третий младшего байта 16-разрядного числа (используется командами десятичной арифметики), наличие переноса из старшего бита числа в знаковый разряд при сложении или вычитании, наличие переполнения, четность числа единиц в коде результата) и дополнительную управляющую информацию;

7) блок из четырех сегментных регистров, содержащих базовые адреса оперативной памяти: кодового сегмента CS, где содержится программа; сегмента данных DS; сегмента стека SS и дополнительного сегмента данных ES;

8) сумматор адреса (СмА);

9) регистр обмена (РО);

10) шинный интерфейс - схемы, обеспечивающие связь внутренней магистрали микропроцессора с системной шиной.

Система команд микропроцессора содержит 135 команд, которые по функциональному назначению делятся на команды передачи данных, арифметические, поразрядной обработки данных, обработки строк данных, передачи управления, управления процессором.

Команды передачи обеспечивают пересылку операнда- источника на место операнда-приемника без содержательного преобразования. Арифметические команды (сложение, вычитание, умножение, деление, преобразование форматов) выполняют операции над 8- и 16-разрядными целыми двоичными числами с фиксированной и плавающей точками и двоично-десятичными числами. Команды поразрядной обработки предназначены для выполнения логических операций булевой алгебры, операции линейных и циклических сдвигов вправо и влево. Команды обработки строк позволяют обрабатывать как числа, так и тексты (длина обрабатываемых строк может достигать 64 Кбайт). Команды передачи управления позволяют осуществлять безусловные переходы, вызовы и возвраты, условные переходы, управление циклами и обслуживание прерываний. Команды управления процессором изменяют состояния определенных разрядов регистров признаков и используются для синхронизации работы с внешними событиями и процессорами.

Система команд - двухадресная, поэтому в ее составе нет команд, в которых оба операнда извлекаются из основной памяти. Допустимы только следующие сочетания: RR, RS, RI, SI (R - регистр регистровой памяти, S - оперативная память, I - операнд, заданный в адресном поле команды). При обращении к регистровой памяти указывается номер регистра; при обращении к основной памяти исполнительный (физический) 20-разрядный адрес формируется путем сложения эффективного адреса с увеличенным в 16 раз содержимым определенного сегментного регистра.

Эффективный адрес может

- быть частью команды;

- находиться в одном из регистров BX, DI, SI;

- быть равен сумме содержимого одного из:

регистров BX, BP, DI, SI и 8- или 16-разрядного смещения;

базовых регистров (BX, BP) и одного из индексных регистров (DI, SI);

базовых регистров (BX, BP), одного из индексных регистров (DI, SI) и 8- или 16-разрядного смещения.

Микропроцессор i80386

Этот микропроцессор стал родоначальником семейства 32-разрядных схем и принятые в нем архитектурные решения до настоящего времени остаются характерными для последующих микропроцессоров фирмы Intel.

Микропроцессор i80386 оптимизирован для многозадачных ОС и для совместной работы пользователей, использующих разные ОС. Эти возможности поддерживаются архитектурой со встроенными устройствами управления памятью и защиты.

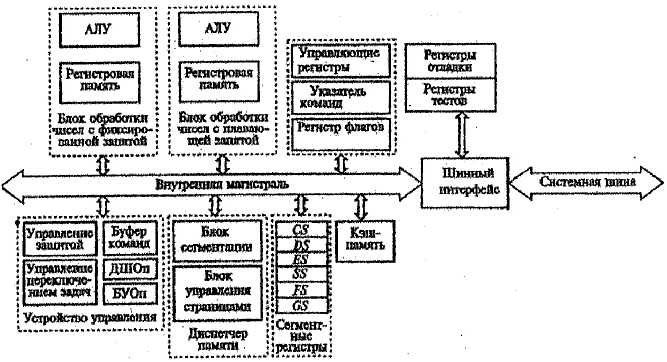

Микропроцессор содержит шесть блоков, реализующих выполнение команд, сегментацию, страничную организацию памяти, сопряжение с шинами, декодирование и упреждающую выборку команд (рис. 15.4). Все эти блоки и устройства работают в режиме конвейера: во время выполнения одной команды декодируется вторая и из памяти выбирается третья. Дополнительным средством повышения производительности служит специальный блок быстрого умножения/деления.

Блоки сегментации и управления страницами позволяют управлять логическим адресным пространством, обеспечивая перемещаемость программ и данных и эффективное распределение памяти между задачами пользователей. Для этого память организована в виде одного или нескольких блоков - сегментов, каждый из которых, в свою очередь, разделяется на одну или несколько страниц.

Рисунок 15.4

Сегмент - это часть адресного пространства переменного размера, которая выделяется программе. Каждый сегмент имеет свой дескриптор (описатель), содержащий базовый адрес сегмента, размер сегмента, тип информации (стек, программа, данные) и поле прав доступа.

В микропроцессоре имеется 32 регистра: регистры общего назначения, сегментные, указатель команд и флаги, управления, системных адресов, отладки, тестов. Эти регистры являются расширением регистров микропроцессора i8086.

В восьми 32-разрядных РОН хранятся адреса и данные, в шести сегментных регистрах - значения селекторов, указывающих адресуемые в данный момент сегменты памяти (один - текущий сегмент программы, один - текущий стековый сегмент, четыре - сегменты данных).

Указатель команд содержит смещение адреса следующей команды относительно базового адреса сегмента, где хранятся коды команд программы. Регистр флагов имеет то же назначение, что и в микропроцессоре i8086.

Внутренняя кэш-память включается между регистрами процессора и оперативной памятью; она хранит наиболее часто используемую информацию (команды и данные). В различных моделях микропроцессоров емкость внутренней кэш-памяти находится в диапазоне от 8 Кбайт до 128 Кбайт.

Контрольные вопросы:

1 Перечислите основные узлы, входящие в структурную схему ОМК с интегрированными устройствами высокоскоростного ввода/вывода.

2 Режимы работы универсальных каналов захвата/сравнения в процессоре событий.

3 Блоки, входящие в состав микропроцессора i8086

4 Система команд микропроцессора i8086

5 Назначение блоков, входящих в состав микропроцессора i8386

Дата: 2019-04-23, просмотров: 412.