Преобразователи параллельного сравнения обладают, в принципе, самым высоким быстродействием. Они построены на основе сетки разрешенных уровней напряжения. Эти напряжения формируются с помощью делителей эталонного напряжения Е. Каждое из опорных напряжений поступает на первые входы 2n-1 схем сравнения, а на все вторые входы этих схем подано входное напряжение Ux.

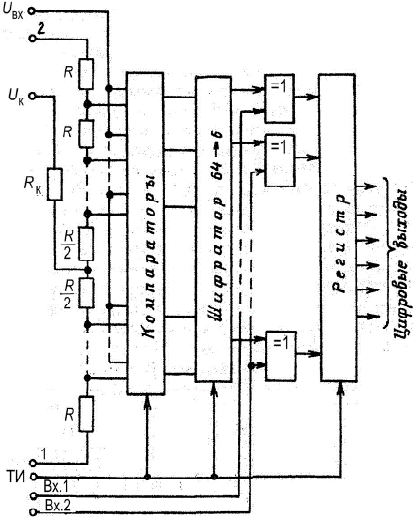

В качестве примера преобразователя такого типа рассмотрим микросхему К1107ПВ1. Функциональная схема этой БИС объединяет делитель опорного напряжения, 64 стробируемых компаратора напряжения КН (А0 - А63), синхронизирующие буферные каскады, логические схемы шифрации и управления, выходной буферный регистр Рг (рис. 11.2).

Рисунок 11.2

Делитель опорного напряжения представляет собой набор низкоомных резисторов с номиналами R=1,04...1,24 Ом. Резисторы образуют шину деления опорного напряжения с двумя самостоятельными выводами 1 и 2. По выводу 1 возможно проведение коррекции напряжения смещения нуля на входе, а по выводу 2 - абсолютной погрешности преобразования в конечной точке шкалы.

Каждый из 64 КН обладает быстродействием порядка 7 нс (типовая задержка) и небольшим коэффициентом усиления. Перепад логических уровней на выходе составляет 200...400 мВ. Управление работой КН, логических элементов, буферного регистра осуществляется от одних и тех же тактовых импульсов ТИ.

Выборка аналогового сигнала производится через 10...22 нс после появления фронта ТИ на соответствующем входе КН. Шифрация сигналов с выходов 64 КН проводится с момента поступления среза ТИ. Результат шифрации, который является также конечным результатом процесса кодирования, записывается в выходной буферный регистр с появлением фронта следующего ТИ. Задержка, вносимая буферным регистром, не превышает наименьшей длительности периода ТИ, равной 50 нс. Это делает возможным производить выборку аналогового сигнала одновременно с появлением на выходе АЦП результата преобразования. В тот момент, когда на выходе микросхемы появляется результат n-й выборки, на входе производится (n+2)-я выборка, то есть имеет место конвейеризация обработки сигналов. Частота преобразования МС типа К1107ПВ1 - до 20 МГц.

Контрольные вопросы:

1 Алгоритм работы преобразователей напряжения в код, построенные по принципу поразрядного кодирования.

2 Разъясните соотношение, которому должен удовлетворять разрядный коэффициент кода аi.

3 Быстодействие преобразователей напряжения в код, построенные по принципу параллельного сравнения.

4 Функциональная схема БИС в качестве примера преобразователя, построенного по принципу параллельного сравнения.

Лекция 12 Основные направления совершенствования схем и принципов преобразования. Основные характеристики преобразователей

Основные направления совершенствования схем и принципов преобразования

Среди современных АЦП все реже можно найти схемы, построенные «традиционным» способом (параллельные, последовательных приближений, интегрирующие). Для обеспечения лучших параметров (быстродействие, разрешающая способность) используются комбинированные структуры.

Практически все АЦП имеют последовательно-параллельную структуру со схемой выборки-хранения на входе и работают по принципу постоянного опроса, когда преобразование сигнала происходит постоянно с максимальной скоростью.

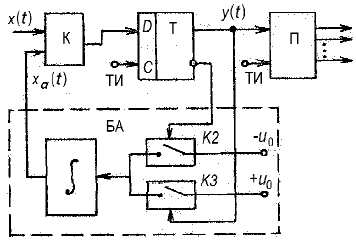

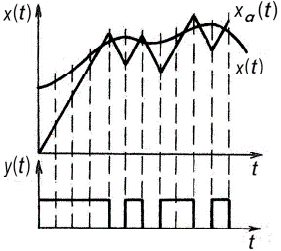

Это обеспечивается, в частности, применением дельта-модуляции. Преобразователь, реализующий этот принцип, состоит из компаратора и квантователя К в основном тракте обработки сигнала и из интегрирующего усилителя в цепи обратной связи (рис. 12.1, а). Алгоритм работы такого преобразователя поясняется рис. 12.1, б.

а) б)

Рисунок 12.1

Входной сигнал x(t) сравнивается с выходным сигналом xa(t) блока аппроксимации, выполненном на интегрирующем усилителе. На выходе компаратора формируется логический сигнал, соответствующий знаку разности между текущим и аппроксимированным значениями сигнала. Он определяет знак величины опорного напряжения u0, подаваемого на вход интегратора, и, следовательно, управляет изменением напряжения на его выходе.

Выходной сигнал дельта-модулятора - последовательность значений логических сигналов 1 и 0. Она должна быть преобразована в параллельный двоичный код. Это можно сделать с помощью реверсивного счетчика, который выполняет операцию сложения при поступлении 1 и вычитания при поступлении 0.

Данному преобразователю свойственна динамическая погрешность, возникающая в случае, когда скорость изменения входного сигнала превышает скорость изменения напряжения на выходе интегратора. Определяющими параметрами при этом служат частота тактовых импульсов и величина u0.

Развитием этого принципа являются алгоритмы адаптивной дельта-модуляции.

Вариант параллельно-последовательной структуры преобразователя можно представить следующим образом. Входное напряжение подается одновременно на вход АЦП1 и на один из входов усилителя. АЦП1 выполняет грубое кодирование входного сигнала, формируя старшие разряды выходного кода. Выходы АЦП1 поступают на входы ЦАП, который формирует соответствующее напряжение. Это напряжение подается на инвертирующий вход усилителя. Усиленная разность входного сигнала и этого напряжения, представляющая собой погрешность квантования АЦП1, после фиксации кода и окончания переходных процессов в аналоговых цепях преобразуется с помощью АЦП2, выходной код которого объединяется с выходным кодом АЦП1.

Большинство АЦП имеет встроенный источник опорного напряжения и работает от одного источника питания (обычно 5 В).

Современные ЦАП характеризуются снижением энергопотребления и тенденцией к снижению стоимости. В связи с этим расширяется сфера применения ЦАП: в частности, они используются 122 вместо переменных и подстроечных резисторов. Для такого рода приложений достаточно иметь точность 8...10 разрядов и среднее быстродействие. Так, например, ЦАП типа AD8802/04 фирмы Analog Device, область применения которого - электронная подстройка (замена потенциометров), имеет 8 разрядов при 12 каналах установки с временем 0,6 мкс. Он потребляет мощность 55 мВт, работает от источника 3 В и имеет последовательный интерфейс для связи с системой.

Дата: 2019-04-23, просмотров: 400.