| Наименование звена | Уравнение звена y(t)=f(u(t)) | Передаточная функция W(s)=y(s)/u(s) | Элементарные составляющие |

| Пропорциональное | y(t)=ku(t) | Wп(s)=k | Нет |

| Интегрирующее | dy(t)/dt = ku(t); py = ku | Wи(s)=k/s | Нет |

| Дифференцирующее | y(t)=k·du(t)/dt; y = kpu | Wд(s)=ks | Нет |

| Апериодическое 1 -го порядка | (Tp+1)y = ku | W(s)=k/(Ts+1) |

|

| Форсирующее 1 -го порядка | У = k(Tp+1) | W(s)=k(Ts+1) |

|

| Интегрирующее инерционное | p(Tp+1)y = ku | W(s) = k/[s(Ts+1)] |

|

| Дифференцирующее инерционное | (Tp+1)y = kpu | W(s) = ks/(Ts+1) |

|

| Изодромное | py = k(Tp+1)u | W(s) = k(Ts+1)/s |

|

| Колебательное, консервативное, апериодическое 2-го порядка | (T2p2+2ξTp+1)y = ku | W(s)=k/(T2p2+2ξTp+1) |

|

Заметим, что если для функциональной схемы система разбивается на звенья исходя из выполняемых ими функций, то для математического описания систему фрагментируют исходя из удобства получения описания. Поэтому звенья должны быть как можно более простые (мелкие). С другой стороны, при разбиении системы на звенья математическое описание каждого звена должно быть составлено без учета связей его с другими звеньями. Это возможно, если звенья обладают направленностью действия - т.е. передают воздействие только в одном направлении, с входа на выход. Тогда изменение состояния какого-либо звена не влияет на состояние предшествующего звена.

Если условие направленности действия звеньев выполнено, математическое описание всей системы можно получить в виде системы независимых уравнений отдельных звеньев, дополненных уравнениями связи между ними. Наиболее часто встречающимися (типовыми) считаются такие звенья, как апериодическое, колебательное, интегрирующее, дифференцирующее, звено постоянного запаздывания.

Проблема элементарных звеньев в моделях вида системы дифференциальных уравнений исследовалась рядом авторов. Анализ показывает, что их позиции в основном сводятся к констатации факта существования типовых звеньев и исследования их роли в процессе образования более сложных структур. Отбор в группу типовых звеньев производится произвольно, без каких-либо критериев. В перечни типовых без объяснения и обоснования включаются разные звенья, а для обозначения типовых звеньев в равной мере используются также термины "простейшие" и "элементарные" (см. таблицу). Между тем, исследование многочисленных "типовых" звеньев динамических систем методами структурных матриц показывает, что лишь три звена - пропорциональное, интегрирующее и дифференцирующее - в своих структурных матрицах не содержат матричных циклов. Поэтому только их можно называть элементарными. Все остальные звенья строятся путем комбинации элементарных звеньев.

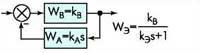

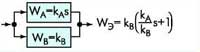

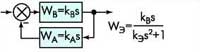

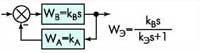

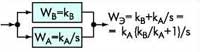

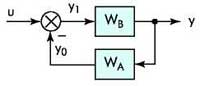

Так, если пропорциональное звено с передаточной функцией WB(s) = kB и дифференцирующее звено с передаточной функцией WA(s) = kAs соединить по схеме отрицательной обратной связи (рис.3), то эквивалентная передаточная функция

Таким образом, результат с точностью до значений постоянных времени совпадает с передаточной функцией апериодического звена первого порядка. Значит, это звено можно получить соединив пропорциональное и дифференцирующее звенья по схеме с отрицательной обратной связью и, следовательно, оно не может считаться элементарным.

Рисунок 16.3 - Эквивалентная, схема апериодического звена

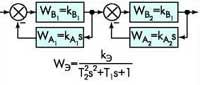

Точно так же можно построить и остальные звенья, включенные в таблицу. Особо следует остановиться на передаточной функции колебательного звена (T2p2 + 2ξTp + 1 )y = ku. Так, если соединить последовательно два апериодических звена с передаточными функциями отличающимися лишь постоянными времени, то эквивалентная передаточная функция примет вид

Таким образом, результат с точностью до значений постоянных времени совпадает с передаточной функцией исследуемого звена. Следовательно, колебательное, консервативное и апериодическое звенья 2-го порядка можно получить путем последовательного соединения звеньев первого порядка. Значит, они не могут считаться элементарными, хотя называть их типовыми в принципе допустимо.

Анализ результатов, приведенных в последнем столбце таблицы, позволяет сделать вывод о том, что такие звенья, как апериодическое, изодромное, форсирующее, дифференцирующее инерционное и интегрирующее инерционное, могут быть получены соединением элементарных звеньев. Чтобы доказать, что передаточные функции и остальных типовых звеньев могут быть получены путем соединения элементарных звеньев, следовало бы проанализировать соединения по три, четыре и так далее звеньев по типовым схемам соединения. Такой же результат можно получить, если рассмотреть соединения элементарных звеньев с типовыми звеньями первого порядка.

Таким образом, доказано, что посредством соединения элементарных звеньев достаточно просто получить все передаточные функции так называемых типовых динамических звеньев. Следовательно, произвольные динамические системы могут быть синтезированы с помощью операторов размножения и соединения всего трех элементарных звеньев: пропорционального, дифференцирующего и интегрирующего. Этот вывод имеет фундаментальное значение, так как он определяет элементный базис, необходимый для построения линейных динамических систем любого порядка, в том числе - радиоэлектронных схем. И если динамические системы предполагается строить из ограниченной номенклатуры динамических звеньев, как в случае МАБИС и ПАИС, то сделанный вывод важен особенно.

Рисунок 16.4. - Простые схемные решения элементарных узлов: а) много-входовой сумматор, б) дифференциальный усилитель (пропорциональное звено), в) дифференциатор (дифференцирующее звено), г) интегратор (интегрирующее звено)

Появляется возможность синтеза произвольных аналоговых устройств всего из пяти функциональных узлов - мультиплексора, сумматора, умножителя, интегратора и дифференциатора (рис.4)! Заметим, что приведенные на рис. 4 схемы не следует воспринимать как реально отработанные схемотехнические решения, а только лишь как обоснование возможности замены элементарных звеньев на функциональной схеме базовыми радиоэлектронными элементами. Заменяя элементарные звенья функциональных схем их аппаратными аналогами, можно проектировать аналоговые устройства с заданными характеристиками.

Пример синтеза аналогового устройства

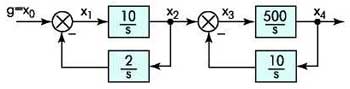

Рассмотрим весьма простой пример синтеза принципиальной схемы аналогового устройства по модели, заданной системой дифференциальных уравнений в форме преобразований Лапласа вида: x0 = g, x1 = x0 - 2x2/s, x2 = 10x1/s, x3 = x2 - 10x4/s, x4 = 500x3/s.

| x1 | x2 | x3 | x4 | x5 |

| 1 |

| 1 | ||

| 10/s |  1 1

| |||

| 1 | 1 |

| ||

| 500/s |

|

Построим структурную матрицу этой системы дифференциальных уравнений и выделим стрелками матричные циклы:

По уравнениям и структурной матрице восстановим блок-схему устройства (рис.5). В соответствии со структурной матрицей система обладает двумя отрицательными обратными связями: узел 2 —> узел1 и узел 4 —> узел 3, соответственно. Поскольку структурная схема на рис.5 изначально построена на элементарных звеньях, ее можно рассматривать как функциональную схему электронного устройства.

Рисунок 16.5 - Структурная схема синтезируемого устройства (поэтапно)

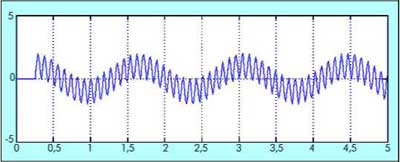

Из результатов моделирования (рис.6) синтезированной схемы видно, что при заданных параметрах она представляет собой два последовательно соединенных генератора. То есть весьма простое устройство, состоящее всего из четырех интегрирующих звеньев, выполняет сравнительно сложную функцию модуляции низкочастотного колебания высокочастотным.

Отметим, что при проектировании и производстве МАБИС и ПА-ИС совершенно не обязательно использовать аппаратные аналоги элементарных звеньев, выполненные на операционных усилителях, как на рис.4, хотя в этом базисе они лучше всего проработаны. Наиболее перспективна реализация аппаратных аналогов элементарных звеньев на оптоэлектронных компонентах, хотя возможны и любые другие варианты.

Рисунок 16.6 - Осциллограмма синтезированного устройства

Универсальные МАБИС и ПАИС

Таким образом, можно выделить пять элементарных (простейших) компонентов любой РЭА, соответствующих основным операторам систем дифференциальных уравнений: умножения, дифференцирования, интегрирования, сложения и размножения (мультиплексирования). Методика проектирования аналоговых электронных устройств предполагает:

• использование в качестве исходных данных для проектирования математической модели в виде системы из n дифференциальных уравнений первого порядка (или дифференциального уравнения л-го порядка;

• построение структурной матрицы проектируемого устройства и нахождение матричных циклов;

• восстановление структурной схемы проектируемого устройства;

• преобразование структурной схемы в функциональную путем замены типовых звеньев совокупностью элементарных звеньев;

• преобразование функциональной схемы проектируемого устройства в схему электрическую принципиальную путем замены элементарных звеньев эквивалентными им аппаратными базисными элементами (возможно, применение современных САПР позволит избежать этот этап, синтезируя топологию непосредственно из функционального описания);

• разработка топологии проектируемого устройства.

Предлагаемый подход обладает рядом решающих преимуществ. Так, функциональная схема проектируемого устройства синтезируется из исходной системы дифференциальных уравнений путем стандартных матричных преобразований, которые могут быть упорядочены и преобразованы в алгоритм для автоматических вычислений. Схема электрическая принципиальная синтезируется из функциональной схемы простой заменой элементарных динамических звеньев эквивалентными им базисными элементами. Также существенно может упроститься моделирование устройства средствами САПР.

Таким образом, поскольку множество элементарных звеньев не многочисленно, появляется реальная возможность проектирования универсальных МАБИС и ПАИС. Что, в свою очередь, значительно упрощает проектирование аналоговых и цифроаналоговых устройств и открывает заманчивые перспективы дальнейшего развития электроники в целом.

Лекция № 17

ТЕМА: Применение современных средств САПР для ПЛИС. Единый базис проектирования ПЛИС и МАБИС.

Основные вопросы, рассматриваемые на лекции:

1. Применение современных средств САПР для ПЛИС

2. Единый базис проектирования ПЛИС и МАБИС

3. Основные производители САПР для ПЛИС

4. Разновидности САПР для ПЛИС

На современном уровне развития ПЛИС проектирование цифровых устройств в данном базисе трудно себе представить без применения средств САПР. При этом как САПР ПЛИС, так и любые другие САПР имеют ряд особенностей, выделяющие их из ряда прочих программных продуктов:

объем систем проектирования (миллионы строк исходного кода на языках высокого уровня);

наукоемкость программных продуктов. Предметными областями САПР, как правило, являются интенсивно развивающиеся отрасли науки и техники. При этом программное обеспечение выступает как инструмент исследования предметной области;

длительность сроков разработки программного обеспечения. Сроки разработки, эксплуатации и модернизации отдельных продуктов составляют десятки лет.

При этом надо отметить - программное обеспечение8 применяемое при разработке цифровых устройств, быстро морально устаревает вследствие

высоких темпов развития элементной базы, результатом чего является необходимость его модернизации. Данное утверждение полностью правомерно и но отношению к САПР ПЛИС Так, на данный момент, в современных коммерческих САПР ПЛИС хорошо отработаны методы получения конфигурации ПЛИС по моделям устройств на уровне регистровых передач. Однако современные устройства ПЛИС обладают такой логической емкостью, что позволяют проектировать целые системы на. одном кристалле, и соответственно для проектирования систем необходимо применять средства проектирования на системном уровне. В настоящее время нет однозначной, удовлетворяющей всех разработчиков аппаратуры. методологии получения конфигурации ПЛИС по функциональной модели устройства на системном уровне.

Наиболее популярным подходом по решению данной проблемы является применение технологии ІР-ядср (Intellectual property - Cores). IP-ядра - это готовые компоненты, позволяющие легко включать их в собственный проект для создания более сложной системы, У данного подхода есть один существенный недостаток - привязанность ІР-ядср к элементному базису. Каждое IP-ядро оптимизировано под конкретную серию микросхем конкретного производителя, что существенно ухудшает возможность переноса уже созданных устройств из одного элементного базиса в другой[33,90].

Закрытость архитектур коммерческих САПР делает невозможным добавление собственных функциональных моделей устройств на системном уровне для получения на их основе моделей усіройства на уровне регистровых передач.

Другой популярный подход, позволяющий осуществить переход от

функциональной модели на системном уровне к модели устройства на уровне

регистровых передач — применение языков описания аппаратуры на системном

уровне (SLDLs, system-level design languages). К таким языкам относятся

SystemC,. Handel-C, Open Vera- Основным недостатком данного подхода

является ограниченность групп алгоритмов, которые возможно применять для осуществления данного перехода, следствием чего является снижение качества получаемого решения (по сравнению с технологией IP-ядер). Однако его несомненным плюсом является независимость от аппаратного базиса, в котором будет ре&іизовано устройство.

Таким образом, с одной стороны, при применении технологии 1Р-ядер разработчик аппаратуры получает качественное решение, но жестко привязанное к аппаратному базису, в котором реализуется усіройство. С другой стороны, при применении языков описания аппаратуры на системном уровне реализация устройства является аппаратно независимой, но при этом теряется качество получаемого решения (в сравнении с технологией ІР-ядер). Из выше сказанного следует, что в настоящее время актуальным является решение задачи автоматизации перехода. от функциональной модели устройства на системном уровне к его модели па уровне регистровых передач и создание подсистемы, САПР, открытой по отношению к модернизации и расширению, позволяющей решать данную задачу.

днако в настоящий момент у большинства разработчиков систем САПР хорошо отработан процесс получения конфигурации устройства по его описанию на уровне регистровых передач, но до сих. пор разработчики аппаратуры сталкиваются с рядом проблем при попытке получить описание. устройства на уровне регистровых передач на основании его функциональной модели на системном уровне.

Далее рассмотрим коммерческие САПР цифровых устройств и методы получения описания устройства на уровне регистровых передач по его функциональной модели на системном уровне. При этом акцентируем свое внимание на том, как в этих системах при разработке устройства в базисе ПЛИС решается проблема перехода от функциональной моделей устройства на системном уровне к его модели на уровне регистровых передач.

САПР "MAX+PLUSir фирмы ALTERA поддерживает цикл проектирования ПЛИС для кристаллов этой же фирмы, однако только лишь для проектов, в которых проектируемое устройство описано на уровне регистровых передач. Эта система работает на PC платформе и рабочих станциях. САПР предоставляет разнообразные средства входного описания,, включая интерфейсы со стандартными языками и наиболее распространенными пакетами и обеспечивая эффективные алгоритмы синтеза, позволяющие максимально использовать ресурсы кристалла, временной и функциональный анализ разработанного устройства. Используется для проектирования микросхем всех семейств фирмы, таких, как MAX70G0, MAX900G, FLEX8000, FLEX10K.

MAX+PLUSII ориентирован на сопряжение со стандартами VHDL, EDIF, Verilog. Любая конфигурация САПР импортирует входные данные в формате EDIF и формирует результаты проектирования во всех перечисленных форматах. ALTERA обеспечивает библиотеками САПР таких фирм, как Mentor Graphics, Cadence, Viewlogic и Synopsys. Имеются библиотеки IP-ядер.

Последняя версия 10.0 MAX+PLUS II реализуется с октября 2000г. С октября 2000г. фирма выпустила новый программный продукт "Quartus". Данный пакет ориентирован на самые мощные новые кристаллы фирмы семейства APEX, Stratix и обладает всеми" чертами, присущими MAX+PLUSII.

Фирма Xilinx — разработчик ПЛИС - поставляет также САПР для разработки устройств на FPGA и CPLD. С 1996г. Xilinx выпустила ПО Foundation Series, охватывающее все этапы разработки ПЛИС. В новых версиях ПО поддерживаются расширенные библиотеки IP-ядер, которые становятся очень важными при создании проектов больших размеров, сокращают сроки и упрощают проектирование. Имеются UNISIM-библиотеки для функционального моделирования с VHDL и Verilog, также в САПР фирмы включен набор библиотек для временного моделирования,

В настоящее время Xilinx выпустила свою последнюю версию Foundation Series 4.2І. Эта САПР позволяет в два раза сократить время компиляции проекта, появились новые средства трассировки и размещения, включена новая версия программы синтеза Express 3.6. На данный момент Foundation Series больше не развивается в связи с чем, что фирма Xilinx порвала отношения с производителем программы синтеза фирмой Synopsys. Поэтому рекомендуется для новых разработок применять новую САПР ISE[I5,82] Эта САПР позволяет выполнять полный маршрут проектирования для новых кристаллов фирмы: это наиболее мощные и быстрые кристаллы семейства Virtcx-11, Viriex-11 Pro, дешевые кристаллы семейства Spartan-II, Spartan-III и кристаллы с малым потреблением CoolRimner. Кроме того, данная САПР поддерживает интеграцию с системами Synplify, LeonardoSpectrum и Modelsim. Так же в настоящее время фирма ХІІІпх выдвинула на рынок свой новый продукт -Embedded Development Kit, предназначенный для построения систем на основе их функциональных моделей на системном уровне. Данный продукт при реализации систем в кристалле опирается на библиотеки ІР-ядер. А также позволяет создавать проекты, содержащие одновременно как описание аппаратуры, так и программную часть. В настоящее время это становится актуально в связи с выходом новой серии кристаллов Virtex-II Pro, содержащих интегрированные процессорные ядра. Так же для перехода от функциональных моделей на системном уровне к реализации в кристалле, фирма Xiliiix предлагает библиотеку расширения для MatLab. В данном подходе реализация в кристалле получается при помощи применения библиотеки ІР-ядер.

Фирмой Xilinx совместно с фирмой ELANIX разработан новый подход к проектированию устройств обработки сигналов - на основе комбинации САПР системного уровня System View фирмы ELANIX с ІР-ядрами, оптимизированными для эффективной реализации в ПЛИС Xilinx. Таким образом, цифровое устройство может быть моделировано, оптимизировано и реализовано в ПЛИС с помощью библиотек ІР-ядер.

То есть можно сделать вывод, что в САПР фирмы Xilinx для осуществления перехода от функциональных моделей па системном уровне к моделям на уровне регистровых передач доминирует подход на основе ІР-ядер. Фирма CADENCE, многие годы занимающаяся разработкой САПР в области электроники, расширяется за счег приобретения множества более мелких компаний; годовой объем продаж достиг 1.3 млрд. долларов в 2003г. Основные направления развития связаны со следующими базовыми конфигурациями системы: — проектирование на системном уровне (system-level design); — функциональная верификация (functional verification); — эмулляция и ускорители решений (emulation and acceleration); — средства синтеза от верхних уровней до размещения и трассировки (synthesis/piace-and-route); — средства проектирования аналоговых, высокочастотных и смешанных схем (analog, radio frequency, and mixed-signal design); — проектирование топологии интегральных схем (custom 1С layout); — анализ и верификация на физическом уровне (physical verification and analysis); — проектирование и корпусирование микросхем (1С packaging); — проектирование печатных плат (РСВ design). Основные системы CADENCE для решения задач по направлениям: Virtuoso Custom Designer - это набор средств САПР для проектирования заказных ИС. Это полностью автоматизированный процесс проектирования на уровне приборов и ячеек, включая средства верификации, размещения и трассировки, CADENCE SP&R - это система сквозного синтеза от регистрового уровня или уровня затворов до формирования GDSII-файла после реализации размещения и трассировки на основе синтеза, CADENCE AMS Designer реализует маршрут проектирования эффективного решения задач проектирования систем на кристалле, в том числе и для смешанных аналого-цифровых систем. CADENCE Wireless Solution содержит высоко интегрированный набор программ, который поддерживает быстрое проектирование от концепции решения до реализации в микросхемах. Система обеспечена большим числом библиотек всех основных мировых стандартов, включая 3GPP, CDMA2000, Bluetooth, 802.11 и др. Signal Processing Worksystcm позволяет ускорить процесс проектирования сложных алгоритмически цифровых сигнальных процессоров. SPW поддерживается большим набором библиотек и позволяет от алгоритмического уровня перейти к реализации в ASIC или FPGA, NC-SIM - это один из самых быстрых пакетов моделирования на основе языков описания аппаратуры Verilog и VHDL. Основное его преимущество — это работа одновременно с двумя стандартными языками.

Как было показало выше, основным узким местом в маршруте проектирования цифровых устройств е базисе ПЛИС является переход от разряботанной функциональной модели устройства на системном уровне к его модели на уровне регистровых передач (оптимизированной для заданного элементного базиса).

На сегодняшний день наиболее развитым подходом, покрывающим данный этап, является проектирование устройств и систем на основе ІР-ядер. ІР-ядра - это готовые компоненты, позволяющие легко включать их в собственный проект для создания более сложной системы. Например, ІР-ядром может быть интерфейс соединения с компьютером РСІ или USB, быстрое преобразование Фурье, голосовой кодек. Этот подход реатизован практически во всех современных системах САПР, Основным недостатком данного подхода является привязанность ядер к конкретным семействам кристаллов, т.е. при необходимости смены аппаратного базиса возникает необходимость в получении новых IP-ядер оптимизированных под него. К тому же никто не гарантирует, что IP-ядра, реализующие те же самые функции для новой элементной базы, будут сохранять свои старые интерфейсы, т.е,. встает проблема повторного связывания набора IP-ядер оптимизированного под новую элементную базу.

Так же в настоящее время ведутся активные разработки по получению описания схемы на уровне регистровых передач, исходя из ее описания на таких языках, как SystemC, Handel-C и др.» которые относят к семейству SLDL (system-level design languages), т.е. на языках поведенческого описания приближенных к аппаратным. Здесь лидирующие позиции занимает фирма SYNOPSYS. Однако набор алгоритмов, которые возможно перевести с SLDL языков на уровень регистровых передач, ограничен следующими правилами: 1. В программе может использоваться любое число простых переменных и переменных с индексами. 2. Единственным типом исполнительного оператора может быть оператор присваивания, правая часть которого есть арифметическое выражение; допускается любое число таких операторов. 3. Все повторяющиеся операции описываются только с помощью цикла с указанием границ изменения параметра; структура вложенности циклов может быть произвольной; шаги изменения параметров циклов всегда равны +1; если у цикла нижняя граница больше верхней, то цикл не выполняется.. 4. Допускается использование любого числа условных и безусловных операторов перехода, передающих управление «вниз» по тексту; не допускается использование побочных выходов из циклов. 5. Все индексные выражения переменных, границы изменения параметров и условия передачи управления задаются в общем случае, неоднородными формами, линейными как по параметрам циклов, так и по внешним переменным программы; все коэффициенты лилейных форм являются целыми числами. 6. Внешние переменные программы всегда целочисленные, и вектора их значений принадлежат некоторым целочисленным многоіранникам; конкретные значения внешних переменных известны только перед началом работы программы и неизвестны в момент её исследования.

Уместно сделать одно замечание относительно терминологии. Обычно под переменной с индексами понимается весь массив простых переменных, объединённых общим идентификатором. При изучении тонкой структуры программы такая «групповая» переменная очень неудобна. Гораздо удобнее рассматривать массив как группу простых переменных, идентификаторы которых составлены из идентификатора массива и индексов. Таким образом, работа с массивом сводится к работе с группой нумерованных переменных. Что резко сужает возможность применения данных методов из за снижения качества получаемого решения.

С другой стороны, разрабатываемое устройство мы можем представить в виде множества простейших компонентов, являющихся аппаратно зависимыми (регистры, очереди, сумматоры и т.д и построенных на их основе более сложных компонентов (фильтр, кодер, декодер и т.д.). Такое разбиение устройства правомерно, т.к. из алгебры логики известно, что в случае если множество простейших компонентов является функционально полной системой, то через его элементы можно выразить любую логическую функцию.

В случае, если разрабатываемое устройство строится на основе данного множества, мы получаем, что только лишь компоненты в него входящие являются зависимыми от конкретного базиса, в котором будет реализовано данное устройство. Описание самого устройства опирается уже на данное множество примитивов, что делает его независимым от базиса, в котором оно будет реализовано. Так же на основе данного множества можно реализовывать и аппаратно независимые IP ядра независимых примитивов В случае смены аппаратного базиса достаточно перенести в него множество аппаратно зависимых примитивов, при этом не трогая описания всего устройства в целом, что дает существенный выигрыш данного подхода по сравнению с двумя предыдущими. Так получаемое в данном случае решение по качеству эквивалентно решению, получаемому при применении технологии IP-ядер, при одновременной простоте переноса разработанного устройства из одного элементного базиса в другой.

В настоящее время данный подход не нашел применения в коммерческих системах САПР, но был применен при построении некоммерческих систем: так профессор Christoph Wolinski из Los Alamos National Laboratory применил данное представление устройства для построения автоматизированной системы проецирования реконфигурируемых вычислителей.

В качестве входного языка системы был выбран Java. Описание внутренней структуры проектируемого устройства производилось в виде набора Java объектов, а связи между объектами устанавливались посредством вызова соответствующих методов объектов. То есть для работы с данной системой от конечного пользователя необходимо знание Java и соответственно умение программировать на нем. Так же, как показало более детальное рассмотрение данной методологии, описание схемы оказывается очень громоздким, так как необходимо прописать каждую связь между внутренними объектами проектируемого устройства. Однако было бы логичней указывать узлы подключения каждого объекта, входящего в состав устройства,. что существенно сократило бы его входное описание в связи с тем, что обычно количество узлов в схеме существенно меньше количества связей между ее отдельными элементами (в худшем случае количество связей и узлов в схеме равны). С этой точки зрения наиболее удобным является описание устройства на SPICE подобном языке.

Как известно, качество получаемого решения при реализации устройства в ПЛИС можно определить по следующим критериям: площадь, занимаемая в кристалле, максимальная частота функционирования, время, затраченное на разработку.

Таблица 17.1

САПР фирм – производителей кристаллов ПЛИС

Таблица 17.2

Общецелевые САПР независимых разработчиков

Дата: 2019-03-05, просмотров: 505.

-(2/s)

-(2/s)