Все модели МК AVR (кроме снятого с производства ATtinyl 1) имеют встроенную EEPROM для хранения констант и данных при отключении питания. В разных моделях объем ее варьируется от 64 байт (ATtinylх) до 4 кбайт (старшие модели Mega). Число циклрв перепрограммирования EEPROM может достигать 100 тыс.

Напомним, что EEPROM отличается от flash-памяти возможностью выборочного программирования побайтно (в принципе, даже побитно, но эта возможность скрыта от пользователя). Чтение из EEPROM осуществляется с такой же скоростью, как и чтение из РОН — в течение одного машинного цикла (правда, на практике оно растягивается на 4 цикла, но программисту следить за этим специально не требуется). А вот запись в EEPROM протекает значительно медленнее, и к тому же с не точно определенной скоростью: цикл записи одного байта может занимать от 2 до 4 и более миллисекунд. Процесс записи регулируется встроенным RC-генератором, частота которого нестабильна (при низком напряжении питания можно ожидать, что время записи будет больше). За такое время при обычных тактовых частотах МК успевает выполнить несколь^со тысяч команд, потому программирование процедуры записи требует аккуратности: например, нужно следить, чтобы в момент записи не «вклинилось» прерывание.

Микросхемы Tiny имеют Flash-ПЗУ программ объемом 1-8 кбайт и размещаются в основном в корпусах с 8-20 выводами (кроме ATtiny28), т. е. они в целом предназначены для более простых и дешевых устройств. Это не значит, что их возможности во всех случаях более ограниченны, чем у семейства Mega. Так, например, ATtiny26 при цене менее 2 долларов содержит таймер с высокоскоростным ШИМ-режимом (в других моделях такого нет), а также 11-канальный АЦП с возможностью работы в дифференциальном режиме, с регулируемым входным усилителем и встроенным источником опорного напряжения, что характерно для старших моделей. Микросхема ATtiny2313, как уже говорилось, представляет собой улучшенную версию одного из наиболее универсальных и удобных "классических" AVR AT90S2313. Подсемейство Mega оснащено Flash-ПЗУ программ объемом 8-256 кбайт и корпусами с 28-100 выводами. В целом МК этой группы более "навороченные", чем Tiny, имеют более разветвленную систему встроенных устройств с более развитой функциональностью. Кроме этих трех семейств, на базе AVR-ядра выпускаются специализированные микросхемы для работы с USB-интерфейсом (AT90USBxxxx), промышленным интерфейсом CAN (AT90CANXJCJC), для управления ЖК-дисплеями (ATmega329 и др.), с беспроводным интерфейсом IEEE 802.15.4 (ZigBee) для предприятий торговли и некоторые другие. В последнее время некоторые микроконтроллеры серий Tiny и Mega стали выпускаться в версиях со сверхмалым потреблением (технология picoPower с напряжением питания от 1,8 В, в конце наименования МК этой серии добавлена буква "Р") и высокотемпературных для использования в автомобильной промышленности (версии Automotive). Появилось семейство XMega с напряжением питания 1,8-3,6 В, повышенным быстродействием (тактовая частота до 32 МГц), 12-разрядным 16-канальным АЦП и 2-4 каналами ЦАП (до сих пор в структуре AVR они отсутствовали), несколькими каналами UART и других последовательных портов (причем с возможностью работы в автономном режиме, при остановленном ядре), встроенной поддержкой криптографии, усовершенствованным режимом picoPower и другими "наворотами". Существует также отдельное семейство 32-разрядных МК AVR32, предназначенное для высокоскоростных приложений, таких как обработка видеопотока или распознавание образов в реальном времени.

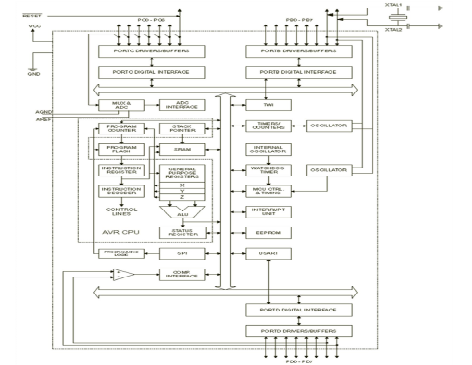

Архитектура микроконтроллера ATmega8

ATmega8 – 8-разрядный КМОП микроконтроллер, основанный на

архитектуре AVR фирмы Atmel (Принстонская система архитектуры).

Контроллер выполняет большинство инструкций за 1 такт, поэтому

вычислительная мощность контроллера равна 1MIPS (миллиону операций в секунду) на 1 МГц. Микроконтроллер имеет RISC-архитектуру, но формат команды двухоперандный, за один такт может быть обращение только к двум регистрам.

На рис. 11.3 изображена архитектура микроконтроллера ATmega8.

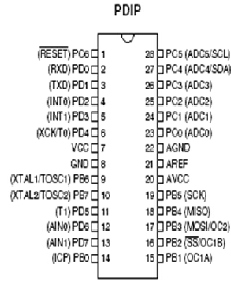

На рис. 11.4 изображен сам микроконтроллер (вид сверху) с номерами ножек и функциональным назначением этих ножек.

Рисунок 11.3 - Архитектура микроконтроллера ATmega8

Из рис.11.3 видно, что некоторые ножки микроконтроллера несут на себе

двойную и даже тройную функцию. Цель такого совмещения – это

сэкономить число ножек микроконтроллера, т.е. уменьшить габариты

Рисунок 11.3 - Архитектура микроконтроллера ATmega8

Из рис.11.3 видно, что некоторые ножки микроконтроллера несут на себе

двойную и даже тройную функцию. Цель такого совмещения – это

сэкономить число ножек микроконтроллера, т.е. уменьшить габариты

микроконтроллера, т.к. не все функции микроконтроллера используются одновременно. Пример, если учитывать схему подключения внешнего генератора импульсов, которую можно заменить конденсатором, а также, что это схема для передачи постоянного сигнала – не помеха, то эти ножки можно использовать для ввода или вывода постоянных сигналов. Еще пример, можно запретить микроконтроллеру использовать сигнал Reset (ножка 1). Тогда эту ножку можно использовать для

ввода или вывода информации в микроконтроллер. Правда после такой операции невозможно будет перезаписать программу в микроконтроллере, т.к. чтобы выполнить эту операцию необходимо подать сигнал Reset.

а) PC6 (Reset) – сигнал сброса по прихода нулевого уровня (нуля вольт),

Это инверсный сигнал сброса, т.е. Reset происходит при появлении нуля

вольт на входе, а не 5В, одновременно является 6 битом порта С.

б) Ножки PD0 (RXD), PD1 (TXD) – необходимы для связи

микроконтроллера с другими устройствами по последовательному

интерфейсу UART. А также, одновременно, эти ножки являются 0 и 1 битом порта D. Ножка TXD – это выход передатчика UART. Если разрешена работа передатчика UART, независимо от состояния бита 1 в регистре DDRD (регистр направления передачи информации) этот вывод сконфигурирован как выход. Ножка RXD – выход приемника UART. Если разрешена работа приемника UART, независимо от состояния 0 бита в регистре DDRD (регистр направления передачи информации) этот вывод сконфигурирован как выход.

в) PD2 (INT0) и PD3 (INT1) – это входы внешних прерываний INT0 и INT1, а также 2 и 3 бит порта D.

г) PD4 (ХСК/T0) – это счетный вход таймера/счетчика 0, если он настроен

как счетчик, а также эта ножка является 4 битом порта D.

д) VСС – питание микроконтроллера. Сюда подается сигнал в 5В. Т.к. без

питания микроконтроллер вообще не работоспособный, то эту ножку не

совместили больше ни с какими функциями.

е) GND – общий провод.

ж) PB6 (XTAL1/TOSC1), PB7 (XTAL2/TOSC2) – ножки подключения

внешнего генератора. Одновременно эти ножки являются входами

выходами порта В.

и) PD5 (T1) – вход таймера/счетчика 1, если он настроен на счет

импульсов, т.е. как счетчик. Одновременно – это ножка 5 порта D.

к) PD6 (AIN0) и PD7 (AIN1) – входа аналогового компаратора и

одновременно 6 и 7 бит порта D.

л) PB0 (ICP) – ножка бита 0 порта В. ICP – вход для захвата счета в таймере/счетчики 1 по выполнению того или иного события на этой

ножке.

м) PB1 (OC1A) – 1 бит порта В и выход ШИМ сигнала таймера/счетчика 1

с А счетчиком, если он конечно подсоединен к этой ножке, и настроен как

ШИМ генератор.

н) PB2 (SS/OC1B) – 2 бит порта В, а также выход канала В таймера/счетчика 1.

п) PB3 (MOSI/OSC2) – 3 бит порта В, ножка, необходимая для

программирования микроконтроллера, и выходная ножка ШИМ

таймера 2.

р) PB4 (MISO) – 4 бит порта В, а также ножка необходимая для

программирования микроконтроллера.

с) PB5 (SCK) – 5 бит порта В и SCK – вход для тактовой частоты SPI внешнего соединения.

т) AVСС – напряжение питания АЦП.

у) AREF – напряжение источника внешнего опорного напряжения.

ф) AGND – общий провод для питания АЦП (0 В).

х) РС0 (ADC0) … РС3 (ADC3) – 0–3 биты порта С, и одновременно 0–3

каналы входов для АЦП.

ц) PC4 (ADC4/SDA) – 4 бит порта С, 4 канал АЦП и SDA – шина

подключения TWSI соединения с другим внешним устройством по TWSI

соединению.

ч) PC5 (ADC5/SCL) – 5 бит порта С, 4 канал АЦП и SCL – шина

подключения TWSI соединения с другим внешним устройством по TWSI

соединению. В более ранних версиях микроконтроллеров серии AVR многие ножки микроконтроллеров были отданы только одной единственной функции. В результате число ножек было велико. Затем производители микроконтроллеров нашли способ их использовать для двух функций. Это привело к уменьшению габаритов (числа ножек), но одновременно с этим это привело к невозможности использования одновременно всех функций.

Рассмотрим архитектуру микроконтроллера ATmega8 более подробно

(см. рис. 11.5).

На ножки VCC и GND подается напряжение питания микроконтроллера

– 5 В. На ножку AVCC, AGND подается напряжение питание мультиплексора

АЦП (MUX).

Мультиплексор переключает вход АЦП с одной ножки микроконтроллера на другую. В результате чего, в микроконтроллер можно заводить 6 аналоговых сигналов с напряжением от 0 до +5 В (ADC0 – ADC5), но при этом используется только одно АЦП.

Порты В, С и D имеют схожую друг с другом структуру. Поэтому

рассмотрим работу только одного из портов, например, порта В.

Порт В содержит буфер, в котором хранится значение, полученное с

входов порта или значения, которые наоборот необходимо выдать на ножки порт В. Также порт содержит устройство сопряжения буфера порта и общей шины (PORTB DIGITAL INTERFACE). Это устройство сопрягает данные полученные от порта В с общей шиной данных.

Остальные порты микроконтроллера имеют схожую структуру.

Единственное, что они также как и порт В несут на себе еще и

дополнительные функции, рассмотренные выше.

Основным устройством в микроконтроллере является ALU

(арифметическое логическое устройство), которое работает только с 32 регистрами – РОНами (general purpose registers) (рис. 11.5).

Эти РОНы занимают область памяти SRAM. Кроме того, 6 старших регистров образуют двухбайтные X, Y, Z регистры, которые служат

для косвенной адресации.

ALU выполняет, заданную арифметическую операцию над РОНами,

расставляет флаги в регистре статуса (SREG). И посылает результат в общую шину.

Из общей шины полученные данные могут быть переданы любому

устройству, в том числе различным областям памяти (EEPROM, SRAM, Flash).

SRAM – статическая оперативная память. Оперативное запоминающее устройство статического типа SRAM предназначено для хранения данных, получаемых в процессе работы микроконтроллера. При

выключении напряжения питания микроконтроллера данные в SRAM

теряются.

В адресном пространстве SRAM кроме адресов, по которым выполняется

обращение к ячейкам памяти SRAM, включены 32 адреса для обращения к регистрам общего назначения РОНам (адреса от 0x00 до 0x1F) и 64 адреса для обращения к регистрам ввода-вывода (адреса от 0x20 до 0x5F)

Flash – перезаписываемая флэш память. Постоянное запоминающее

устройство Flash предназначено для хранения кодов команд программы и констант. Ячейка памяти содержит 16 разрядов, В ней могут храниться код команды формата "слово" (два байта) или коды двух однобайтных констант.

EEPROM – энергонезависимая память. Постоянное запоминающее

устройство EEPROM предназначено для хранения данных, записанных при программировании микроконтроллера и получаемых в процессе выполнения программы. При выключении напряжения питания данные сохраняются. Одна ячейка памяти содержит 8 разрядов. Здесь обычно хранятся какие-то константы, к которым происходит очень редкое обращение или те данные, которые необходимо сохранить даже при пропадании питания. Время извлечения данных из этой области памяти в несколько раз больше чем из других областей памяти, поэтому эту память используют редко, чтобы не увеличивать время одного работы программы. EEPROM память данных организована как отдельное пространство данных с возможность считывания и записи отдельного байта или слова (два байта). EEPROM обеспечивает 100 000 циклов стирания/записи. Кроме звена передачи информации другим устройствам данный микроконтроллер содержит также SPI (Serial Peripheral Interface) устройство ввода вывода и передачу байтов при обмене данными с другими устройствами, имеющими порт SPI. А также последовательный порт ввода-вывода TWSI (Two-Wire Serial Interface), который предназначен для обмена байтами данных с другими устройствами по двухпроводной шине. Все выше рассмотренные устройства ввода вывода информации предназначены для передачи данных от одного устройства другому по различным сетевым протоколам.

Наиболее надежный и проверенный способ сохранения данных в

EEPROM заключается в установке внешнего монитора питания,

удерживающего МК в состоянии сброса при уменьшении напряжения

питания ниже порогового уровня. Это небольшая микросхема, как правило, трехвыводная, которая при снижении питания ниже допустимого уровня заворачивает свой выход на «землю». Если питание в норме, то выход находится в состоянии «разрыва» и никак не влияет на работу схемы.

Типичными представителями RISC-процессоров являются PIC-контроллеры производства фирмы MicroChip. PIC-контроллеры применяются в системах управления автомобильными и электрическими двигателями, приборах бытовой электроники, телефонных приставках с АОН, системах охраны с оповещением по телефонной линии, мини-АТС. Отдельные БИС отличаются разрядностью ПЗУ: от 12 до 14 бит в серии PIC16Схх, 16 бит – в серии PIC17Схх. Благодаря сокращенному числу команд (от 33 до 35) все команды занимают в памяти одно слово. Время выполнения каждой команды, кроме команд разветвления, составляет четыре такта, т.е. один машинный цикл. ОЗУ выполнено по схеме с произвольной выборкой с возможностью непосредственной адресацией. Стек реализован аппаратно и имеет глубину 2, 8 или 16 ячеек. Почти во всех PIC-контроллерах есть система прерываний, источниками прерываний для которой служить переполнение таймеров или изменение состояний сигналов на некоторых входах БИС. В PIC-контроллерах предусмотрен бит защиты ПЗУ который предотвращает нелегальное копирования содержимого памяти.

Простейший микроконтроллер имеет 8 выводов. Микроконтроллер 8-ми разрядный с Гарвардской архитектурой, что повышает производительность. Одновременно считывается команда и происходит обращение за данными. В некоторых микроконтроллерах есть операции умножения, деления, операции с плавающей точкой. Система команд компактная – не более 51 команды (LOW, LITLE и HIGH – 51 команда). Есть банки регистров как МК51.

Есть ПЗУ разных типов и перифирийные устройства (АЦП, ЦАП). В составе перифирийных устройств имеется несколько выводов последовательного интерфейса – обычный RS232, интерфейс I2C фирмы Philips, SPI.

Контроллеры PIC могут быть использованы как ²умные² перифирийные устройства, т.е. SLAVE – контроллер может быть подсоединен к управляющему контроллеру PIC как обычное перифирийное устройство через порт (или линю данных). Очень развиты перифирийные средства коммуникации (I2C, SPI, RS232, порты).

На основе PIC может быть организованна сеть микроконтроллеров (через шину I2C).

У SPI и I2C общая особенность: для передачи используется два провода.

Интерфейс SPI работает со стробиованием по фронту сигнала (клока), т.е. по одной линии передаются данные, по другой – клок.

В I2C стробирование осуществляется по уровню. В обоих интерфейсах Master обеспечивает выдачу сигналов тактирования.

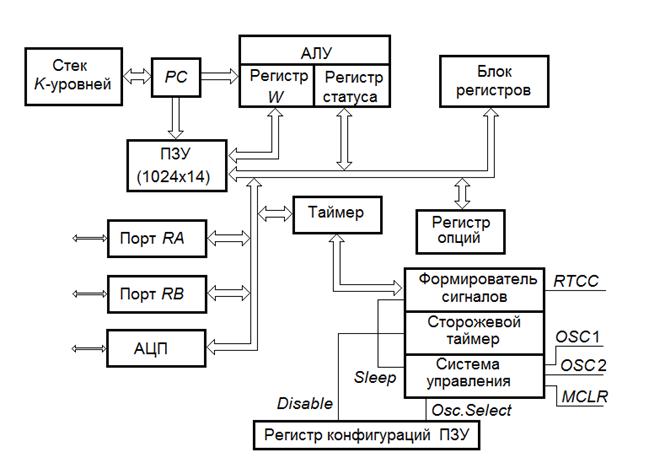

Архитектура PIC16-контроллеров.

Архитектуру PIC-контроллеров рассмотрим на прмере PIC16С71 (см. рис. 11.6). Основой являются раздельные шины и области памяти для данных и команд. Шина данных и ячейка ОЗУ – 8-разрядные, а шина команд и программная память (ПЗУ) – 14-разрядные. Двухступенчатый конвейер обеспечивает одновременные выбор и выполнение команды. Система команд содержит 35 команд. Все команды выполняются за один цикл, за исключением команд переходов, которые выполняются за два цикла.

микроконтроллера, т.к. не все функции микроконтроллера используются одновременно. Пример, если учитывать схему подключения внешнего генератора импульсов, которую можно заменить конденсатором, а также, что это схема для передачи постоянного сигнала – не помеха, то эти ножки можно использовать для ввода или вывода постоянных сигналов. Еще пример, можно запретить микроконтроллеру использовать сигнал Reset (ножка 1). Тогда эту ножку можно использовать для

ввода или вывода информации в микроконтроллер. Правда после такой операции невозможно будет перезаписать программу в микроконтроллере, т.к. чтобы выполнить эту операцию необходимо подать сигнал Reset.

а) PC6 (Reset) – сигнал сброса по прихода нулевого уровня (нуля вольт),

Это инверсный сигнал сброса, т.е. Reset происходит при появлении нуля

вольт на входе, а не 5В, одновременно является 6 битом порта С.

б) Ножки PD0 (RXD), PD1 (TXD) – необходимы для связи

микроконтроллера с другими устройствами по последовательному

интерфейсу UART. А также, одновременно, эти ножки являются 0 и 1 битом порта D. Ножка TXD – это выход передатчика UART. Если разрешена работа передатчика UART, независимо от состояния бита 1 в регистре DDRD (регистр направления передачи информации) этот вывод сконфигурирован как выход. Ножка RXD – выход приемника UART. Если разрешена работа приемника UART, независимо от состояния 0 бита в регистре DDRD (регистр направления передачи информации) этот вывод сконфигурирован как выход.

в) PD2 (INT0) и PD3 (INT1) – это входы внешних прерываний INT0 и INT1, а также 2 и 3 бит порта D.

г) PD4 (ХСК/T0) – это счетный вход таймера/счетчика 0, если он настроен

как счетчик, а также эта ножка является 4 битом порта D.

д) VСС – питание микроконтроллера. Сюда подается сигнал в 5В. Т.к. без

питания микроконтроллер вообще не работоспособный, то эту ножку не

совместили больше ни с какими функциями.

е) GND – общий провод.

ж) PB6 (XTAL1/TOSC1), PB7 (XTAL2/TOSC2) – ножки подключения

внешнего генератора. Одновременно эти ножки являются входами

выходами порта В.

и) PD5 (T1) – вход таймера/счетчика 1, если он настроен на счет

импульсов, т.е. как счетчик. Одновременно – это ножка 5 порта D.

к) PD6 (AIN0) и PD7 (AIN1) – входа аналогового компаратора и

одновременно 6 и 7 бит порта D.

л) PB0 (ICP) – ножка бита 0 порта В. ICP – вход для захвата счета в таймере/счетчики 1 по выполнению того или иного события на этой

ножке.

м) PB1 (OC1A) – 1 бит порта В и выход ШИМ сигнала таймера/счетчика 1

с А счетчиком, если он конечно подсоединен к этой ножке, и настроен как

ШИМ генератор.

н) PB2 (SS/OC1B) – 2 бит порта В, а также выход канала В таймера/счетчика 1.

п) PB3 (MOSI/OSC2) – 3 бит порта В, ножка, необходимая для

программирования микроконтроллера, и выходная ножка ШИМ

таймера 2.

р) PB4 (MISO) – 4 бит порта В, а также ножка необходимая для

программирования микроконтроллера.

с) PB5 (SCK) – 5 бит порта В и SCK – вход для тактовой частоты SPI внешнего соединения.

т) AVСС – напряжение питания АЦП.

у) AREF – напряжение источника внешнего опорного напряжения.

ф) AGND – общий провод для питания АЦП (0 В).

х) РС0 (ADC0) … РС3 (ADC3) – 0–3 биты порта С, и одновременно 0–3

каналы входов для АЦП.

ц) PC4 (ADC4/SDA) – 4 бит порта С, 4 канал АЦП и SDA – шина

подключения TWSI соединения с другим внешним устройством по TWSI

соединению.

ч) PC5 (ADC5/SCL) – 5 бит порта С, 4 канал АЦП и SCL – шина

подключения TWSI соединения с другим внешним устройством по TWSI

соединению. В более ранних версиях микроконтроллеров серии AVR многие ножки микроконтроллеров были отданы только одной единственной функции. В результате число ножек было велико. Затем производители микроконтроллеров нашли способ их использовать для двух функций. Это привело к уменьшению габаритов (числа ножек), но одновременно с этим это привело к невозможности использования одновременно всех функций.

Рассмотрим архитектуру микроконтроллера ATmega8 более подробно

(см. рис. 11.5).

На ножки VCC и GND подается напряжение питания микроконтроллера

– 5 В. На ножку AVCC, AGND подается напряжение питание мультиплексора

АЦП (MUX).

Мультиплексор переключает вход АЦП с одной ножки микроконтроллера на другую. В результате чего, в микроконтроллер можно заводить 6 аналоговых сигналов с напряжением от 0 до +5 В (ADC0 – ADC5), но при этом используется только одно АЦП.

Порты В, С и D имеют схожую друг с другом структуру. Поэтому

рассмотрим работу только одного из портов, например, порта В.

Порт В содержит буфер, в котором хранится значение, полученное с

входов порта или значения, которые наоборот необходимо выдать на ножки порт В. Также порт содержит устройство сопряжения буфера порта и общей шины (PORTB DIGITAL INTERFACE). Это устройство сопрягает данные полученные от порта В с общей шиной данных.

Остальные порты микроконтроллера имеют схожую структуру.

Единственное, что они также как и порт В несут на себе еще и

дополнительные функции, рассмотренные выше.

Основным устройством в микроконтроллере является ALU

(арифметическое логическое устройство), которое работает только с 32 регистрами – РОНами (general purpose registers) (рис. 11.5).

Эти РОНы занимают область памяти SRAM. Кроме того, 6 старших регистров образуют двухбайтные X, Y, Z регистры, которые служат

для косвенной адресации.

ALU выполняет, заданную арифметическую операцию над РОНами,

расставляет флаги в регистре статуса (SREG). И посылает результат в общую шину.

Из общей шины полученные данные могут быть переданы любому

устройству, в том числе различным областям памяти (EEPROM, SRAM, Flash).

SRAM – статическая оперативная память. Оперативное запоминающее устройство статического типа SRAM предназначено для хранения данных, получаемых в процессе работы микроконтроллера. При

выключении напряжения питания микроконтроллера данные в SRAM

теряются.

В адресном пространстве SRAM кроме адресов, по которым выполняется

обращение к ячейкам памяти SRAM, включены 32 адреса для обращения к регистрам общего назначения РОНам (адреса от 0x00 до 0x1F) и 64 адреса для обращения к регистрам ввода-вывода (адреса от 0x20 до 0x5F)

Flash – перезаписываемая флэш память. Постоянное запоминающее

устройство Flash предназначено для хранения кодов команд программы и констант. Ячейка памяти содержит 16 разрядов, В ней могут храниться код команды формата "слово" (два байта) или коды двух однобайтных констант.

EEPROM – энергонезависимая память. Постоянное запоминающее

устройство EEPROM предназначено для хранения данных, записанных при программировании микроконтроллера и получаемых в процессе выполнения программы. При выключении напряжения питания данные сохраняются. Одна ячейка памяти содержит 8 разрядов. Здесь обычно хранятся какие-то константы, к которым происходит очень редкое обращение или те данные, которые необходимо сохранить даже при пропадании питания. Время извлечения данных из этой области памяти в несколько раз больше чем из других областей памяти, поэтому эту память используют редко, чтобы не увеличивать время одного работы программы. EEPROM память данных организована как отдельное пространство данных с возможность считывания и записи отдельного байта или слова (два байта). EEPROM обеспечивает 100 000 циклов стирания/записи. Кроме звена передачи информации другим устройствам данный микроконтроллер содержит также SPI (Serial Peripheral Interface) устройство ввода вывода и передачу байтов при обмене данными с другими устройствами, имеющими порт SPI. А также последовательный порт ввода-вывода TWSI (Two-Wire Serial Interface), который предназначен для обмена байтами данных с другими устройствами по двухпроводной шине. Все выше рассмотренные устройства ввода вывода информации предназначены для передачи данных от одного устройства другому по различным сетевым протоколам.

Наиболее надежный и проверенный способ сохранения данных в

EEPROM заключается в установке внешнего монитора питания,

удерживающего МК в состоянии сброса при уменьшении напряжения

питания ниже порогового уровня. Это небольшая микросхема, как правило, трехвыводная, которая при снижении питания ниже допустимого уровня заворачивает свой выход на «землю». Если питание в норме, то выход находится в состоянии «разрыва» и никак не влияет на работу схемы.

Типичными представителями RISC-процессоров являются PIC-контроллеры производства фирмы MicroChip. PIC-контроллеры применяются в системах управления автомобильными и электрическими двигателями, приборах бытовой электроники, телефонных приставках с АОН, системах охраны с оповещением по телефонной линии, мини-АТС. Отдельные БИС отличаются разрядностью ПЗУ: от 12 до 14 бит в серии PIC16Схх, 16 бит – в серии PIC17Схх. Благодаря сокращенному числу команд (от 33 до 35) все команды занимают в памяти одно слово. Время выполнения каждой команды, кроме команд разветвления, составляет четыре такта, т.е. один машинный цикл. ОЗУ выполнено по схеме с произвольной выборкой с возможностью непосредственной адресацией. Стек реализован аппаратно и имеет глубину 2, 8 или 16 ячеек. Почти во всех PIC-контроллерах есть система прерываний, источниками прерываний для которой служить переполнение таймеров или изменение состояний сигналов на некоторых входах БИС. В PIC-контроллерах предусмотрен бит защиты ПЗУ который предотвращает нелегальное копирования содержимого памяти.

Простейший микроконтроллер имеет 8 выводов. Микроконтроллер 8-ми разрядный с Гарвардской архитектурой, что повышает производительность. Одновременно считывается команда и происходит обращение за данными. В некоторых микроконтроллерах есть операции умножения, деления, операции с плавающей точкой. Система команд компактная – не более 51 команды (LOW, LITLE и HIGH – 51 команда). Есть банки регистров как МК51.

Есть ПЗУ разных типов и перифирийные устройства (АЦП, ЦАП). В составе перифирийных устройств имеется несколько выводов последовательного интерфейса – обычный RS232, интерфейс I2C фирмы Philips, SPI.

Контроллеры PIC могут быть использованы как ²умные² перифирийные устройства, т.е. SLAVE – контроллер может быть подсоединен к управляющему контроллеру PIC как обычное перифирийное устройство через порт (или линю данных). Очень развиты перифирийные средства коммуникации (I2C, SPI, RS232, порты).

На основе PIC может быть организованна сеть микроконтроллеров (через шину I2C).

У SPI и I2C общая особенность: для передачи используется два провода.

Интерфейс SPI работает со стробиованием по фронту сигнала (клока), т.е. по одной линии передаются данные, по другой – клок.

В I2C стробирование осуществляется по уровню. В обоих интерфейсах Master обеспечивает выдачу сигналов тактирования.

Архитектура PIC16-контроллеров.

Архитектуру PIC-контроллеров рассмотрим на прмере PIC16С71 (см. рис. 11.6). Основой являются раздельные шины и области памяти для данных и команд. Шина данных и ячейка ОЗУ – 8-разрядные, а шина команд и программная память (ПЗУ) – 14-разрядные. Двухступенчатый конвейер обеспечивает одновременные выбор и выполнение команды. Система команд содержит 35 команд. Все команды выполняются за один цикл, за исключением команд переходов, которые выполняются за два цикла.

| |

|

Рисунок 11.6 - Структурная схема контроллера PIC16С71

Труктурная схема контроллера содержит:

- 8-уровневый аппаратный стек (STACK);

- 13-разрядный программный счетчик команд ( PC );

- 8-разрядное АЛУ (ALU);

- ОЗУ (BlockREG), которое состоит из 36 8-разрядных РОН;

- 15 регистров специальных функции SFR;

- 8-разрядный таймер/счетчик (Т/С);

- модуль АЦП (ADC) с четырьмя входами;

- 13 линий ввода/вывода (4-разрядный порт РА, 8-разрядный порт РВ и линия RТСС;

-сторожевой таймер (WDT);

- формирователь Form внешнего сигнала RТСС или сигнала сторожевого таймера

- систему управления и синхронизации с внутренним генератором (Synh. Control System).

Лекция № 12

| ТЕМА: DSP процессоры. Структура, принципы организации и работы DSP – процессоров. Базовая архитектура сигнальных процессоров. |

Основные вопросы, рассматриваемые на лекции:

1. DSP процессоры.

2. Назначение ПЦОС

3. Структура DSP – процессоров

4. Базовая архитектура сигнальных процессоров

Процессоры цифровой обработки сигналов находят широкое

применение в самых различных областях, так, как они способны

обеспечивать работу в реальном масштабе времени как существующих, так

и принципиально новых устройств.

Процессор цифровой обработки сигналов (сигнальный процессор,

Digital Signal Processor) – это микропроцессор, особенностью работы

которого является поточный характер обработки больших объемов данных

в реальном масштабе времени и, как правило, с интенсивным обменом

данных с внешними устройствами. ПЦОС реализуется на основе так

называемой базовой архитектуры (DSP Basic Architecture).

Реальный масштаб времени (реальное время работы, Real Time

Scale) – это такой режим работы устройства, при котором регистрация и

арифметическая обработка (а при необходимости и анализ, визуализация,

сохранение, систематизация, синтез и передача по каналам связи) данных

производится без потерь информации, поступающей от ее источника.

Цифровая обработка сигнала (Digital Signal Processing) — это

арифметическая обработка в реальном масштабе времени

последовательности значений амплитуды сигнала, определяемых через

равные временные промежутки.

Аналоговая обработка сигнала, традиционно применяемая в

большинстве устройств, является во многих случаях более практичным и

дешевым способом достижения требуемого результата. Однако тогда,

когда требуется высокая точность обработки данных, реализация

устройства в весьма компактном и миниатюрном виде, достижение

высокой стабильности характеристик устройства в различных

температурных условиях функционирования, цифровая обработка

оказывается единственно приемлемым решением.

На основе ПЦОС создаются устройства в которых требуется

реальный масштаб времени выполнения практически любых

арифметических задач. В то же время, можно выделить ряд типовых,

наиболее распространенных задач, решаемых с применением ПЦОС:

· фильтрация сигналов;

· свертка двух сигналов (смешение сигналов);

· вычисление значений авто и кросс-корреляционной функции двух

сигналов;

· усиление, нормализация или преобразование сигналов;

· прямое и обратное Фурье-преобразование;

· и др.

Основные направления применения ПЦОС

ПЦОС широко применяются в следующих областях:

· телекоммуникации;

· приборостроение ц(ифровые функционально- и проблемно-

ориентированные приборы);

· автоматизация в промышленности;

· управление техническими системами;

· автомобилестроение;

· медицина;

· обработка голоса и речи;

· обработка изображений и графические станции;

· бытовые приборы;

· оборонные отрасли;

· и др.

Базовая архитектура ПЦОС

Отличительной чертой задач цифровой обработки сигналов является

поточный характер обработки больших объемов данных в реальном

масштабе времени, требующий от технических средств высокой

производительности и возможности интенсивного обмена с внешними

устройствами. Это достигается в настоящее время благодаря специфической архитектуре ПЦОС, называемой базовой архитектурой ПЦОС.

Базовая архитектура ПЦОС – это совокупность характерных

особенностей процессора, направленная на повышение его производительности и отличающая ПЦОС от микросхем других типов.

Она обусловлена:

применением модифицированной гарвардской архитектуры;

широкому использованием конвейерного режима работы;

наличием специализированного устройства умножения;

наличием специальных команд для цифровой обработки сигналов;

реализацией короткого командного цикла.

Гарвардская архитектура

Гарвардская архитектура применяется для повышения

производительности (быстродействия) и гибкости работы ПЦОС.

Гарвардская архитектура в классическом варианте подразумевает

размещение программы и данных в раздельных ЗУ и их передачу по

раздельным шинам. Это позволяет полностью совмещать во времени

выборку и исполнение команд.

Модифицированная гарвардская архитектура допускает обмен

содержимым между памятью программ и памятью данных, что расширяет

возможности устройства.

Конвейер

Конвейер также применяется в целях повышения

производительности ПЦОС. Так, в четырехкаскадном конвейере (например, в ПЦОС TMS320C2xx) ПЦОС может обрабатывать одновременно четыре команды, причем все команды находятся на разных стадиях выполнения. В четырехкаскадном конвейере предварительную выборку команды,

дешифрирование, выборку операнда и исполнение команд можно

осуществлять независимым образом. Пока производится предварительная

выборка команды N, предыдущая команда N─1 дешифрируется, команда

N─2 выбирает операнд, а N─3 исполняется.

Следует отметить, что конвейер реализован автоматически таким

образом, что специалист, программирующий ПЦОС никак не замечает его

наличие.

Дата: 2019-03-05, просмотров: 695.