Стремительный прогресс в области проектирования логических систем на ПЛИС был предопределен тем, что все логические системы основываются на четко проработанном математическом аппарате алгебры Буля. Эта теория позволяет доказать, что построение произвольной логической функции возможно путем упорядоченной композиции лишь одного элементарного оператора - логического И-НЕ (или ИЛИ-НЕ). То есть любую строго логическую систему можно проектировать из элементов всего одного типа, например И-НЕ.

Совсем иная ситуация в области проектирования (синтеза) и анализа (декомпозиции) принципиальных схем аналоговых систем. В аналоговой электронике до сих пор нет единого общепризнанного математического аппарата, который позволил бы решать задачи анализа и синтеза с единых методологических позиций. Причины этого явления следует искать в истории развития аналоговой электроники.

На ранних этапах схемотехника аналоговых устройств развивалась в соответствии с концепциями функционально-узлового метода, основной идеей которого было деление сложных принципиальных схем на узлы. Узел состоит из группы элементов и выполняет вполне определенную функцию. При объединении узлы образуют блоки, платы, шкафы, механизмы - т.е. какие-то единые конструкции, которые называют устройствами. Объединение устройств образует систему. Функционально-узловой метод предполагал, что элементарными составляющими систем должны быть узлы, основная задача которых - выполнение вполне определенной функции.

Именно поэтому за критерий классификации узлов была принята функциональность, то есть факт выполнения узлом какой-то функции. Однако по мере развития электроники выделенных и обособленных функций (следовательно - и узлов) оказалось чрезвычайно много. Исчезла всякая возможность их минимизации и унификации, что необходимо для синтеза сложных систем. Именно поэтому тормозилось и продолжает тормозиться развитие матричных аналоговых БИС (МАБИС) и перепрограммируемых аналоговых интегральных схем (ПАИС).

Состояние дел в области программируемых аналоговых схем можно проследить, анализируя разработки ведущих российских и иностранных компаний. Так, специалисты ОАО "НИИТТ и завод "Ангстрем" сосредоточили усилия на разработке и производстве аналого-цифровых БМК (базовых матричных кристаллов) типа "Руль" Н5515ХТ1, Н5515ХТ101, предназначенных для систем сбора данных, контроля и управления, для медицинской техники и контрольно-измерительной аппаратуры.

Конструкция этих БМК включает аналоговую и цифровую матрицу. Цифровая матрица содержит 115 цифровых базовых ячеек (230 вентилей 2И-НЕ), которые расположены пятью рядами по 23 ячейки в ряд. Аналоговая матрица объединяет 18 аналоговых базовых ячеек, размещенных двумя рядами по 9 ячеек. Между рядами аналоговых ячеек располагаются два ряда конденсаторов (номиналом 17,8 пФ) и два ряда диффузионных резисторов (по 24,8 кОм). Между аналоговой и цифровой частью расположен ряд 3,2-кОм резисторов.

В БМК предусмотрено два типа аналоговых ячеек (А и Б). Ячейки типа А состоят из 12 прп- и четырех рлр-транзисторов с изолированным коллектором и 38 многоотводных диффузионных резисторов. В ячейках типа Б четыре лрл-транзистора заменены двумя р-МОП-транзисторами. Периферийные ячейки типа А и Б содержат по четыре мощных лрл-транзистора (в ячейках типа Б - с изолированным коллектором) и по два биполярных транзистора.

Цифровые базовые ячейки представлены тремя типами - из четырех л-МОП-транзисторов, из четырех р-МОП-транзисторов и из комплиментарной пары биполярных транзисторов. Кроме того, на периферии кристалла расположены мощные цифровые ячейки, которые содержат по четыре мощных л-МОП- и р-МОП-транзисто-ра, а также по два лрл-транзистора, включенных по схеме Дарлингтона.

Для БМК разработаны библиотеки стандартных аналоговых и цифровых элементов, которые существенно облегчают и ускоряют процесс проектирования устройств на базе БМК. Эти и подобные им БМК содержат несоединенные между собой наборы электрорадиоэлементов (ЭРЭ), из которых может быть получен ряд функциональных узлов, оговоренных в библиотеке. Основной недостаток таких микросхем - весьма узкая область применения, ограниченная конкретными значениями номиналов и других характеристик ЭРЭ в данном наборе. Возможности функциональных узлов, разработанных и рекомендованных для данного набора, приводятся в сопровождающей микросхему библиотеке.

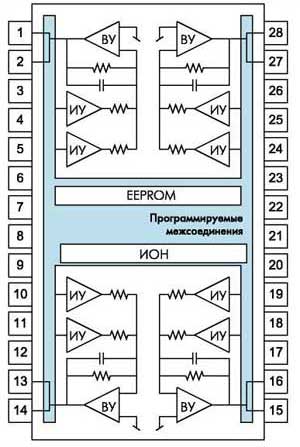

Рисунок 16.1 - Структура ispPAC-10

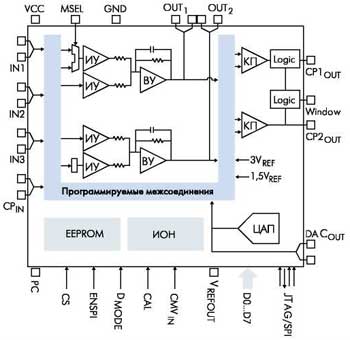

С 2000 года фирма Lattice Semiconductor выпускает программируемые аналоговые интегральные схемы (ПАИС) семейства ispPAC (In-System Programmable Analog Circuit) с программированием в системе, т.е. без извлечения из печатной платы [2, 3]. К середине 2000 года производились три представителя этого семейства: ispPAC-Ю (рис.1), ispPAC-20 (рис.2) и ispPAC-80. Они интегрируют до 60 активных и пассивных элементов, которые конфигурируются, моделируются и программируются с помощью пакета PAC-Designer.

ПАИС семейства ispPAC содержат:

• схемы последовательного интерфейса, регистры и элементы электрически репрограммируемой энергонезависимой памяти (EEPROM), обеспечивающие конфигурирование матрицы;

• программируемые аналоговые ячейки (PACcells) и состоящие из них программируемые аналоговые блоки (PACblocks);

• программируемые элементы для межсоединений (ARP - Analog Routing Pool).

Заложенная в эту серию архитектура основывается на базовых ячейках, содержащих: инструментальный усилитель (ИУ); выходной усилитель (ВУ), реализованный по схеме сумматора/интегратора; источник опорного напряжения 2,5 В (ИОН); 8-разрядный ЦАП с выходом по напряжению и сдвоенный компаратор (КП). Аналоговые входы и выходы ячеек (кроме ИОН) для повышения динамического диапазона обрабатываемых сигналов выполнены по дифференциальной схеме. Два ИУ и один ВУ образуют макроячейку, называемую РАС-блоком, в котором выходы ИУ соединены с суммирующими входами ВУ. Микросхема ispPAC-10 включает четыре РАС-блока, a ispPAC-20 - два. В состав ispPAC-20 также входят ячейки ЦАП и компараторов. В ячейке программируются коэффициент усиления ИУ в диапазоне от -10 до +10 с шагом 1, а в цепи обратной связи ВУ - величина емкости конденсатора (128 возможных значений) и включение/выключение сопротивления.

Ряд изготовителей ИС применяют для программирования аналоговых функций технологию "переключаемых конденсаторов", предполагающую изменение емкости частотно-задающих цепей посредством электронного ключа, переключающегося по условию.

Рисунок 16.2 - Структура ispPAC-20

Подход компании Lattice основан на использовании схем с постоянными во времени характеристиками, которые могут быть изменены в процессе переконфигурования системы без выключения питания. Это улучшение существенно, так как избавляет от дополнительных обработок сигнала, необходимых в первом методе.

Средства внутренней разводки (Analog Routing Pool) позволяют соединять друг с другом входные контакты микросхемы, входы и выходы макроячеек, выход ЦАП и входы компараторов. Объединяя несколько макроячеек, можно строить схемы перестраиваемых активных фильтров в диапазоне частот от 10 до 100 кГц, основанных на использовании звена интегратора.

Следует заметить, что ispPAC фирмы Lattice в наибольшей степени приближены к ПАИС. Единственный их недостаток - отсутствует система универсальных базовых элементов, которая позволяла бы проектировать не только перестраиваемые активные фильтры, а достаточно широкое множество аналоговых систем. Именно это обстоятельство мешает ispPAC фирмы Lattice Semiconductor стать аналогом ПЛИС таких фирм, как Altera и Xilinx.

В целом, анализируя ситуацию в области разработок и практических реализаций аналоговых микросхем, можно сделать ряд обобщений:

• основная масса промышленно реализованных аналоговых микросхем по степени интеграции не может быть отнесена к БИСам;

• аналоговые БИС и БМК предназначаются для проектирования устройств определенного класса, т.е. они не универсальны;

• при проектировании больших аналоговых систем главенствующим остается функционально-узловой метод (специализированные комплекты ИС, например для телевизионных приемников).

Однако задача разработки единого схемотехнического базиса проектирования аналоговых систем все же имеет решение, что мы попробуем теоретически обосновать и показать возможные направления практической реализации изложенных идей.

Прежде всего, следует выбрать математическую модель большой аналоговой электронной системы, которая позволила бы выделить малочисленную группу базисных элементов. В области анализа и синтеза электронных схем альтернатив математическому аппарату систем линейных дифференциальных уравнений практически нет, что было признано еще в шестидесятых годах прошлого столетия. Отметим, однако, что идея практического массового использования данной методологии и сегодня еще не овладела умами всех специалистов.

Система дифференциальных уравнений состоит из элементов, их связей и характеризуется определенной структурой. Элементный базис дифференциальных уравнений был исследован в первой половине прошлого века в рамках научной дисциплины "автоматика". В данной области проявилось такое достоинство дифференциальных уравнений, как унификация: их форма не зависит от описываемой модели процесса. Однако в стандартной форме записи дифференциального уравнения нет никакой наглядной информации о характере взаимосвязей в исследуемой системе. Поэтому методы наглядного отображения структуры систем дифференциальных уравнений в виде различного рода схем разрабатывались на всем протяжении развития теории автоматического управления.

К концу 60-х годов двадцатого века вполне сложилась современная точка зрения на структурную организацию моделей динамических систем. Формирование математической модели системы начинается с ее разбиения на звенья и последующего их описания - либо аналитически в виде уравнений, связывающих входные и выходные величины звена; либо графически в виде мнемосхем с характеристиками. По уравнениям или характеристикам отдельных звеньев составляются уравнения или характеристики системы в целом.

Дата: 2019-03-05, просмотров: 460.