| Бит | Обозначение | Дополнительная функция |

| P3.7 |

| Строб чтения из внешней памяти данных (Read Data for External Memory). |

| P3.6 |

| Строб записи во внешнюю память данных (Write Data for External Memory). |

| P3.5 | T1 | Внешний вход T/C1 (Timer/Counter 1 External Input). |

| P3.4 | T0 | Внешний вход T/C0 (Timer/Counter 0 External Input). |

| P3.3 |

| Вход внешнего прерывания 1 (External Interrupt 1 Input Pin). |

| P3.2 |

| Вход внешнего прерывания 0 (External Interrupt 0 Input Pin). |

| P3.1 | TxD | Выход данных передатчика последовательного порта (Serial Port Transmit Pin). |

| P3.0 | RxD | Вход данных передатчика последовательного порта (Serial Port Receive Pin). |

VCC : Напряжение питания микроконтроллера.

VSS : Потенциал земли.

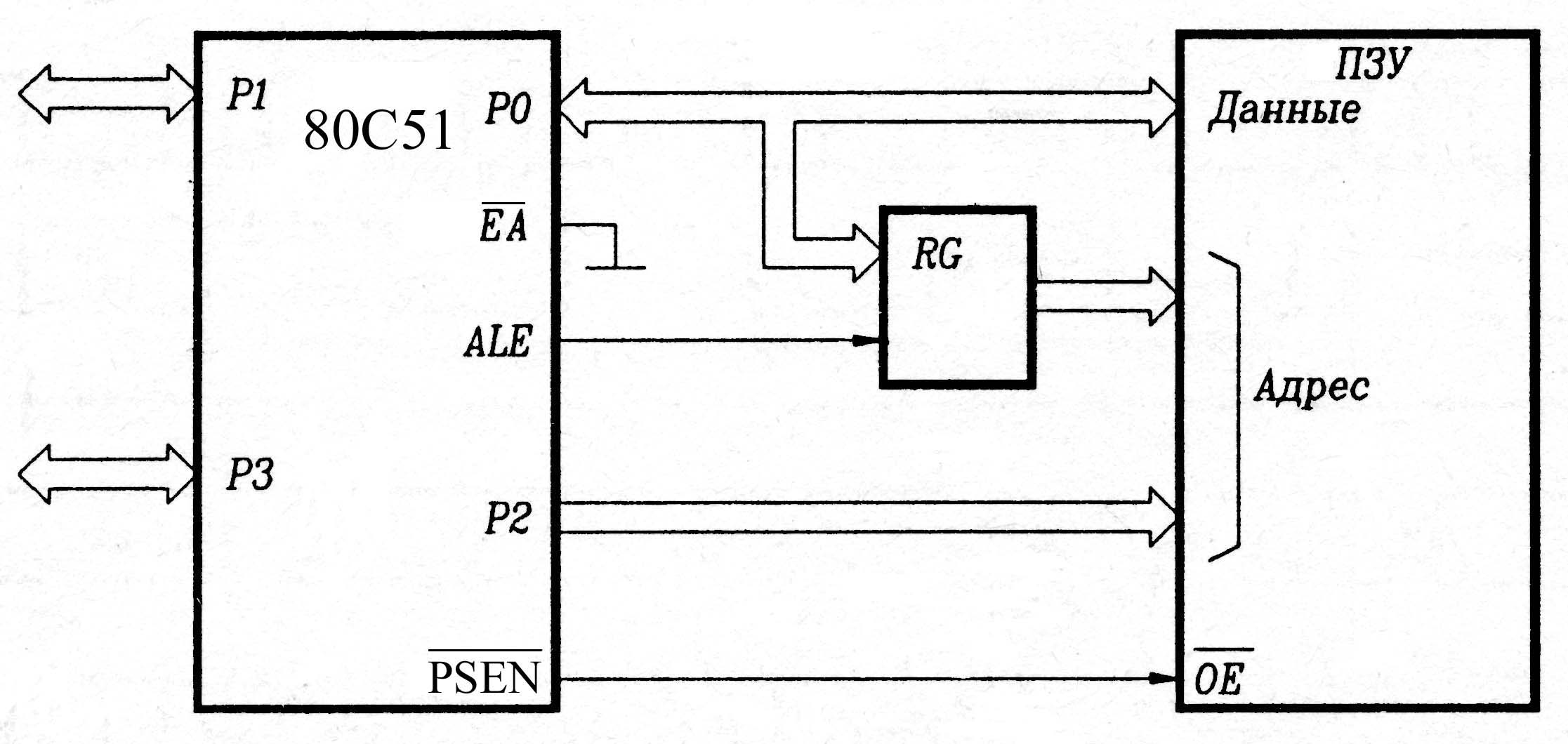

Подключение внешней памяти программ

При обращениях к внешней памяти программ всегда формируется 16-разрядный адрес, младший байт которого выдается через порт Р0, а старший – через порт Р2. При этом байт адреса, выдаваемый через порт Р0, должен быть зафиксирован во внешнем регистре по спаду сигнала ALE, т. к. в дальнейшем линии порта Р0 используются в качестве шины данных, по которой байт из внешней памяти программ вводится в микроконтроллер.

На рис. 10.6 показана функциональная схема включения микроконтроллера 80C51 с внешним ПЗУ программ. Порт Р0 работает как мультиплексированная шина адрес/данные: выдает младший байт счетчика команд, а затем переходит в z-состояние и ожидает прихода байта из ПЗУ программ. Когда младший байт адреса находится на выходах порта Р0, сигнал ALE защелкивает его в адресном регистре RG. Старший байт адреса находится на выходах порта Р2 в течение всего времени обращения к ПЗУ. Сигнал  разрешает выборку байта из ПЗУ, после чего выбранный байт поступает на порт Р0 80C51 и вводится в микроконтроллер.

разрешает выборку байта из ПЗУ, после чего выбранный байт поступает на порт Р0 80C51 и вводится в микроконтроллер.

Рисунок 10.6 - Функциональная схема подключения внешнего ПЗУ

Рисунок 10.7 - Схема подключения внешнего 8K ППЗУ типа К573РФ6

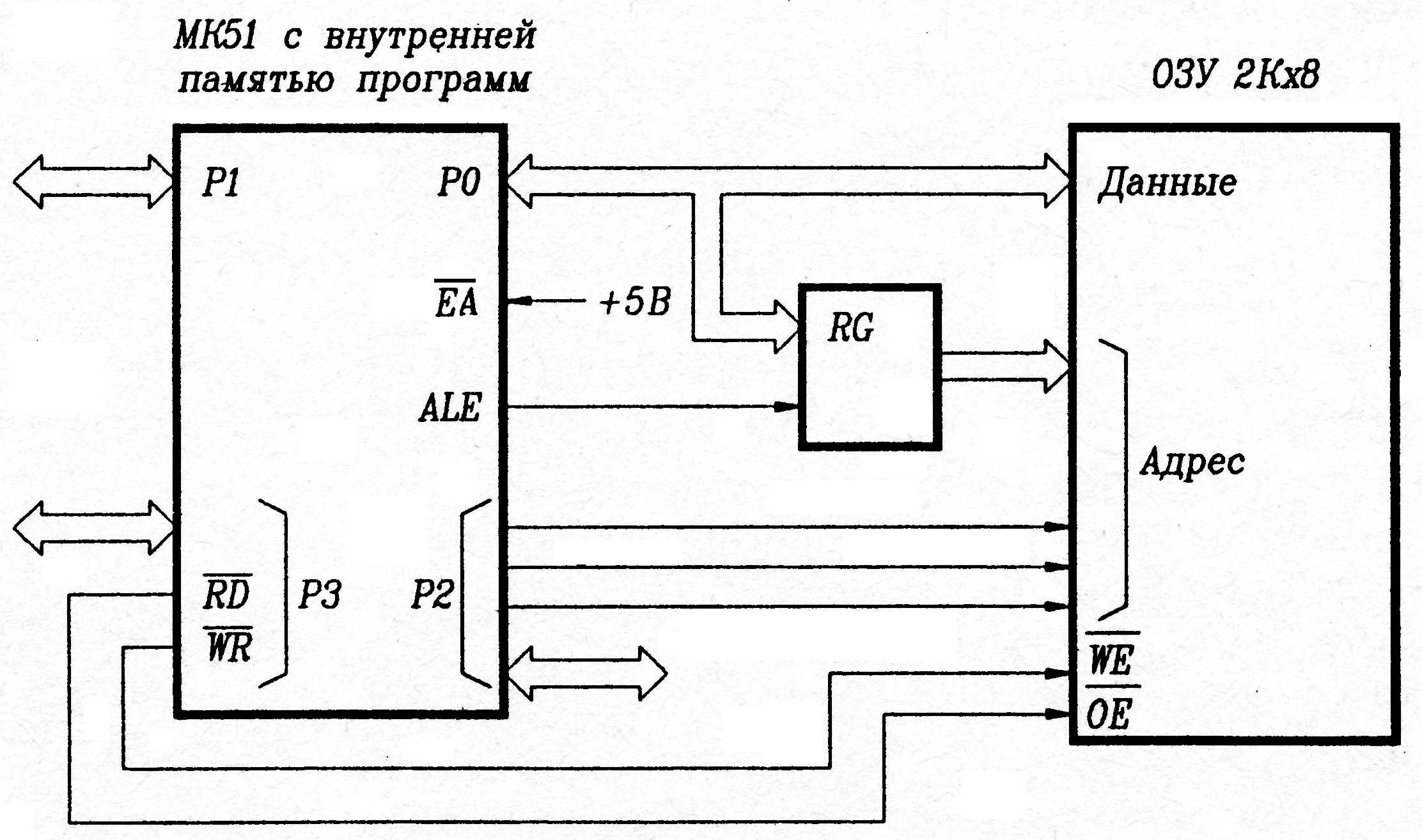

Выводы P3.6 и P3.7 микроконтроллера в схемах на рис.4.10 и 4.11 имеют альтернативное значение: P3.6 –  , а P3.7 –

, а P3.7 –  .

.

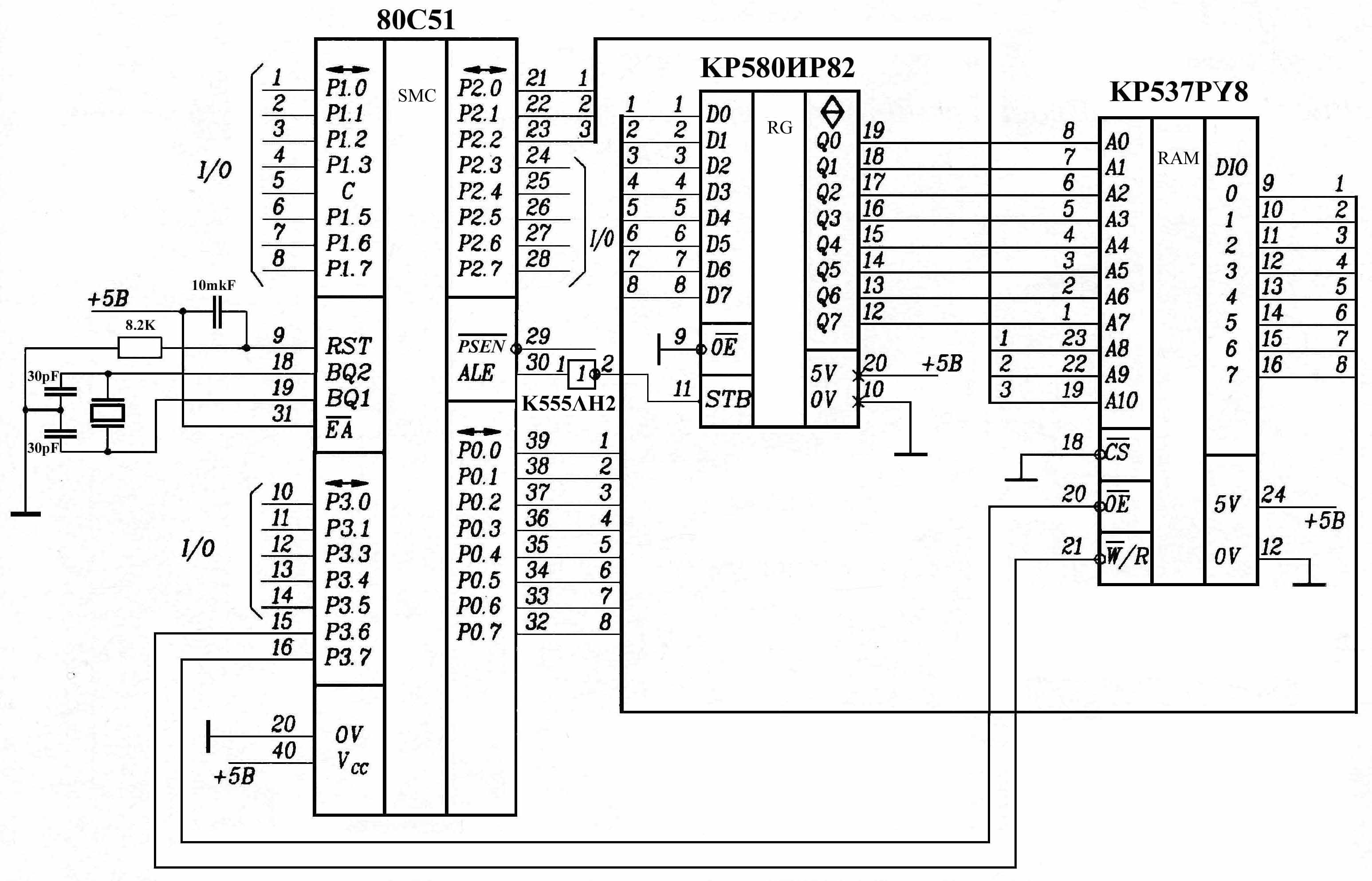

Схемы подключения внешнего ППЗУ на рис.4.10 и рис.4.11 обеспечивает адресацию 2K и 8K байт данных соответственно. Для этого первая использует 11-ти разрядную шину адреса, а вторая – 13-ти разрядную шину.

Младшие разряды (A0 – A7) адреса ячейки данных выдаются микроконтроллером через порт P0. Поскольку порт P0 используется также для ввода данных в микроконтроллер, шина адреса/данных демультиплексируется – младший байт адреса фиксируется в регистре-защелке КР580ИР82 по сигналу ALE микроконтроллера, стробирующего вход STB регистра.

Старшие разряды адреса (A8 – A10) для К573РФ5 и (A8 – A12) для К573РФ6 вырабатываются портом P2 микроконтроллера и не нуждаются в запоминании во внешнем регистре.

Таким образом, на адресные входы ППЗУ (A0 – A10 для К573РФ5 и A0 – A12 для К573РФ6) поступает младший байт адреса, зафиксированный в регистре КР580ИР82, и старшие разряды адреса, зафиксированные в порте P2 микроконтроллера.

Данные, выбранные из ячейки по этому адресу, поступают на выход ППЗУ по сигналу  микроконтроллера, выводящего выходные буферы БИС ППЗУ из третьего состояния.

микроконтроллера, выводящего выходные буферы БИС ППЗУ из третьего состояния.

Байт данных, выставленный ППЗУ на шину адреса/данных, вводится в микроконтроллер через порт P0.

Подключение внешнего оперативного запоминающего устройства

Рисунок 10.8 - Страничная организация внешней памяти данных

Рисунок 10.9 - Схема подключения внешнего ОЗУ типа КР537РУ8

Микроконтроллеры семейства MCS-251 Изначально наиболее «узкими» местами архитектуры MCS-51 были 8-разрядное АЛУ на базе аккумулятора и относительно медленное выполнение инструкций (для выполнения самых быстрых инструкций требуется 12 периодов тактовой частоты). Это ограничивало применение микроконтроллеров семейства в приложениях, требующих повышенного быстродействия и сложных вычислений (16- и 32- битовых). Насущным стал вопрос принципиальной модернизации старой архитектуры. Для решения этой задачи была создана совместная группа из специалистов компаний Intel и Philips, но позднее пути этих двух фирм разошлись. В результате в 1995 г. появилось 2 существенно отличающихся семейства: MCS-251/151 у Intel и 51XA у Philips.

Основные характеристики архитектуры MSC-251:

- 24-разрядное линейное адресное пространство, обеспечивающее адресацию до 16M памяти;

- регистровая архитектура , допускающая обращение к регистрам как к байтам, словам и двойным словам;

- страничный режим адресации для ускорения выборки инструкций из внешней программной памяти;

- очередь инструкций;

- расширенный набор команд, включающий 16-битовые арифметические и логические инструкции;

- расширенное адресное пространство стека до 64К;

- выполнение самой быстрой инструкции за 2 такта;

- совместимость на уровне кода с программами для MCS-51.

Система команд MCS-251 построена на базе двух наборов инструкций - первый набор является копией системы команд MCS-51, а второй набор состоит из расширенных инструкций, реализующих преимущества архитектуры MSC-251. Перед использованием микроконтроллера его необходимо сконфигурировать, т.е. с помощью программатора «прожечь» конфигурационные байты, определяющие, какой из наборов инструкций станет активным после включения питания. Если установить набор инструкций MCS-51, то в этом случае MSC-251 будет совместим с MCS-51 на уровне двоичного кода. Такой режим называется Binary Mode. Однако расширенные инструкции в этом режиме также доступны через «форточку» – зарезервированный код инструкции 0A5h. Естественно, длина каждой расширенной инструкции увеличивается в таком случае на 1 байт. Если же изначально установить набор расширенных инструкций, то в этом случае программы, написанные для MCS-51, потребуют перекомпиляции на кросс-средствах для MCS-51, т.к. теперь уже стандартные инструкции будут доступны через ту же «форточку» 0A5h и длина их также увеличится на 1 байт. Такой режим называется Source Mode. Он позволяет с максимальной эффективностью использовать расширенные инструкции и достигнуть наибольшего быстродействия, но требует переработки программного обеспечения.

Для пользователей, ориентированных на применение микроконтроллеров MCS-251 в качестве механической замены MCS-51 фирма Intel выпускает микроконтроллеры MCS-251 с уже запрограммированными битами конфигурации в состоянии Binary Mode. Такие микроконтроллеры получили индекс MCS-151.

Лекция № 11

ТЕМА: Микроконтроллеры AVR фирмы ATMEL . PIC контроллеры

Основные вопросы, рассматриваемые на лекции:

1. Микроконтроллеры AVR

2. Микроконтроллеры ATmega8

3. PIC контроллеры

Из семейств универсальных 8-разрядных микроконтроллеров, так сказать, «на все случаи жизни», наиболее распространены три: контроллеры классической архитектуры х51 (первый контроллер семейства 8051 был выпущен фирмой Intel еще в середине 1980-х), контроллеры PIC фирмы Microchip (идеально подходят для проектирования несложных устройств, особенно предназначенных для тиражирования), и Atmel AVR.

Одним из существенных преимуществ AVR стало использование конвейера. В результате для AVR не существует понятия машинного цикла: большинство команд, как мы говорили, выполняется за один такт (для сравнения отметим, что пользующиеся большой популярностью МК семейства PIC выполняют команду за 4 такта).

Другое огромное преимущество AVR-архитектуры — наличие 32 оперативных регистров, не во всем равноправных, но позволяющих в простейших случаях обходиться без обращения к оперативной памяти и, что еще важнее, без использования стека — главного источника ошибок у начинающих программистов (мало того, в младщих моделях AVR стек даже недоступен для программиста). Для AVR не существует понятия «аккумулятора», ключевого для ряда других семейств. Это еще больше приближает структуру ассемблерных программ для AVR к программам на языке высокого уровня, где операторы работают не с ячейками памяти и регистрами, а с абстрактными переменными и константами.

Но это, конечно, не значит, что AVR — однозначно лучшее в мире семейство МК. У него есть и ряд недостатков (например, несовершенная система защиты энергонезависимой памяти данных— EEPROM, некоторые вопросы с помехоустойчивостью, излишние сложности в системе команд и структуре программ и т. п.). Но в принципе любые универсальные современные МК позволяют делать одно и то же, и вопрос выбора платформы — вопрос в значительной степени предпочтений и личного опыта разработчика

Линейка универсальных контроллеров AVR общего назначения делится на семейства — Classic, Mega и Tiny (есть и новейшее семейство Xmega, но оно представляет весьма «навороченные» приборы не для наших задач). МК семейства Classic (они именовались, как АТ908<марка контроллера>) ныне уже не производятся, однако все еще распространены, так как они задержались на складах торгующих фирм, и, к тому же, для них наработано значительное количество программ. Чтобы пользователям не пришлось переписывать все ПО, фирма Atmel позаботилась о преемственности — большинство МК семейства Classic имеет функциональные аналоги в семействе Mega, например, AT90S8515— ATmega8515, AT90S8535— ATmega8535 и т.п. (только AT90S2313 имеет аналог в семействе Tiny — ATtiny2313).

Полная совместимость обеспечивается специальным установочным битом (из набора т. н. Fuse-битов), при программировании которого Mega-процессор начинает функционировать, как Classic (подробнее об этом рассказано в главе 19). Для вновь разрабатываемых устройств обычно нет никакого смысла в использовании их в режиме совместимости, однако такой прием в ряде случаев может оказаться полезным для начинающих, так как МК Classic устроены проще и не заставляют пользователя отвлекаться на некоторые ненужные подробности, не имеющие отношения к делу. Поэтому в книге далее будут приводиться иногда примеры и для «классической» серии.

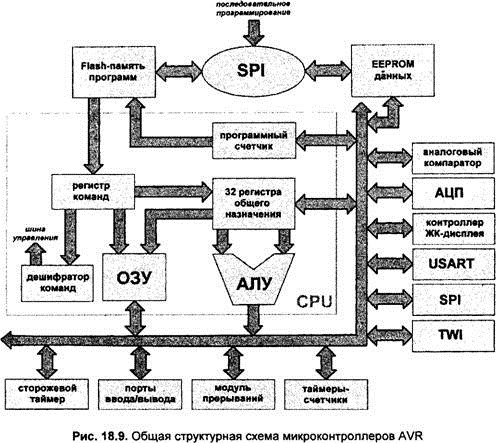

Семейство Tiny (что в буквальном переводе означает «крохотный») предна; значено для наиболее простых устройств. Часть МК этого семейства не имеет возможности программирования по последовательному интерфейс. Общая структура внутреннего устройства МК AVR приведена на рис. 11.1. На этой схеме показаны все основные компоненты AVR (за исключением некоторых специализированных); в отдельных моделях некоторые компоненты могут отсутствовать или различаться по характеристикам, неизменным остается только общее 8-разрядное процессорное ядро (GPU, General Processing Unit). Кратко рассмотрим наиболее важные компоненты, большинство из которых мы будем рассматривать в дальнейшем подробнее.

В структуре AVR имеются три разновидности памяти: flash-память программ, ОЗУ (SRAM) для временного хранения данных, и энергонезависимая память (EEPROM) для долговременного хранения констант и данных.

Рисунок 11.1 – Обобщенная структурная схема контроллеров AVR

Память программ

Встроенная flash-память программ в AVR-контроллерах имеет объем от 1 кбайта у ATtinyl 1 до 256 кбайт у ATmega2560. Первое число в наименовании модели содержит величину этой памяти в килобайтах, из ряда: 1, 2, 4, 8, 16, 32, 64, 128 и 256 кбайт. Так, ATtiny2313 имеет 2 кбайта памяти, а ATmega8535 — 8 кбайт.

С точки зрения программиста память программ можно считать построенной из отдельных ячеек— слов по два байта каждое. Устройство памяти программ (и только этой памяти!) по двухбайтовым словам— очень важный момент, который нужно твердо усвоить. Такая организация обусловлена тем.

что любая команда в AVR имеет длину ровно 2 байта. Исключение составляют команды jmp, call и некоторые другие (например, ids), которые оперируют с адресами 16-разрядной и более длины, длина этих команд составляет 4 байта, и они используются лишь в моделях с памятью программ более 8 кбайт, поэтому в этой книге вы их не встретите. Во всех остальных случаях счетчик команд сдвигается при выполнении очередной команды на 2 байта (одно слово), поэтому необходимую емкость памяти легко подсчитать, зная просто число используемых команд.

По умолчанию все контроллеры AVR всегда начинают выполнение программы с адреса $0000. Если в программе не используются прерывания, то с этого адреса может начинаться прикладная программа.

Память данных (ОЗУ, 3RAM)

в отличие от памяти программ, адресное пространство памяти данных адресуется побайтно (а не пословно). Адресация полностью линейная, без какого-то деления на страницы, сегменты или банки, как это принято в некоторых других системах. Исключая некоторые младшие модели Tiny, объем встроенной SRAM колеблется от 128 байт (например, у ATtiny2313) до 4—8 кбайт у старших моделей Mega.

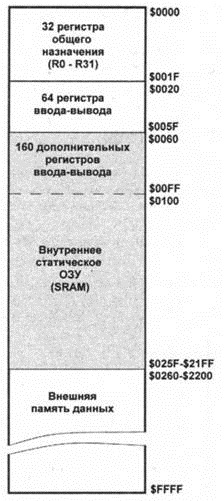

Адресное пространство статической памяти данных (SRAM) условно делится на несколько областей, показанных на рис. 18.10. К собственно встроенной SRAM относится лишь затемненная часть, до нее по порядку адресов расположено адресное пространство регистров, где первые 32 байта занимает массив регистров общего назначения (РОН), еще 64 — регистров ввода-вывода (РВВ).

Для некоторых моделей Mega (ATmega8515, ATmegal62, ATmegal28, AT-mega2560 и др.) предусмотрена возможность подключения внешней памяти объемом до 64 кбайт. Отметим, что адресные пространства РОН и РВВ не отнимают пространство у ОЗУ данньпс: так, если в конкретной модели МК имеется 512 байт SRAM, а пространство регистров занимает первые 96 байт (до адреса $60), то адреса SRAM займут адресное пространство от $0060 до $025F (то есть от 96 до 607 ячейки включительно). Конец встроенной памяти данных обозначается константой ramend. Следует учесть, что последние адреса SRAM, как минимум, на четыре—шесть ячеек от конца (в зависимости от количества вложенных вызовов процедур, для надежности лучше принять это число равным десяти или даже более) занимать данными не следует, так как они при использовании подпрограмм и прерываний заняты под стек.

Рисунок 11.2 - Адресное пространство статической памяти данных (SRAM) микроконтроллеров AVR

Операции чтения/записи в память одинаково работают с любыми адресами из доступного пространства, и потому при работе с SRAM нужно быть внимательным: вместо записи в память вы легко можете «попасть» в какой-нибудь регистр. Для обращения к РОН, как к ячейкам памяти, можно в качестве адреса подставлять номер регистра, а вот при обращении к РВВ таким же способом к номеру последнего нужно прибавлять $20. Следует также помнить, что по умолчанию при включении питания все РВВ устанавливаются в нулевое состояние во всех битах (единичные исключения все же имеются, поэтому в критичных случаях надо смотреть документацию), а вот РОН и ячейки SRAM могут принимать произвольные значения.

Дата: 2019-03-05, просмотров: 1256.