| Обозначение | Назначение бита |

| P3.7 | Строб чтения из внешней памяти данных (Read Data for External Memory,  ). ).

|

| P3.6 | Строб записи во внешнюю память данных (Write Data for External Memory,  ). ).

|

| P3.5 | Внешний вход T/C1 (Timer/Counter 1 External Input, T1). |

| P3.4 | Внешний вход T/C0 (Timer/Counter 0 External Input, T0). |

| P3.3 | Вход внешнего прерывания 1 (External Interrupt 1 Input Pin,  ). ).

|

| P3.2 | Вход внешнего прерывания 0 (External Interrupt 0 Input Pin,  ). ).

|

| P3.1 | Выход данных передатчика последовательного порта (Serial Port Transmit Pin, TxD). |

| P3.0 | Вход данных передатчика последовательного порта (Serial Port Receive Pin, RxD). |

Дополнительные функции порта могут быть активизированы, если соответствующий бит в SFR защелке порта содержит 1 (по умолчанию все биты установлены в 0).

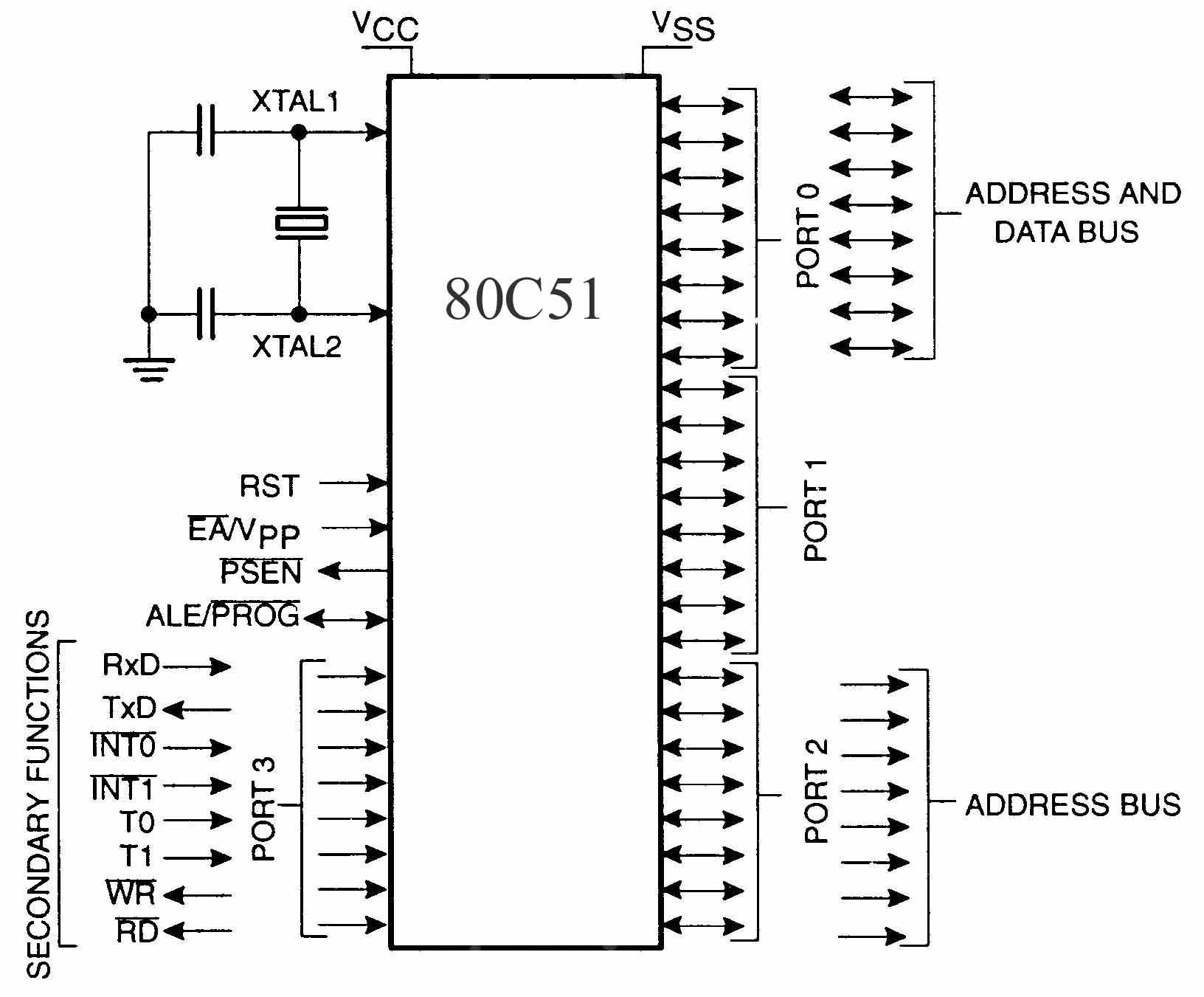

Назначение выводов БИС микроконтроллера 80С51 показано на рис.10.4, а их функции поясняет рис.10.5.

Рисунок 10.4 - Назначение выводов микроконтроллера

Рисунок 10.5 - Функциональное назначение выводов микроконтроллера

ALE /  : Выходной сигнал разрешения фиксации адреса (Address Latch Enable) служит для защелкивания младшего байта адреса во время доступа к внешней памяти. Сигнал ALE вырабатывается микроконтроллером с постоянной скоростью, равной 1/6 частоты внешнего тактового генератора, с целью тактирования или синхронизации внешних устройств. Отметим, что сигнал ALE вырабатывается даже в том случае, когда нет никаких обращений к внешней памяти. Однако, один импульс ALE пропускается в течение каждого цикла обращения к внешней памяти данных.

: Выходной сигнал разрешения фиксации адреса (Address Latch Enable) служит для защелкивания младшего байта адреса во время доступа к внешней памяти. Сигнал ALE вырабатывается микроконтроллером с постоянной скоростью, равной 1/6 частоты внешнего тактового генератора, с целью тактирования или синхронизации внешних устройств. Отметим, что сигнал ALE вырабатывается даже в том случае, когда нет никаких обращений к внешней памяти. Однако, один импульс ALE пропускается в течение каждого цикла обращения к внешней памяти данных.

Этот вывод служит также в качестве входа программирования (  ) при перепрограммировании встроенного ППЗУ.

) при перепрограммировании встроенного ППЗУ.

: Строб чтения внешнего ПЗУ (Program Store Enable) – это строб чтения из внешней памяти программ. Когда микроконтроллер работает от внешней памяти программ,

: Строб чтения внешнего ПЗУ (Program Store Enable) – это строб чтения из внешней памяти программ. Когда микроконтроллер работает от внешней памяти программ,  активизируется дважды за каждый машинный цикл. Однако,

активизируется дважды за каждый машинный цикл. Однако,  пропускается в течение каждого цикла обращения к внешней памяти данных. Отметим, что строб

пропускается в течение каждого цикла обращения к внешней памяти данных. Отметим, что строб  не активизируется, когда микроконтроллер работает от внутренней памяти программ.

не активизируется, когда микроконтроллер работает от внутренней памяти программ.

/ VPP : Сигнал разрешения доступа к внешнему ПЗУ (external access). Когда на вход

/ VPP : Сигнал разрешения доступа к внешнему ПЗУ (external access). Когда на вход  подано напряжение логической “1”, микроконтроллер работает от внутренней памяти программ (если счетчик команд 80C51 не превышает 0FFFH). Подача на

подано напряжение логической “1”, микроконтроллер работает от внутренней памяти программ (если счетчик команд 80C51 не превышает 0FFFH). Подача на  уровня “0” заставляет микроконтроллер работать от внешней памяти, независимо от состояния счетчика команд. Отметим, что в микроконтроллере 83СЗ1 вывод

уровня “0” заставляет микроконтроллер работать от внешней памяти, независимо от состояния счетчика команд. Отметим, что в микроконтроллере 83СЗ1 вывод  всегда должен быть подключен к “0”.

всегда должен быть подключен к “0”.

В устройствах с электрически перепрограммируемым ПЗУ на этот вывод подается опорное напряжение (VPP) во время программирования.

XTAL1 : Вход инвертирующего усилителя генератора.

XTAL2 : Выход инвертирующего усилителя генератора.

PORT 0 : Порт P0 – 8 битный двунаправленный порт с открытым стоком. Поскольку выводы порта имеют открытый сток, то каждый из них может быть нагружен на восемь ТТЛ - входов. Выводы порта P0, в которые записаны 1 находятся z - состоянии и будут функционировать как высокоимпедансные входы.

Порт P0 служит также мультиплексируемой шиной младшего байта адреса и данных при работе с внешней памятью. При этом он использует мощные внутренние подтягивающие резисторы во время генерации логических “1”.

Порт P0 служит для вывода данных D7 – D0 в режиме проверки внутреннего ПЗУ. При этом необходимы внешние подтягивающие резисторы.

PORT 1 : Порт P1 – 8 битный двунаправленный порт ввода/вывода с внутренними подтягивающими резисторами. Выводы порта P1, в которые записаны 1, подтягиваются в высокое состояние внутренними подтягивающими резисторами, и в этом состоянии их можно использоваться как вводы. Как входы, выводы порта P1 внешне подтягиваются в низ внутренними подтягивающими резисторами.

PORT 2 : Порт P2 – 8 битный двунаправленный порт ввода/вывода с внутренними подтягивающими резисторами. Порт P2 служит для вывода старшего байта адреса при работе с внешней памяти, которая использует 16-разрядную адресацию. При этом он использует мощные внутренние подтягивающие резисторы во время генерации логических “1”.

PORT 3 : Порт P3 – 8 битный двунаправленный порт ввода/вывода с внутренними подтягивающими резисторами и дополнительными функциями, представленными в таблице 10.3

Таблица 10.3

Дата: 2019-03-05, просмотров: 563.