Цели:

· Закрепить навыки упрощения логических выражений, используя логические законы

· Развивать логическое мышление

· Воспитывать умение слушать учителя и одноклассников

Теоретическая часть.

Равносильные преобразования логических формул имеют то же назначение, что и преобразования формул в обычной алгебре. Они служат для упрощения формул или приведения их к определённому виду путем использования основных законов алгебры логики.

Под упрощением формулы, не содержащей операций импликации и эквиваленции, понимают равносильное преобразование, приводящее к формуле, которая либо содержит по сравнению с исходной меньшее число операций конъюнкции и дизъюнкции и не содержит отрицаний неэлементарных формул, либо содержит меньшее число вхождений переменных.

Некоторые преобразования логических формул похожи на преобразования формул в обычной алгебре (вынесение общего множителя за скобки, использование переместительного и сочетательного законов и т.п.), тогда как другие преобразования основаны на свойствах, которыми не обладают операции обычной алгебры (использование распределительного закона для конъюнкции, законов поглощения, склеивания, де Моргана и др.).

Покажем на примерах некоторые приемы и способы, применяемые при упрощении логических формул:

1)

(законы алгебры логики применяются в следующей последовательности: правило де Моргана, сочетательный закон, правило операций переменной с её инверсией и правило операций с константами);

2)

(применяется правило де Моргана, выносится за скобки общий множитель, используется правило операций переменной с её инверсией);

3)

(повторяется второй сомножитель, что разрешено законом идемпотенции; затем комбинируются два первых и два последних сомножителя и используется закон склеивания);

4)

(вводится вспомогательный логический сомножитель (  ); затем комбинируются два крайних и два средних логических слагаемых и используется закон поглощения);

); затем комбинируются два крайних и два средних логических слагаемых и используется закон поглощения);

5)

(сначала добиваемся, чтобы знак отрицания стоял только перед отдельными переменными, а не перед их комбинациями, для этого дважды применяем правило де Моргана; затем используем закон двойного отрицания);

6)

(выносятся за скобки общие множители; применяется правило операций с константами);

Из этих примеров видно, что при упрощении логических формул не всегда очевидно, какой из законов алгебры логики следует применить на том или ином шаге. Навыки приходят с опытом.

УРОК №13

Тема: Схемы И, ИЛИ. НЕ. И-НЕ, ИЛИ-НЕ.

Теоретическая часть.

С х е м а И

Схема И реализует конъюнкцию двух или более логических значений. Условное обозначение на структурных схемах схемы И с двумя входами

Таблица истинности схемы И

x y x . y

0 0 0

0 1 0

1 0 0

1 1 1

Единица на выходе схемы И будет тогда и только тогда, когда на всех входах будут единицы. Когда хотя бы на одном входе будет ноль, на выходе также будет ноль.

Связь между выходом z этой схемы и входами x и y описывается соотношением: z = x . y

(читается как "x и y"). Операция конъюнкции на структурных схемах обозначается знаком "&" (читается как "амперсэнд"), являющимся сокращенной записью английского слова and .

С х е м а ИЛИ

Схема ИЛИ реализует дизъюнкцию двух или более логических значений. Когда хотя бы на одном входе схемы ИЛИ будет единица, на её выходе также будет единица.

Условное обозначение на структурных схемах схемы ИЛИ с двумя входами. Знак "1" на схеме — от устаревшего обозначения дизъюнкции как ">=1" (т.е. значение дизъюнкции равно единице, если сумма значений операндов больше или равна 1). Связь между выходом z этой схемы и входами x и y описывается соотношением: z = x v y (читается как "x или y").

Таблица истинности схемы ИЛИ

x y x v y

0 0 0

0 1 1

1 0 1

1 1 1

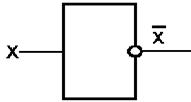

С х е м а НЕ

Схема НЕ (инвертор) реализует операцию отрицания. Связь между входом x этой схемы и выходом z можно записать соотношением z =  , где

, где  читается как "не x" или "инверсия х".

читается как "не x" или "инверсия х".

Если на входе схемы 0, то на выходе 1. Когда на входе 1, на выходе 0. Условное обозначение на структурных схемах инвертора

Таблица истинности схемы НЕ

x

0 1

1 0

С х е м а И—НЕ

Схема И—НЕ состоит из элемента И и инвертора и осуществляет отрицание результата схемы И. Связь между выходом z и входами x и y схемы записывают следующим образом:  , где

, где  читается как "инверсия x и y". Условное обозначение на структурных схемах схемы И—НЕ с двумя входами

читается как "инверсия x и y". Условное обозначение на структурных схемах схемы И—НЕ с двумя входами

Таблица истинности схемы И—НЕ

x y

0 0 1

0 1 1

1 0 1

1 1 0

С х е м а ИЛИ—НЕ

Схема ИЛИ—НЕ состоит из элемента ИЛИ и инвертора и осуществляет отрицание результата схемы ИЛИ. Связь между выходом z и входами x и y схемы записывают следующим образом:  , где

, где  , читается как "инверсия x или y ". Условное обозначение на структурных схемах схемы ИЛИ—НЕ с двумя входами представлено на рис. 5.5.

, читается как "инверсия x или y ". Условное обозначение на структурных схемах схемы ИЛИ—НЕ с двумя входами представлено на рис. 5.5.

Таблица истинности схемы ИЛИ—НЕ

x y

0 0 1

0 1 0

1 0 0

1 1 0

УРОК № 14

Тема: Триггеры, сумматор.

Теоретическая часть.

Триггер — это электронная схема, широко применяемая в регистрах компьютера для надёжного запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое — двоичному нулю.

Термин триггер происходит от английского слова trigger — защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает "хлопанье". Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить ("перебрасываться") из одного электрического состояния в другое и наоборот.

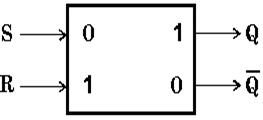

Самый распространённый тип триггера — так называемый RS-триггер (S и R, соответственно, от английских set — установка, и reset — сброс). Условное обозначение триггера — на рис.

Он имеет два симметричных входа S и R и два симметричных выхода Q и  , причем выходной сигнал Q является логическим отрицанием сигнала

, причем выходной сигнал Q является логическим отрицанием сигнала  .

.

На каждый из двух входов S и R могут подаваться входные сигналы в виде кратковременных импульсов (  ).

).

Наличие импульса на входе будем считать единицей, а его отсутствие — нулем.

На рис. показана реализация триггера с помощью вентилей ИЛИ—НЕ и соответствующая таблица истинности.

S R Q

0 0 запрещено

0 1 1 0

1 0 0 1

1 1 хранение бита

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ—НЕ

- Если на входы триггера подать S="1", R="0", то (независимо от состояния) на выходе Q верхнего вентиля появится "0". После этого на входах нижнего вентиля окажется R="0", Q="0" и выход

станет равным "1".

станет равным "1". - Точно так же при подаче "0" на вход S и "1" на вход R на выходе

появится "0", а на Q — "1".

появится "0", а на Q — "1". - Если на входы R и S подана логическая "1", то состояние Q и

не меняется.

не меняется. - Подача на оба входа R и S логического "0" может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 х 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

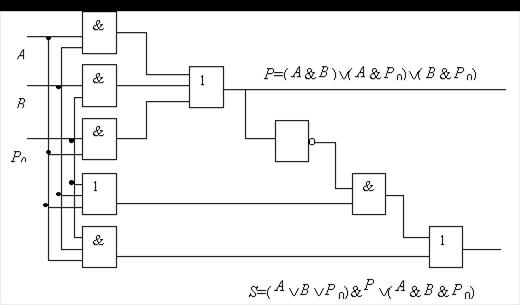

Сумматор — это электронная логическая схема, выполняющая суммирование двоичных чисел.

Сумматор служит, прежде всего, центральным узлом арифметико-логического устройства компьютера, однако он находит применение также и в других устройствах машины.

Многоразрядный двоичный сумматор, предназначенный для сложения многоразрядных двоичных чисел, представляет собой комбинацию одноразрядных сумматоров, с рассмотрения которых мы и начнём. Условное обозначение одноразрядного сумматора на рис.

При сложении чисел A и B в одном i-ом разряде приходится иметь дело с тремя цифрами:

1. цифра ai первого слагаемого;

2. цифра bi второго слагаемого;

3. перенос pi –1 из младшего разряда.

В результате сложения получаются две цифры:

1. цифра ci для суммы;

2. перенос pi из данного разряда в старший.

Таким образом, одноразрядный двоичный сумматор есть устройство с тремя входами и двумя выходами, работа которого может быть описана следующей таблицей истинности:

Входы Выходы

Первое слагаемое Второе слагаемое Перенос Сумма Перенос

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

Если требуется складывать двоичные слова длиной два и более бит, то можно использовать последовательное соединение таких сумматоров, причём для двух соседних сумматоров выход переноса одного сумматора является входом для другого.

Например, схема вычисления суммы C = (с3 c2 c1 c0) двух двоичных трехразрядных чисел A = (a2 a1 a0) и B = (b2 b1 b0) может иметь вид:

Практическая часть.

Пример 1. Существует 16 логических функций от двух переменных Построить их логические схемы с помощью логических элементов И, ИЛИ, НЕ.

Ответ:

F1 (константа 0)

F2 (конъюнкция)

F2 (конъюнкция)

F3 (отрицание импликации Х в Y)

F3 (отрицание импликации Х в Y)

F4 (переменная Х)

F5 (отрицание импликации Y в Х)

F5 (отрицание импликации Y в Х)

F6 (переменная Y)

F6 (переменная Y)

F7 (отрицание эквивалентности)

F8 (дизъюнкция)

F8 (дизъюнкция)

F9 (ИЛИ-НЕ)

F9 (ИЛИ-НЕ)

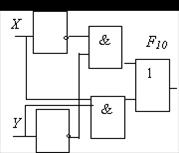

F10 (эквивалентность)  F11 (отрицание Y)

F11 (отрицание Y)

F12 (импликация Y в Х)

F12 (импликация Y в Х)

F13 (отрицание Х)

F14 (импликация Х в Y)

F14 (импликация Х в Y)

F15 (И-НЕ)

F15 (И-НЕ)

F16 (константа 1)

Пример 2 Доказать, что рассмотренная в примере 3.11 логическая схема является одноразрядным двоичным полусумматором (не учитывается перенос из младшего разряда).

Ответ: Таблица сложения одноразрядных двоичных чисел X и Y с учетом переноса в старший разряд выглядит следующим образом:

Слагаемые Перенос Сумма

X Y P S

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 0

Из этой таблицы сразу видно, что перенос можно реализовать с помощью операции логического умножения:

P = F1( X, Y) =X&Y

Получим теперь формулу для вычисления суммы. Значения суммы более всего совпадают с результатом операции логического сложения (кроме случая, когда на входы подаются две единицы, а на выходе должен получиться нуль)

Нужный результат достигается, если результат логического сложения умножить на инвертированный перенос. Таким образом, для определения суммы можно применить следующее логическое выражение:

S = F2(X,Y) = (XÚY)&(  )

)

Пример 3. Построить логическую схему одноразрядного двоичного сумматора.

Ответ:

Пример 4. Какое количество базовых логических элементов необходимо для реализации 64-разрядного сумматора двоичных чисел.

Ответ: Для построения одноразрядного сумматора двоичных чисел необходимо 9 базовых логических элементов. Следовательно: 9 ´ 64 = 576.

Пример 5. Какое количество базовых логических элементов составляют оперативную память современного компьютера объемом 64 Мбайта.

Ответ: Количество базовых логических элементов в триггере необходимо умножить на количество бит в ячейке оперативной памяти и умножить на количество ячеек:

4 ´ 8 ´ 64 ´ 1024 ´ 1024 = 2 147 483 648

УРОК №15-16

Дата: 2018-12-21, просмотров: 645.