Одним из основных логических элементов является инвертор. Инвертирующими каскадами являются однотранзисторный каскад с общим эмиттером, однотранзисторный каскад с общим истоком, двухтранзисторный двухтактный выходной каскад на комплементарных парах транзисторов с последовательным включением транзисторов по постоянному току (применяется в ТТЛ и КМОП), двухтранзисторный дифференциальный каскад с параллельным включением транзисторов по постоянному току (применяется в ЭСЛ) и др. Однако одного условия инвертирования недостаточно для применения инвертирующего каскада в качестве логического инвертора. Логический инвертор должен иметь смещённую рабочую точку на один из краёв проходной характеристики, что делает каскад неустойчивым в середине диапазона входных величин и устойчивым в крайних положениях (закрыт, открыт). Такой характеристикой обладает компаратор, поэтому логические инверторы строят, как компараторы, а не как гармонические усилительные каскады с устойчивой рабочей точкой в середине диапазона входных величин. Таких каскадов, как и контактных групп реле, может быть два вида: нормально закрытые (разомкнутые) и нормально открытые (замкнутые).

Микросхема 7404 содержит шесть отдельных инверторов. Все шесть инверторов микросхемы 7404 можно использовать независимо друг от друга.

При подаче напряжения низкого уровня на вход каждого из них на выходе микросхемы 7404 устанавливается напряжение высокого уровня, и наоборот.

Модель микросхемы инвертора 7404 имеет вид представленный на рисунке 7 и таблицу переходов состояний на входах и выходах (табл. 4).

Рисунок 7 – Модель микросхемы инвертора 7404

Таблица 4 – Таблица переходов микросхемы 7404

| Вход 1 | Выход 2 |

| 0 | 1 |

| 1 | 0 |

Шина – это группа проводников, по которым одновременно передается двоичный код числа. Шина необходима для подключения многоразрядных источников входных сигналов к компонентам схемы.

Шина чертится при нажатии кнопки «Place Bus» панели инструментов точно так же, как чертится один проводник.

После вычерчивания шины делаем «отводы», которые размещаются у шины при нажатии кнопки «Place bus entry», после этого делается нужное соединение «отвода» к выводам компонента схемы и им присваиваются имена A0 – A7.

3.6. Модель шифратора для преобразования восьми десятичных

Чисел (от 0 до 7) в 3-разрядный двоичный код

С приоритетом (74148)

Шифратор – это логическое устройство, выполняющее преобразование позиционного кода в n-разрядный двоичный код. Таким образом, шифратор – это комбинационное устройство, реализующее обратную дешифратору функцию. Наибольшее применение они находят в устройствах ввода информации (пультах управления) для преобразования десятичных чисел в двоичную систему счисления. Предположим, на пульте десять клавиш с гравировкой от 0 до 9. При нажатии любой из них на входы шифратора подается единичный сигнал (Х0, ..., Х9), а на соответствующем выходе шифратора появляется двоичный код (Y0, ..., Y9) этого десятичного числа [2].

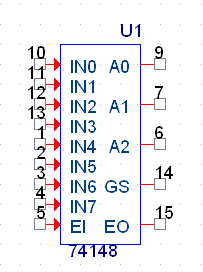

Модель шифратора представлена на рисунке 8. Модель 74148 хранится в библиотеке 7400 и позволяет расположить 8 входных сигналов в последовательности согласно приоритету важности сигнала. Чем больше число, подаваемое на вход, тем выше ее приоритет. Модель может использоваться как обычный шифратор десятичного числа в 3-разрядный двоичный код.

Рисунок 8 – Модель шифратора 74148

Модель имеет 8 входов (IN0, IN1, …, IN7), на каждый из которых подается сигнал, имеющий низкий уровень «0» или высокий «1». На трех выходах (А2, А1, А0) формируется инверсный 3-разрядный двоичный код, соответствующий десятичному номеру входа, на который подан низкий уровень сигнала.

Для модели 74148 активным является низкий уровень входного сигнала. Если на все входы подается сигнал высокого уровня, а на вход IN0 – низкого, то на всех выходах (А2, А1, А0) устанавливается сигнал высокого уровня, т. е. инверсный код 111, которому соответствует прямой код 000.

Если сигнал низкого уровня подается только на IN3, то на выходах устанавливаются следующие значения: А2 = 1, А1 = 0, А0 = 0. Этому инверсному двоичному коду соответствует прямой код 011.

Если на два или более входа одновременно подаются сигналы низкого уровня, то на выходах формируется инверсный код, соответствующий входу с наибольшим порядковым номером (наивысшим приоритетом), а состояние остальных входов игнорируется. Например, когда на входы IN1 и IN4 одновременно подаются сигналы низкого уровня, выходной инверсный сигнал установится равным 011 (что в прямом коде равно 100 и соответствует цифре 4 в десятичной системе счисления).

Кроме семи информационных входов и 3-х выходов в модели имеются еще 2 выхода GS и E0, служащие для каскадного соединения микросхем. На выходе GS формируется сигнал низкого уровня, если «0» подается на какой-либо из входов. На выходе Е0 формируется сигнал низкого уровня, когда на все входы подается напряжение высокого уровня. В нормальном режиме работы на вход ЕI должен подаваться сигнал низкого уровня. Работа модели шифратора 74148 представлена в таблице 5.

Таблица 5 – Работа модели шифратора 74148

| Вход | Выход | ||||||||||||

| ЕI | IN0 | IN1 | IN2 | IN3 | IN4 | IN5 | IN6 | IN7 | А2 | А1 | А0 | GS | E0 |

| 0 | Х | Х | Х | Х | Х | Х | Х | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | Х | Х | Х | Х | Х | Х | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | Х | Х | Х | Х | Х | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

| 0 | Х | Х | Х | Х | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0 | Х | Х | Х | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

| 0 | Х | Х | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 0 | Х | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

Дата: 2019-05-28, просмотров: 381.