Входом установки и входом сброса

Модель JK-триггера хранится в библиотеке 7400 и имеет имя 7472. Микросхема 7472 содержит синхронизируемый тактовым импульсом JK-триггер с логическими элементами, реализующими логическую операцию 3И над сигналами на входах J1, J2, J3 и К1, К2, К3, входом установки  и входом сброса

и входом сброса  . Наличие дополнительных входов J1, J2, J3 и К1,К2, К3 расширяет функциональные возможности триггера, поэтому JK-триггер называется универсальным. При соответствующем подключении входов JK-триггер может выполнять функции D-триггера, RS-триггера и T-триггера.

. Наличие дополнительных входов J1, J2, J3 и К1,К2, К3 расширяет функциональные возможности триггера, поэтому JK-триггер называется универсальным. При соответствующем подключении входов JK-триггер может выполнять функции D-триггера, RS-триггера и T-триггера.

После его размещения на чертеже, он имеет имя U1 и графическое изображение, показанное на рисунке 10. В нормальном режиме работы на входы  и

и  подается напряжение высокого уровня (+5 В) от источника постоянного напряжения V2 через два порта с именами HI. Тактовые импульсы поступают от генератора тактовых импульсов DSTM1, имеющего следующие свойства: OFFTIME = 0,7 us, ONTIME = 0,3 us, DELAY = 0,1 us, STARTVAL = 0, OPPVAL = 1, FORMAT 1, WIDTH 0. На входах J1, J2, J3 и К1, К2, К3 подаются сигналы от одноразрядных программируемых генераторов входных сигналов, имеющие свойства:

подается напряжение высокого уровня (+5 В) от источника постоянного напряжения V2 через два порта с именами HI. Тактовые импульсы поступают от генератора тактовых импульсов DSTM1, имеющего следующие свойства: OFFTIME = 0,7 us, ONTIME = 0,3 us, DELAY = 0,1 us, STARTVAL = 0, OPPVAL = 1, FORMAT 1, WIDTH 0. На входах J1, J2, J3 и К1, К2, К3 подаются сигналы от одноразрядных программируемых генераторов входных сигналов, имеющие свойства:

| DSTM2 COMMAND1 – 0 us 0 COMMAND2 – 1 us 1 COMMAND3 – 2 us 0 COMMAND4 – 3 us 1 COMMAND5 – 4 us 0 COMMAND6 – 5 us 1 COMMAND5 – 6 us 0 | DSTM3 COMMAND1 – 0 us 1 COMMAND2 – 1 us 0 COMMAND3 – 2 us 1 COMMAND4 – 3 us 0 COMMAND5 – 4 us 1 COMMAND6 – 5 us 0 COMMAND5 – 6 us 1 |

Рисунок 10 – Модель схемы подключения источников напряжения

и сигналов к микросхеме 7472

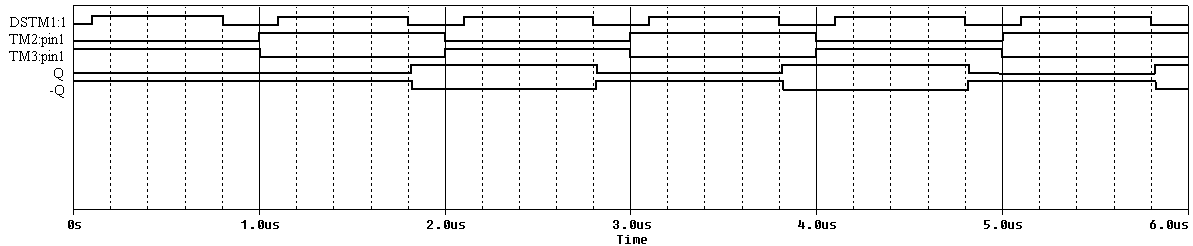

Если задать профиль моделирования Transient с параметром Run to time = 6us, то результатом будут диаграммы, приведенные на рисунке 11.

Рисунок 11 – Временные диаграммы, характеризующие работу

модели JK-триггера

Общие сведения о счетчиках

Счетчиком называется функциональный узел устройства обработки информации, предназначенный для подсчета числа импульсов, поступающих на его вход.

Счет числа поступающих импульсов производится в двоичной системе счисления. Обычно простые счетчики разделяются на: суммирующие, вычитающие и реверсивные.

Суммирующий счетчик предназначен для выполнения счета в прямом направлении, т. е. для сложения. С поступлением очередного импульса на вход счетчика, его показание увеличивается на единицу.

Вычитающий счетчик служит для осуществления счета в обратном направлении, т. е. для вычитания. Каждый импульс, поступающий на вход вычитающего счетчика, уменьшает его показание на единицу.

Реверсивный счетчик предназначен для операции счета, как в прямом, так и в обратном направлении, т. е. он может работать в режиме сложения и вычитания.

Основными показателями счетчиков являются коэффициент счета и быстродействие.

Коэффициент счета Ксч определяет число импульсов, которое может быть сосчитано счетчиком. Ксч определяется числом разрядов двоичного числа n: Ксч = 2n.

Быстродействие счетчика характеризуется максимальной частотой следования счетных импульсов и связанным с ней временем установки счетчика. Время установки определяется максимальным временем протекания переходных процессов во всех разрядах счетчика при поступлении на вход очередного счетного импульса.

Для хранения одного разряда двоичного числа применяется один триггер. Поэтому счетчик можно рассматривать как «связанную цепочку» n триггеров. Связи определяются типом применяемых триггеров.

Модель микросхемы четырехразрядного счетчика хранится в библиотеке 7400 и имеет имя 74191 (рис. 12).

Рисунок 12 – Модель микросхемы счетчика 74191

Схема замещения четырехразрядного счетчика, построенная на JK-триггерах, представлена на рисунке 13.

Рисунок 13 – Модель схемы четырехразрядного счетчика

на JK-триггерах

Дешифраторы

Дешифратором называется комбинационная схема с несколькими входами и выходами, преобразующая двоичный код, подаваемый на входы, в сигнал на одном из выходов.

В комбинационной схеме, построенной на элементах, которые реализуют логические операции, совокупность выходных сигналов в дискретный момент времени ti однозначно определяется входными сигналами, поступающими на вход в тот же момент времени.

В общем случае дешифратор имеет n входов и m = 2n выходов, поскольку n-разрядный двоичный код – на входе может принимать 2n различных значений. Каждому этому значению соответствует сигнал на одном выходе.

Дешифраторы устанавливаются в схемах ПК на выходах регистров или счетчиков и служат для преобразования двоичного кода, находящегося в регистре (или в счетчике), в управляющий сигнал на одном из выходов дешифратора. Как правило, в целях экономии оборудования, двоичный код из регистра передается на дешифратор не только своими прямыми значениями, но и инверсными. Поэтому часто дешифратор на 2n выходов имеет не n, а 2n входов.

Схемы дешифраторов строят различным образом в зависимости от формата дешифрируемого кода и особенностей применяемой системы логических элементов. По способам построения дешифраторы принято подразделять на: линейные, прямоугольные и пирамидальные. Различные схемы дешифраторов обычно сравнивают по быстродействию и аппаратным затратам. Быстродействие дешифраторов определяется временем задержки сигнала в нем (измеряется в наносекундах). Аппаратные затраты оцениваются количеством логических элементов в схеме дешифратора.

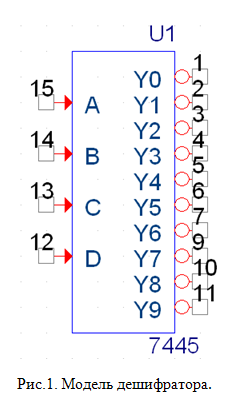

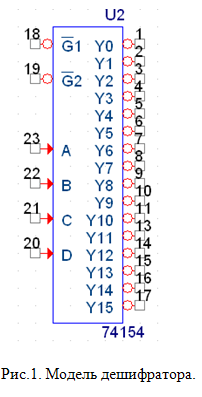

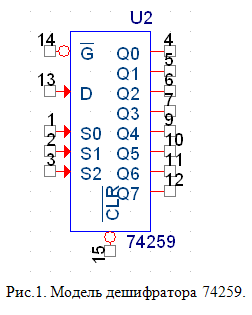

Дешифраторы хранятся в библиотеке 7400, их основные модели представлены на рисунке 14 (а, б, в).

а б в

Рисунок 14 – Модели дешифраторов: а – микросхема 7445;

б – микросхема 74154; в – микросхема 74259

Шифраторы

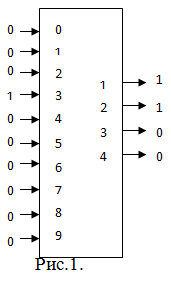

Шифратором называется комбинационная схема, которая преобразует один из десяти входных сигналов в 4-разрядный двоичный выходной сигнал. Это преобразование условно можно представить так, как показано на рисунке 15.

Другими словами: при появлении сигнала высокого уровня (1) на одном из входов (рис. 15, вход 3) на выходах появляются сигналы 0011, представляющие 4-разрядный двоичный код соответствующий цифре 3 десятичной системы счисления.

Одно из основных применений шифратора – это ввод данных с клавиатуры десятичных чисел. Нажатие клавиши с одной из десятичных цифр приводит к формированию и передаче в другие узлы двоичного кода этой цифры.

Рисунок 15 – Преобразование входного сигнала шифратором

Существует несколько видов шифраторов. Например, шифраторы, которые при одновременном нажатии нескольких клавиш вырабатывают код только старшей цифры, называются приоритетными. Для увеличения разрядности выходного кода применяют несколько шифраторов, выходы которых объединяются с помощью элементов, реализующих простые логические операции. Эта процедура называется каскадированием шифраторов.

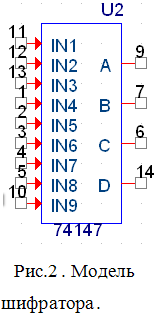

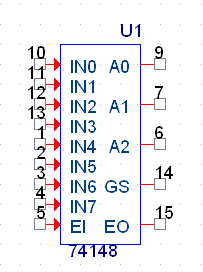

Шифраторы хранятся в библиотеке 7400, их основные модели представлены на рисунке 16 (а, б).

а б

Рисунок 16 – Модели шифраторов: а – микросхема 74147;

б – микросхема 74148

Литература

4.1. Основная литература

1. Новиков Ю. В. Введение в цифровую схемотехнику: Учебное пособие. М.: Интернет-Университет Информационных Технологий: БИНОМ. «Лаборатория знаний». 2007. 343 с.

2. Амосов В. В. Схемотехника и средства проектирования цифровых устройств: [Учебное пособие для вузов. Допущено УМО]. СПб.: БВХ-Петербург, 2007. 542 с.

3. Бойт Клаус. Цифровая электроника / Пер. с нем. М.: Техносфера, 2007. 471 с.

4. Бабич Н. П., Жуков И. А. Основы цифровой схемотехники. М.: Издат. дом "Додэка-XXI"; Киев: МК-Пресс, 2007. 479 с.

5. Каплан Д., Уайт К. Практические основы аналоговых и цифровых схем / Пер. с англ. М.: Техносфера, 2006. 174 с.

4.2. Дополнительная литература

1. Мышляева И. М. Цифровая схемотехника: [Учебник]. М.: ACADEMIA, 2005. 397 с.

2. Безуглов Д. А., Калиенко И. В. Цифровые устройства и микропроцессоры: Учебное пособие. Ростов н/Д: Феникс, 2006. 468 с.

Приложение 1

Пример оформления курсового проекта

Министерство образования и науки Российской Федерации

Дата: 2019-05-28, просмотров: 391.