В цифровой электронике широко используются функциональные узлы способные сохранять двоичную информацию (состояние 0 и 1) после окончания действия входного импульса. Такие функциональные узлы называются триггерами.

В интегральной микросхемотехнике триггеры выполняются как завершенный функциональный элемент в виде микросхемы. Иногда микросхема содержит 2 отдельных триггера. Интегральные триггеры характеризуются большим разнообразием. Их отличают по функциональным признакам, определяющим поведение триггера при воздействии сигнала управления, а также по используемому способу управления.

По функциональному признаку различают триггеры типов: D, JK, RS и другие.

По способу управления триггеры подразделяются на: асинхронные и синхронные (тактовые).

Модель D -триггера

Синхронный триггер D-типа – это запоминающий элемент с 2-мя устойчивыми состояниями и одним информационным D-входом.

Микросхема 7474 содержит 2 отдельных синхронных D-триггера, которые запускаются положительным фронтом тактового импульса и имеют раздельные входы установки и очистки (with Preset and Clear). Оба триггера можно использовать независимо друг от друга.

Условно-графическое изображение модели D-триггера в редакторе Capture представлено на рисунке 7.

Рисунок 7 – Модель D-триггера

Обычно работу триггера описывают таблицей переходов (табл. 3).

Технические данные:

– максимальная рабочая частота – 15 МГц;

– время задержки прохождения сигнала – 17 нс;

– ток потребления – 17 мА.

Пример схемы подключения D-триггера (7474) для получения временных диаграмм характеризующих его работу приведен на рисунке 8.

Таблица 3 – Таблица переходов D-триггера

| Входы | Выходы | ||||

|

| CLK | D | Q |

|

| L | H | X | X | H | L |

| H | L | X | X | L | H |

| L | L | X | X | H | H |

| H | H | H | H | L | |

| H | H | L | L | H | |

| H | H | L | X | Без изменений | |

| H | H | H | X | ||

| H | H | H | |||

Рисунок 8 – Модель D-триггера с подключенными источниками

сигналов

В нормальном режиме работы на выходы  и

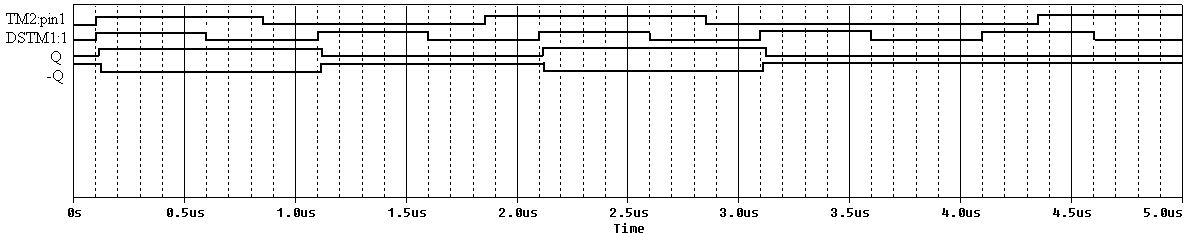

и  подается напряжение высокого уровня (+5В) от источника постоянного напряжения V1 через два порта с именами HI. Тактовые импульсы подаются от генератора DSTM1, имеющего следующие свойства: OFFTIME = 0,5 us; ONTIME = 0,5 us; DELAY = 0,1 us; STARTVAL = 0; OPPVAL = 1. На вход D подается сигнал от одноразрядного программируемого генератора входных сигналов DSTM2, со следующими командами: COMMAND1 – 0 us 0; COMMAND2 – 0,1 us 1; COMMAND3 – 0,85 us 0; COMMAND4 – 1,85 us 1; COMMAND5 – 2,85 us 0; COMMAND6 – 4,35 us 1

подается напряжение высокого уровня (+5В) от источника постоянного напряжения V1 через два порта с именами HI. Тактовые импульсы подаются от генератора DSTM1, имеющего следующие свойства: OFFTIME = 0,5 us; ONTIME = 0,5 us; DELAY = 0,1 us; STARTVAL = 0; OPPVAL = 1. На вход D подается сигнал от одноразрядного программируемого генератора входных сигналов DSTM2, со следующими командами: COMMAND1 – 0 us 0; COMMAND2 – 0,1 us 1; COMMAND3 – 0,85 us 0; COMMAND4 – 1,85 us 1; COMMAND5 – 2,85 us 0; COMMAND6 – 4,35 us 1

При поступлении тактового импульса на вход CLK, триггер переключается по переднему фронту и его выход Q принимает состояние входа D. На выходе  устанавливается противоположное состояние. Другими словами:

устанавливается противоположное состояние. Другими словами:

– если на вход D подается напряжение высокого уровня, то тактовый импульс устанавливает на выходе Q напряжение высокого уровня, а на выходе  – напряжение низкого уровня. В триггер записывается 1;

– напряжение низкого уровня. В триггер записывается 1;

– если на вход D подается напряжение низкого уровня, то тактовый импульс устанавливает на выходе Q напряжение низкого уровня, а на выходе  – напряжение высокого уровня. В триггер записывается 0.

– напряжение высокого уровня. В триггер записывается 0.

Если задать профиль моделирования Transient с параметром Run to time = 5 us, то результатом будут диаграммы, приведенные на рисунке 9.

Рисунок 9 – Временные диаграммы, характеризующие работу синхронного D-триггера

Дата: 2019-05-28, просмотров: 377.