Для формирования входных сигналов в цифровых схемах в модуле PSpice предусмотрены специальные источники напряжения, которые хранятся в библиотеке SOURCE.

1. Источник (генератор) тактовых импульсов имеет имя DigClock, предназначен для выдачи тактовых импульсов (синхросигналов) с регулируемой частотой следования.

Рисунок 2 – Модель источника тактовых импульсов DigClock

Основные свойства компонента DigClock устанавливаются в окне Property Editor:

– OFFTIME – это длительность паузы между тактовыми импульсами;

– ONTIME – это длительность тактового импульса;

– DELAY – это начальная задержка первого тактового импульса;

– STARTVAL – это значение тактового импульса (обычно равно 0);

– OPPVAL – это противоположное значение (относительно STARTVAL) тактового импульса (равно 1).

Важный момент!

После создания профиля моделирования и редактирования временных параметров, следует открыть страницу с вкладкой «Options». В разделе Category выбрать пункт Gate-level Simulation (англ.: уровень узла моделирования), а затем в пункте Initialize all flip-flops to (установить все переключения в) установить ‘0’.

Рисунок 3 – Модель схемы подключения 2И

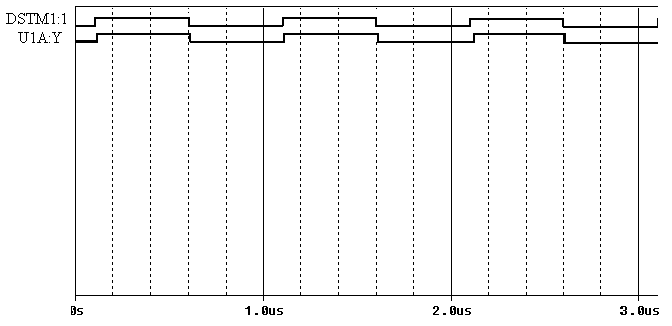

Например: если в редакторе Capture начертить схему, приведенную на рисунке 3, и запустить процесс моделирования, предварительно установив маркеры напряжения, выбрав профиль transient с параметрами Run to time 10us, то в окне Probe получим временные диаграммы, приведенные на рисунке 4.

Рисунок 4 – Временные диаграммы, характеризующие работу

компонента 7408

U1A – это первый из четырех логических элементов, находящихся в микросхеме 7408, который реализует логическую операцию «И » (логическое умножение, конъюнкция).

Для соединения источника постоянного напряжения с микросхемой 7408 можно использовать порты. Порт применяется для беспроводной связи между компонентами, источниками питания и т. д. Символы портов находятся в библиотеке, которая открывается после щелчка левой клавишей мыши по кнопке Place port панели инструментов, после чего появится окно с именем «Place Hierarchical Port» (размещение иерархического порта). Прокруткой выбираются имена портов PORTRIGHT-R (R – правый) или PORTRIGHT–L (L – левый – исправляемый порт).

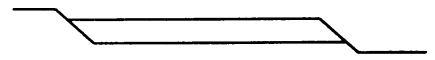

После щелчка по кнопке OK на схеме размещается элемент:

или

.

Имена PORTRIGHT-R и PORTRIGHT-L изменяются при двойном щелчке левой клавишей мыши по ним, после чего в открывшемся окне Display Properties имя заменяется на HI. После этого необходимо имя HI перетянуть в графическое изображение порта. HI означает высокий уровень сигнала (логическая 1), LO – низкий уровень сигнала (логический 0).

2. Модели источников входных сигналов представлены на рисунке 5: одноразрядный (STIM1) (рис. 5а), четырехразрядный (STIM4) (рис. 5б), восьмиразрядный (STIM8) (рис. 5в) и шестнадцатиразрядный (STIM16) (рис. 5г).

а б в г

Рисунок 5 – Модели источников входных сигналов

При двойном щелчке левой клавишей мыши по символу любого из этих источников открывается окно «Property Editor» в таблице, в котором можно задать 16 команд. Каждая команда состоит из значения момента времени и соответствующих ему логических состояний для одного, четырех, восьми или шестнадцати разрядов информационных шин.

Шина – это группа проводников, по которым одновременно передается код двоичного числа. Она необходима для подключения многоразрядных источников входных сигналов к компонентам схемы.

Шина чертится при нажатии кнопки Place Bus панели инструментов точно так же, как чертится один проводник.

После вычерчивания шины в нужных местах делаются «отводы», которые размещаются у шины при нажатии кнопки Place bus entry. После этого делается соединение отвода с выводом компонента схемы и присваиваются им имена D0, D1, D2 и т. д.

Методика черчения шины: щёлкните по <Place (Разместить)> → <Net Alias… (Рамка псевдонима…)>. В открывшемся окне Place Net Alias курсор введите в поле Alias: in и щёлкните по кнопке OK, закройте это окно. После этого к указателю мыши «прилипает» прямоугольник (рамка), нижнюю сторону которого совместите с соединением источника напряжения V1 и инвертора U1A. Щелчком левой кнопки мыши закрепите «псевдоним » соединения, затем щёлкните по правой кнопке и в открывшемся меню щёлкните по опции End Mode (конец режима работы).

Каждая команда окна «Property Editor» определяет уровень логического сигнала на каждом проводнике шины, как показано на рисунке 6.

Наряду со свойствами COMMAND источники сигналов STIM имеют свойства FORMAT, которое принимает разные значения. Если FORMAT имеет значение 1111 – это означает 4-х разрядный двоичный формат, FORMAT = 4444 – это 8-ми разрядный двоичный формат. Свойство WIDTH определяет разрядность информационной шины (например: WIDTH = 4; WIDTH = 8; WIDTH = 16).

Значения этих свойств устанавливаются системой по умолчанию.

Рисунок 6 – Пример соединения компонентов схемы

с шиной и источником входных сигналов

При указании логических состояний в системе OrCAD применяются обозначения, которые приведены в таблице 2.

Таблица 2 – Обозначения логических состояний

и фрагментов временных диаграмм

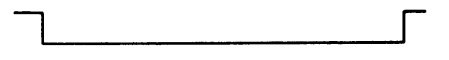

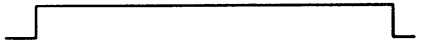

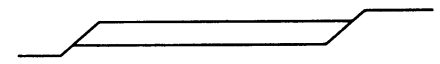

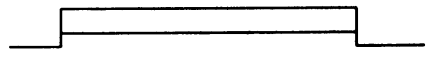

| Обозначение логического состояния | Состояние | Изображение в PROBE |

| 0 | Логический нуль |

|

| 1 | Логическая единица |

|

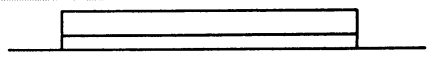

| R | Нарастание фронта (Rise) |

|

| F | Спад фронта |

|

| X | Неопределенное состояние |

|

| Z | Высокоимпедансное (высокоомное) состояние |

|

Дата: 2019-05-28, просмотров: 394.