КОНСПЕКТ ЛЕКЦИЙ

Направление подготовки

(специальность) Техническая эксплуатация транспортного

25.05.03 радиооборудования

код ОКСО наименование

Ведущий лектор:

Бузенков И.И.. доцент, к.т.н.

(Ф.И.О., должность, учен. степень, учен. звание)

Одобрен на заседании кафедры

«01» сентября 2016 г. протокол № 1

Новороссийск

2016 год

СТРУКТУРА

конспекта лекций* по дисциплине Программируемые микроэлектронные

устройства

Лекция № 1

ТЕМА: Введение. Предмет и задачи дисцилины. Современный уровень микропроцессорной техники. Технико-экономические закономерности развития и совершенствования микропроцессорных систем и их влияние на развитие цифровых систем.

Основные вопросы, рассматриваемые на лекции:

1. Введение

2. Цели и задачи дисциплины

3. Современный уровень микропроцессорной техники.

4. Технико-экономические закономерности развития и совершенствования микропроцессорных систем и их влияние на развитие цифровых систем.

1. Цели дисциплины

Дисциплина “ Программируемые микроэлектронные устройства” обеспечивает базовую теоретическую и инженерную подготовку курсантов в области программируемых микроэлектронных устройств.

Она подготавливает студентов к освоению профилирующих дисциплин специальности, рассматривающих теорию и технику радиотехнических систем

2. Место дисциплины в структуре ООП

Дисциплина " Программируемые микроэлектронные устройства" относится к базовой части профессионального цикла ООП.

Перечень учебных дисциплин с указанием разделов (тем), усвоение которых студентами необходимо для изучения данной дисциплины:

- схемотехника;

- информатика и информационные технологии;

- электронные приборы;

- проблемно-ориентированные пакеты прикладных программ в радиотехнике;

- электротехника и электроника;

- радиотехнические цепи и сигналы;

- цифровая и статистическая обработка сигналов.

Иными словами, изучение дисциплины " Программируемые микроэлектронные устройства" необходимо для понимания принципов построения основных узлов радиоэлектронных устройств.

Общий алгоритм ПДП.

Для осуществления прямого доступа к памяти контроллер должен выполнить ряд последовательных операций:

- принять запрос (DREQ) от устройства ввода-вывода;

- сформировать запрос (HRQ) в процессор на захват шины;

- принять сигнал (HLDA), подтверждающий захват шины;

- сформировать сигнал (DACK), сообщающий устройству о начале обмена данными;

- выдать адрес ячейки памяти, предназначенной для обмена;

- выработать сигналы (MEMR, IOW или MEMW, IOR), обеспечивающие управление обменом;

- по окончании цикла DMA либо повторить цикл DMA, изменив адрес, либо прекратить цикл.

Формирование адреса памяти.

Контроллеры DMA обеспечивают формирование только 16 младших разрядов адреса памяти. Причем старшая часть адреса (А15-А8 для DMA1 или А16-А9 для DMA2) во время цикла DMA по шине данных поступает в регистр старшего адреса DMA и далее на шину адреса, а младшая часть адреса (А7-А0 для DMA1 или А8-А1 для DMA2) выдается на шину адреса непосредственно из контроллера. Восемь старших разрядов адреса памяти содержатся в регистре страниц DMA. Разряд А16 из регистра страниц DMA запрещается, когда выбран DMA2. Разряд A0 не связан с DMA2 и всегда содержит нуль при передаче слова.

Это означает, что:

- размер блока данных, который может быть передан или адресован, измеряется не байтами (8 бит), а словами (16 бит);

- слова всегда должны быть расположены на четной границе.

Таким образом, контроллер DMA и регистр страниц определяют 24-разрядный адрес, что обеспечивает передачу данных в пределах адресного пространства 16 М байт.

Регистры страниц.

Регистр страниц вместе с контроллерами DMA он определяет полный (24-разрядный) адрес для каналов DMA.

Адреса портов регистров страниц:

| Канал DMA | Адрес порта регистра страниц |

| 0 | 087h |

| 1 | 083h |

| 2 | 081h |

| 3 | 082h |

| 4 | - |

| 5 | 08Вh |

| 6 | 089h |

| 7 | 08Ah |

| Регенерация | 08Fh |

* Содержимое регистра страниц в целях регенерации должно быть равно 00h.

Адресация портов.

В таблице приведены адреса портов - регистров адреса ОП и управления/состояния контроллеров DMA, а также форматы регистров:

| Функции регистров | Формат | Адреса портов | Чтение/запись | |

| DMA1 | DMA2 | |||

| Регистр состояния (STAT) Read Status Register) | 8 | 008h | 0D0h | Чтение |

| Регистр команд (CR) (Write Command Register) | Запись | |||

| Регистр режима (MOD) (Write Mode Register) | 6 | 00Bh | 0D6h | Запись |

| Регистр режима (MOD)*** (Read Mode Register) | Чтение | |||

| Запись одиночных разрядов регистра маск (Write Single Mask Register) | 4 | 00Ah | 0D4h | Запись |

| Регистр команд (CR)*** (Read Command Register) | 8 | Чтение | ||

| Запись всех разрядов маски (Write Mask Register) | 4 | 00Fh | 0DEh | Запись |

| Регистр маски (MASK)*** (Read Mask Register) | Чтение | |||

| Программный регистр запросов (REQ)** Write Request Register) | 4 | 009h | 0D2h | Запись |

| Регистр запросов *** (Read Request Register) | Чтение | |||

| Базовый и текущий регистры адреса - канал 0 | 16 | 000h | 0C0h | Запись |

| Текущий регистр адреса канал 0 | 16 | 000h | 0C0h | Чтение |

| Базовый и текущий регистры cчетчика - канал 0 | 16 | 001h | 0C2h | Запись |

| Текущий регистр счетчика - канал 0 | 16 | 001h | 0C2h | Чтение |

| Базовый и текущий регистры адреса - канал 1 | 16 | 002h | 0C4h | Запись |

| Текущий регистр адреса - канал 1 | 16 | 002h | 0C4h | Чтение |

| Базовый и текущий регистры cчетчика - канал 1 | 16 | 003h | 0C6h | Запись |

| Текущий регистр счетчика - канал 1 | 16 | 003h | 0C6h | Чтение |

| Базовый и текущий регистры адреса - канал 2 | 16 | 004h | 0C8h | Запись |

| Текущий регистр адреса - канал 2 | 16 | 004h | 0C8h | Чтение |

| Базовый и текущий регистры cчетчика - канал 2 | 16 | 005h | 0CAh | Запись |

| Текущий регистр счетчика - канал 2 | 16 | 005h | 0CAh | Чтение |

| Базовый и текущий регистры адреса - канал 3 | 16 | 006h | 0CCh | Запись |

| Текущий регистр адреса - канал 3 | 16 | 006h | 0CCh | Чтение |

| Базовый и текущий регистры cчетчика - канал 3 | 16 | 007h | 0CEh | Запись |

| Текущий регистр счетчика - канал 3 | 16 | 007h | 0CEh | Чтение |

| Временный регистр данных(TR)** Read Temporary Register)¦ | 16 | 00Dh | 0DAh | Чтение |

| Общий сброс (Master Clear) | * | Запись | ||

| Сброс F/F(Clear Byte Pointer Flip-Flop) | * | 00Ch | 0D8h | Запись |

| Установка F/F *** (Set Byte Pointer Flip-Flop) | Чтение | |||

| Сброс регистра маски (Clear Mask Register) | * | 00Eh | 0DCh | Запись |

| Сброс счетчика MODE *** (Clear Mode Counter) | Чтение | |||

- * Это не регистры, а непосредственные команды для контроллера DMA.

- ** Эти регистры используются только в режиме ПАМЯТЬ-ПАМЯТЬ.

- *** Эти регистры и команды контроллера DMA не реализованы в контроллере 8237А и в "Периферийном контроллере" STC62C008, но реализованы в большинстве современных комплектов процессорных БИС.

Режимы обслуживания.

В активном цикле обслуживание подсистемы DMA возможно в одном из четырех режимов. Окончание обслуживания распознается по переходу регистра счетчика слов из 0000Н в FFFFН. При этом возникает сигнал окончания счета (TC), который может вызвать автоинициализацию, если она запрограммирована, или маскирование канала при ее отсутствии.

Одновременно с TC вырабатывается выходной сигнал -EOP. Во время автоинициализации первоначальные значения регистров текущего адреса и счетчика восстанавливаются из соответствующих базовых регистров. После автоинициализации канал готов выполнять другое обслуживание подсистемы DMA без вмешательства CPU, как только обнаружится достоверный DREQ.

Режим память-память

Этот режим предназначен для передачи блоков данных из одного адресного пространства памяти в другое с минимальными программными и временными затратами, но в PC AT не используется. В данном режиме могут работать только нулевой и 1-й каналы контроллера. Эта передача инициируется программной установкой REQ для канала 0. Адрес ячейки памяти-источника данных задают в CAR0, а ячейки-приемника - в CAR1. Байт данных, считанный из памяти, заносится во временный регистр (TR) и затем из TR считывается в ячейку-приемник. Когда значение счетчика слов канала 1 станет равным FFFFh, обслуживание заканчивается.

Типы передач.

Каждый из трех активных режимов предполагает выполнение трех различных передач. Это ЧТЕНИЕ, ЗАПИСЬ и ПРОВЕРКА. Передача ЧТЕНИЕ пересылает данные из памяти в периферийное устройство при активизации -MEMR и -IOW. Передача ЗАПИСЬ пересылает данные из периферийного устройства в память при активизации -MEMW и -IOR. ПРОВЕРКА - это псевдопередача.

Подсистема DMA осуществляет передачи ЧТЕНИЯ или ЗАПИСИ, генерируя адреса и реагируя на -EOP, но сигналы управления памятью и периферийными устройствами остаются не активными. Вход READY игнорируется в ПРОВЕРКЕ.

Приоритеты.

Подсистема DMA имеет два типа приоритета, которые можно установить программно. Первый из них - фиксированный приоритет, который фиксирует каналы в последовательности, соответствующей убыванию их номеров.

Низший приоритет имеет канал номер 3, а высший приоритет имеет канал 0.

После выбора какого-либо канала для обслуживания запрещается вмешательство остальных каналов до тех пор, пока обслуживание не завершится.

Второй тип приоритета - циклический. Последний обслуженный канал становится каналом с низшим приоритетом согласно циклу. При циклическом приоритете любое устройство, требующее обслуживания, непременно будет распознано после обработки максимум трех более приоритетных обслуживаний. Это исключает монополизацию всей системы одним каналом.

Регистры контроллера DMA.

Временный регистр (TR - 00D, 0DA)

Регистр используется для хранения данных в течение передачи ПАМЯТЬ-ПАМЯТЬ. После окончания передач последнее слово может быть считано микропроцессором.

Регистр всегда содержит последний байт, переданный в предыдущей операции ПАМЯТЬ-ПАМЯТЬ, если не сброшен по RESET.

Таблица 10.1

Таблица 10.2

Выбор регистрового банка

| RS 1 | RS 0 | Банк | Адрес |

| 0 | 0 | 0 | 00Н+07Н |

| 0 | 1 | 1 | 08Н+0FH |

| 1 | 0 | 2 | 10H+17H |

| 1 | 1 | 3 | 18H+1FH |

Указатель стека ( Stack Pointer – SP ). Регистр указателя стека имеет ширину 8 бит. Используется для указания на вершину стека в операциях записи в стек и чтения из него.

Он инкрементируется на единицу перед сохранением данных при выполнении команд PUSH и CALL. Неявно используется такими командами, как RET, RETI, POP.

Стек может находиться в любом месте внутренней памяти данных, однако указатель стека после сброса инициализируется с адреса 07Н (область стека в этом случае начинается с адреса 08Н).

Указатель данных ( Data Pointer – DPTR ). Регистр указателя данных DPTR состоит из старшего байта (DPH) и младшего байта (DPL). Его основная функция состоит в хранении 16-разрядного адреса. К нему можно обращаться, как к 16-разрядному регистру или как к двум независимыми 8-разрядным регистрам.

Порты P 0 – P 3. Функционально любой порт состоит из буфера и SFR - защелки. Соответственно P0, P1, P2, и P3 являются SFR - защелками портов 0, 1, 2, и 3.

Запись логической единицы в любой бит SFR - защелки порта (P0, P1, P2, или P3) вызывает появление высокого состояния на соответствующем выводе порта. Запись нуля вызывает появление низкого состояния.

Когда порт используется как вход, то внешнее состояние вывода порта сохраняется в SFR - защелке порта. То есть, если внешнее состояние вывода порта низкое, соответствующий бит SFR - защелки порта будет содержать 0; если внешнее состояние высокое, то бит будет содержать 1).

Буфер данных последовательного интерфейса ( Serial Data Buffer – SDB ). Последовательный буфер фактически состоит из двух отдельных регистров: буфера передачи и буфера приема.

При записи данных в SBUF они помещаются в буфер передатчика последовательного порта и сохраняются для последующей передачи. Запись байта в буфер передатчика приводит к автоматической инициализации начала передачи этого байта.

При чтении SBUF считывается содержимое буфера приемника последовательного порта. Наличие буферного регистра приемника позволяет совмещать операцию чтения из SBUF ранее принятого байта с приемом очередного. Если к моменту окончания приема очередного байта предыдущий не был считан из SBUF, то он будет потерян.

Основные регистры таймеров в 80C51. Регистровые пары (TH0, TL0) и (TH1, TL1) образуют 16 - разрядные счетные регистры для таймеров / счетчиков 0 и 1, соответственно.

Регистр управления в 80C51. Регистры специальных функций IP, IE, TMOD, TCON, SCON, и PCON содержат биты управления и состояния для системы прерываний, таймеров / счетчиков, и последовательного порта.

Микроконтроллер 80С51 имеет в своем составе четыре двунаправленных порта ввода-вывода P0, P1, P2 и P3. Каждый порт включает в себя защелку (Port Latch) порта (регистры специальных функций SFR от P0 до P3), выходной формирователь (Output Driver) и входной буфер порта (Input Buffer).

Выходные формирователи портов P0 и P2 и входные буферы порта P0 используются в обращениях к внешней памяти. В этом случае порт P0 служит как мультиплексируемая по времени шина адреса/данных. Он выставляет на шину младший байт адреса внешней памяти, а порт P2 выводит старший байт адреса внешней памяти (в том случае, если адрес 16-разрядный). В противном случае, на выводах порта P2 постоянно выводится содержимое регистра P2 из области SFR.

Все выводы порта P3 многофункциональны. Они являются не только выводами порта, но и имеют альтернативные функции, сведенные в таблицу 10.3.

Таблица 10.3

Таблица 10.3

Память данных (ОЗУ, 3RAM)

в отличие от памяти программ, адресное пространство памяти данных адресуется побайтно (а не пословно). Адресация полностью линейная, без какого-то деления на страницы, сегменты или банки, как это принято в некоторых других системах. Исключая некоторые младшие модели Tiny, объем встроенной SRAM колеблется от 128 байт (например, у ATtiny2313) до 4—8 кбайт у старших моделей Mega.

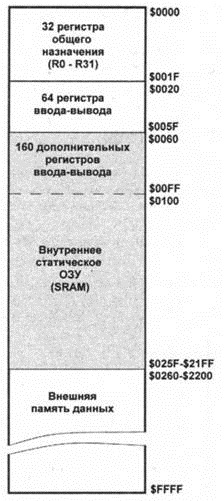

Адресное пространство статической памяти данных (SRAM) условно делится на несколько областей, показанных на рис. 18.10. К собственно встроенной SRAM относится лишь затемненная часть, до нее по порядку адресов расположено адресное пространство регистров, где первые 32 байта занимает массив регистров общего назначения (РОН), еще 64 — регистров ввода-вывода (РВВ).

Для некоторых моделей Mega (ATmega8515, ATmegal62, ATmegal28, AT-mega2560 и др.) предусмотрена возможность подключения внешней памяти объемом до 64 кбайт. Отметим, что адресные пространства РОН и РВВ не отнимают пространство у ОЗУ данньпс: так, если в конкретной модели МК имеется 512 байт SRAM, а пространство регистров занимает первые 96 байт (до адреса $60), то адреса SRAM займут адресное пространство от $0060 до $025F (то есть от 96 до 607 ячейки включительно). Конец встроенной памяти данных обозначается константой ramend. Следует учесть, что последние адреса SRAM, как минимум, на четыре—шесть ячеек от конца (в зависимости от количества вложенных вызовов процедур, для надежности лучше принять это число равным десяти или даже более) занимать данными не следует, так как они при использовании подпрограмм и прерываний заняты под стек.

Рисунок 11.2 - Адресное пространство статической памяти данных (SRAM) микроконтроллеров AVR

Операции чтения/записи в память одинаково работают с любыми адресами из доступного пространства, и потому при работе с SRAM нужно быть внимательным: вместо записи в память вы легко можете «попасть» в какой-нибудь регистр. Для обращения к РОН, как к ячейкам памяти, можно в качестве адреса подставлять номер регистра, а вот при обращении к РВВ таким же способом к номеру последнего нужно прибавлять $20. Следует также помнить, что по умолчанию при включении питания все РВВ устанавливаются в нулевое состояние во всех битах (единичные исключения все же имеются, поэтому в критичных случаях надо смотреть документацию), а вот РОН и ячейки SRAM могут принимать произвольные значения.

Умножитель-накопитель (MAC) сигнальных процессоров семейства ADSP2100

Основным устройством вычислительного блока MAC является аппаратный умножитель. Его входы называются X и Y. Разрядность входов умножителя равна 16. Так как в умножителях разрядность выходного слова определяется как сумма разрядностей входных слов, то выходная шина умножителя является32-разрядной. 32-разрядный результат поступает на вход 40-разрядного сумматора/вычитателя. Его выход подключен к 40-разрядному регистру-аккумулятору (накопителю). Так как сигнальный процессор AD21xx 16-разрядный, то 40-разрядный регистр для отображения в 16-разрядную память процессора разбивают на три регистра: 16-разрядный регистр младших бит MR0, 16-разрядный регистр старших бит MR1 и 8-разрядный регистр защитных бит MR2. Структурная схема MAC сигнальных процессоров семейства ADSP-2100 приведена на рисунке 13.3.

Рисунок 13.3 - Структурная схема MAC сигнальных процессоров семейства ADSP-2100

Сумматор/вычитатель и регистр MR обычно называется аккумулятором (накопителем). Разрядность аккумулятора выбирают больше 32 для того, чтобы предотвратить переполнение при выполнении нескольких операций умножителя-накопителя последовательно. Это обычно требуется при реализации цифрового фильтра с КИХ характеристикой. Восемь защитных бит обычно достаточно для реализации 200-отводного цифрового фильтра. Если при выполнении операции цифровой фильтрации возникает переполнение (число больше 40 разрядов), то устанавливается бит переполнения умножения MV (в этот бит записывается '1')

Регистры ввода/вывода MAC аналогичны регистрам ввода/вывода вычислительного блока АЛУ. Вход умножителя X может получать данные как из регистров MX, так и из регистров результата любого вычислительного блока процессора по Р-шине (шине результатов). MAC содержит два набора регистров MX: МХ0 и МХ1. Запись в эти наборы регистров и считывание из них может производиться по шине памяти данных ДПД. Выходы регистров MX двухпортовые, так что один регистр может осуществлять передачу данных в умножитель, в то время как данные из другого регистра будут записываться в память данных по шине ДПД.

На вход умножителя Y могут поступать данные как из регистров MY, так и из регистра обратной связи MF. Имеется два регистра MY: MY0 и MY1. Запись в эти регистры и считывание с них может производиться по шине ДПД, кроме того запись вних может быть произведена по шине ДПП. В наборе команд возможно также считывание данных из этих регистров по шине ДПП, но в этой операции используется устройство обмена данными между шинами ДПД и ДПП. Выходы регистров MY, как и MX двухпортовые, что позволяет одновременно осуществлять считывание данных из одного регистра MY в умножитель, а из другого сохранять данные в память процессора по шине ДПД.

Выход MAC подключается либо к регистру обратной связи MF, либо к регистру результата MR. Регистр обратной связи MF позволяет использовать биты результата 16-31 для входа Y данных в следующем машинном цикле. Как уже упоминалось выше, 40-разрядный регистр результата MR разделен на три части: MRO, MR1 и MR2. Каждый из этих регистров может загружаться с шины ДПД и передавать данные либо на шину ДПД, либо на Р-шину.

Запись и считывание из любого регистра умножителя-накопителя MAC может осуществляться в одном и том же цикле. Считывание данных из регистров происходит в начале цикла, а запись — в конце. Следовательно, при чтении из регистра считывается значение, загруженное в конце предыдущего цикла. Новое значение, записанное в регистр, невозможно считать до следующего цикла. Это позволяет считывать из регистра ввода операнд для умножителя в начале цикла и записывать новое значение данных из памяти сигнального процессора в конце этого же цикла. Это также позволяет сохранять предыдущее содержимое регистра результатов в памяти процессора и записывать в него очередной результат в течении этого же цикла.

MAC содержит два банка регистров MR, MF, MX, MY, теневые банки регистров показаны на рисунке 1 за основными регистрами. В любой момент времени доступен только один банк. Теневой ряд регистров может быть задействован для быстрого переключения между задачами. Новая задача, такая как подпрограмма обслуживания прерывания, может выполняться без сохранения текущего содержимого регистров в памяти сигнального процессора.

Выбор основного или теневого банка регистров выбирается битом 0 в регистре состояния режима процессора (MSTAT). Если этот бит равен 0, то выбран основной банк, если он равен 1, то — теневой банк регистров.

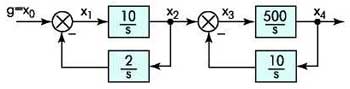

Пример синтеза аналогового устройства

Рассмотрим весьма простой пример синтеза принципиальной схемы аналогового устройства по модели, заданной системой дифференциальных уравнений в форме преобразований Лапласа вида: x0 = g, x1 = x0 - 2x2/s, x2 = 10x1/s, x3 = x2 - 10x4/s, x4 = 500x3/s.

| x1 | x2 | x3 | x4 | x5 |

| 1 |

| 1 | ||

| 10/s |  1 1

| |||

| 1 | 1 |

| ||

| 500/s |

|

Построим структурную матрицу этой системы дифференциальных уравнений и выделим стрелками матричные циклы:

По уравнениям и структурной матрице восстановим блок-схему устройства (рис.5). В соответствии со структурной матрицей система обладает двумя отрицательными обратными связями: узел 2 —> узел1 и узел 4 —> узел 3, соответственно. Поскольку структурная схема на рис.5 изначально построена на элементарных звеньях, ее можно рассматривать как функциональную схему электронного устройства.

Рисунок 16.5 - Структурная схема синтезируемого устройства (поэтапно)

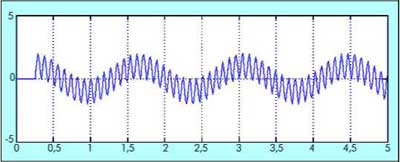

Из результатов моделирования (рис.6) синтезированной схемы видно, что при заданных параметрах она представляет собой два последовательно соединенных генератора. То есть весьма простое устройство, состоящее всего из четырех интегрирующих звеньев, выполняет сравнительно сложную функцию модуляции низкочастотного колебания высокочастотным.

Отметим, что при проектировании и производстве МАБИС и ПА-ИС совершенно не обязательно использовать аппаратные аналоги элементарных звеньев, выполненные на операционных усилителях, как на рис.4, хотя в этом базисе они лучше всего проработаны. Наиболее перспективна реализация аппаратных аналогов элементарных звеньев на оптоэлектронных компонентах, хотя возможны и любые другие варианты.

Рисунок 16.6 - Осциллограмма синтезированного устройства

Универсальные МАБИС и ПАИС

Таким образом, можно выделить пять элементарных (простейших) компонентов любой РЭА, соответствующих основным операторам систем дифференциальных уравнений: умножения, дифференцирования, интегрирования, сложения и размножения (мультиплексирования). Методика проектирования аналоговых электронных устройств предполагает:

• использование в качестве исходных данных для проектирования математической модели в виде системы из n дифференциальных уравнений первого порядка (или дифференциального уравнения л-го порядка;

• построение структурной матрицы проектируемого устройства и нахождение матричных циклов;

• восстановление структурной схемы проектируемого устройства;

• преобразование структурной схемы в функциональную путем замены типовых звеньев совокупностью элементарных звеньев;

• преобразование функциональной схемы проектируемого устройства в схему электрическую принципиальную путем замены элементарных звеньев эквивалентными им аппаратными базисными элементами (возможно, применение современных САПР позволит избежать этот этап, синтезируя топологию непосредственно из функционального описания);

• разработка топологии проектируемого устройства.

Предлагаемый подход обладает рядом решающих преимуществ. Так, функциональная схема проектируемого устройства синтезируется из исходной системы дифференциальных уравнений путем стандартных матричных преобразований, которые могут быть упорядочены и преобразованы в алгоритм для автоматических вычислений. Схема электрическая принципиальная синтезируется из функциональной схемы простой заменой элементарных динамических звеньев эквивалентными им базисными элементами. Также существенно может упроститься моделирование устройства средствами САПР.

Таким образом, поскольку множество элементарных звеньев не многочисленно, появляется реальная возможность проектирования универсальных МАБИС и ПАИС. Что, в свою очередь, значительно упрощает проектирование аналоговых и цифроаналоговых устройств и открывает заманчивые перспективы дальнейшего развития электроники в целом.

Лекция № 17

ТЕМА: Применение современных средств САПР для ПЛИС. Единый базис проектирования ПЛИС и МАБИС.

Основные вопросы, рассматриваемые на лекции:

1. Применение современных средств САПР для ПЛИС

2. Единый базис проектирования ПЛИС и МАБИС

3. Основные производители САПР для ПЛИС

4. Разновидности САПР для ПЛИС

На современном уровне развития ПЛИС проектирование цифровых устройств в данном базисе трудно себе представить без применения средств САПР. При этом как САПР ПЛИС, так и любые другие САПР имеют ряд особенностей, выделяющие их из ряда прочих программных продуктов:

объем систем проектирования (миллионы строк исходного кода на языках высокого уровня);

наукоемкость программных продуктов. Предметными областями САПР, как правило, являются интенсивно развивающиеся отрасли науки и техники. При этом программное обеспечение выступает как инструмент исследования предметной области;

длительность сроков разработки программного обеспечения. Сроки разработки, эксплуатации и модернизации отдельных продуктов составляют десятки лет.

При этом надо отметить - программное обеспечение8 применяемое при разработке цифровых устройств, быстро морально устаревает вследствие

высоких темпов развития элементной базы, результатом чего является необходимость его модернизации. Данное утверждение полностью правомерно и но отношению к САПР ПЛИС Так, на данный момент, в современных коммерческих САПР ПЛИС хорошо отработаны методы получения конфигурации ПЛИС по моделям устройств на уровне регистровых передач. Однако современные устройства ПЛИС обладают такой логической емкостью, что позволяют проектировать целые системы на. одном кристалле, и соответственно для проектирования систем необходимо применять средства проектирования на системном уровне. В настоящее время нет однозначной, удовлетворяющей всех разработчиков аппаратуры. методологии получения конфигурации ПЛИС по функциональной модели устройства на системном уровне.

Наиболее популярным подходом по решению данной проблемы является применение технологии ІР-ядср (Intellectual property - Cores). IP-ядра - это готовые компоненты, позволяющие легко включать их в собственный проект для создания более сложной системы, У данного подхода есть один существенный недостаток - привязанность ІР-ядср к элементному базису. Каждое IP-ядро оптимизировано под конкретную серию микросхем конкретного производителя, что существенно ухудшает возможность переноса уже созданных устройств из одного элементного базиса в другой[33,90].

Закрытость архитектур коммерческих САПР делает невозможным добавление собственных функциональных моделей устройств на системном уровне для получения на их основе моделей усіройства на уровне регистровых передач.

Другой популярный подход, позволяющий осуществить переход от

функциональной модели на системном уровне к модели устройства на уровне

регистровых передач — применение языков описания аппаратуры на системном

уровне (SLDLs, system-level design languages). К таким языкам относятся

SystemC,. Handel-C, Open Vera- Основным недостатком данного подхода

является ограниченность групп алгоритмов, которые возможно применять для осуществления данного перехода, следствием чего является снижение качества получаемого решения (по сравнению с технологией IP-ядер). Однако его несомненным плюсом является независимость от аппаратного базиса, в котором будет ре&іизовано устройство.

Таким образом, с одной стороны, при применении технологии 1Р-ядер разработчик аппаратуры получает качественное решение, но жестко привязанное к аппаратному базису, в котором реализуется усіройство. С другой стороны, при применении языков описания аппаратуры на системном уровне реализация устройства является аппаратно независимой, но при этом теряется качество получаемого решения (в сравнении с технологией ІР-ядер). Из выше сказанного следует, что в настоящее время актуальным является решение задачи автоматизации перехода. от функциональной модели устройства на системном уровне к его модели па уровне регистровых передач и создание подсистемы, САПР, открытой по отношению к модернизации и расширению, позволяющей решать данную задачу.

днако в настоящий момент у большинства разработчиков систем САПР хорошо отработан процесс получения конфигурации устройства по его описанию на уровне регистровых передач, но до сих. пор разработчики аппаратуры сталкиваются с рядом проблем при попытке получить описание. устройства на уровне регистровых передач на основании его функциональной модели на системном уровне.

Далее рассмотрим коммерческие САПР цифровых устройств и методы получения описания устройства на уровне регистровых передач по его функциональной модели на системном уровне. При этом акцентируем свое внимание на том, как в этих системах при разработке устройства в базисе ПЛИС решается проблема перехода от функциональной моделей устройства на системном уровне к его модели на уровне регистровых передач.

САПР "MAX+PLUSir фирмы ALTERA поддерживает цикл проектирования ПЛИС для кристаллов этой же фирмы, однако только лишь для проектов, в которых проектируемое устройство описано на уровне регистровых передач. Эта система работает на PC платформе и рабочих станциях. САПР предоставляет разнообразные средства входного описания,, включая интерфейсы со стандартными языками и наиболее распространенными пакетами и обеспечивая эффективные алгоритмы синтеза, позволяющие максимально использовать ресурсы кристалла, временной и функциональный анализ разработанного устройства. Используется для проектирования микросхем всех семейств фирмы, таких, как MAX70G0, MAX900G, FLEX8000, FLEX10K.

MAX+PLUSII ориентирован на сопряжение со стандартами VHDL, EDIF, Verilog. Любая конфигурация САПР импортирует входные данные в формате EDIF и формирует результаты проектирования во всех перечисленных форматах. ALTERA обеспечивает библиотеками САПР таких фирм, как Mentor Graphics, Cadence, Viewlogic и Synopsys. Имеются библиотеки IP-ядер.

Последняя версия 10.0 MAX+PLUS II реализуется с октября 2000г. С октября 2000г. фирма выпустила новый программный продукт "Quartus". Данный пакет ориентирован на самые мощные новые кристаллы фирмы семейства APEX, Stratix и обладает всеми" чертами, присущими MAX+PLUSII.

Фирма Xilinx — разработчик ПЛИС - поставляет также САПР для разработки устройств на FPGA и CPLD. С 1996г. Xilinx выпустила ПО Foundation Series, охватывающее все этапы разработки ПЛИС. В новых версиях ПО поддерживаются расширенные библиотеки IP-ядер, которые становятся очень важными при создании проектов больших размеров, сокращают сроки и упрощают проектирование. Имеются UNISIM-библиотеки для функционального моделирования с VHDL и Verilog, также в САПР фирмы включен набор библиотек для временного моделирования,

В настоящее время Xilinx выпустила свою последнюю версию Foundation Series 4.2І. Эта САПР позволяет в два раза сократить время компиляции проекта, появились новые средства трассировки и размещения, включена новая версия программы синтеза Express 3.6. На данный момент Foundation Series больше не развивается в связи с чем, что фирма Xilinx порвала отношения с производителем программы синтеза фирмой Synopsys. Поэтому рекомендуется для новых разработок применять новую САПР ISE[I5,82] Эта САПР позволяет выполнять полный маршрут проектирования для новых кристаллов фирмы: это наиболее мощные и быстрые кристаллы семейства Virtcx-11, Viriex-11 Pro, дешевые кристаллы семейства Spartan-II, Spartan-III и кристаллы с малым потреблением CoolRimner. Кроме того, данная САПР поддерживает интеграцию с системами Synplify, LeonardoSpectrum и Modelsim. Так же в настоящее время фирма ХІІІпх выдвинула на рынок свой новый продукт -Embedded Development Kit, предназначенный для построения систем на основе их функциональных моделей на системном уровне. Данный продукт при реализации систем в кристалле опирается на библиотеки ІР-ядер. А также позволяет создавать проекты, содержащие одновременно как описание аппаратуры, так и программную часть. В настоящее время это становится актуально в связи с выходом новой серии кристаллов Virtex-II Pro, содержащих интегрированные процессорные ядра. Так же для перехода от функциональных моделей на системном уровне к реализации в кристалле, фирма Xiliiix предлагает библиотеку расширения для MatLab. В данном подходе реализация в кристалле получается при помощи применения библиотеки ІР-ядер.

Фирмой Xilinx совместно с фирмой ELANIX разработан новый подход к проектированию устройств обработки сигналов - на основе комбинации САПР системного уровня System View фирмы ELANIX с ІР-ядрами, оптимизированными для эффективной реализации в ПЛИС Xilinx. Таким образом, цифровое устройство может быть моделировано, оптимизировано и реализовано в ПЛИС с помощью библиотек ІР-ядер.

То есть можно сделать вывод, что в САПР фирмы Xilinx для осуществления перехода от функциональных моделей па системном уровне к моделям на уровне регистровых передач доминирует подход на основе ІР-ядер. Фирма CADENCE, многие годы занимающаяся разработкой САПР в области электроники, расширяется за счег приобретения множества более мелких компаний; годовой объем продаж достиг 1.3 млрд. долларов в 2003г. Основные направления развития связаны со следующими базовыми конфигурациями системы: — проектирование на системном уровне (system-level design); — функциональная верификация (functional verification); — эмулляция и ускорители решений (emulation and acceleration); — средства синтеза от верхних уровней до размещения и трассировки (synthesis/piace-and-route); — средства проектирования аналоговых, высокочастотных и смешанных схем (analog, radio frequency, and mixed-signal design); — проектирование топологии интегральных схем (custom 1С layout); — анализ и верификация на физическом уровне (physical verification and analysis); — проектирование и корпусирование микросхем (1С packaging); — проектирование печатных плат (РСВ design). Основные системы CADENCE для решения задач по направлениям: Virtuoso Custom Designer - это набор средств САПР для проектирования заказных ИС. Это полностью автоматизированный процесс проектирования на уровне приборов и ячеек, включая средства верификации, размещения и трассировки, CADENCE SP&R - это система сквозного синтеза от регистрового уровня или уровня затворов до формирования GDSII-файла после реализации размещения и трассировки на основе синтеза, CADENCE AMS Designer реализует маршрут проектирования эффективного решения задач проектирования систем на кристалле, в том числе и для смешанных аналого-цифровых систем. CADENCE Wireless Solution содержит высоко интегрированный набор программ, который поддерживает быстрое проектирование от концепции решения до реализации в микросхемах. Система обеспечена большим числом библиотек всех основных мировых стандартов, включая 3GPP, CDMA2000, Bluetooth, 802.11 и др. Signal Processing Worksystcm позволяет ускорить процесс проектирования сложных алгоритмически цифровых сигнальных процессоров. SPW поддерживается большим набором библиотек и позволяет от алгоритмического уровня перейти к реализации в ASIC или FPGA, NC-SIM - это один из самых быстрых пакетов моделирования на основе языков описания аппаратуры Verilog и VHDL. Основное его преимущество — это работа одновременно с двумя стандартными языками.

Как было показало выше, основным узким местом в маршруте проектирования цифровых устройств е базисе ПЛИС является переход от разряботанной функциональной модели устройства на системном уровне к его модели на уровне регистровых передач (оптимизированной для заданного элементного базиса).

На сегодняшний день наиболее развитым подходом, покрывающим данный этап, является проектирование устройств и систем на основе ІР-ядер. ІР-ядра - это готовые компоненты, позволяющие легко включать их в собственный проект для создания более сложной системы. Например, ІР-ядром может быть интерфейс соединения с компьютером РСІ или USB, быстрое преобразование Фурье, голосовой кодек. Этот подход реатизован практически во всех современных системах САПР, Основным недостатком данного подхода является привязанность ядер к конкретным семействам кристаллов, т.е. при необходимости смены аппаратного базиса возникает необходимость в получении новых IP-ядер оптимизированных под него. К тому же никто не гарантирует, что IP-ядра, реализующие те же самые функции для новой элементной базы, будут сохранять свои старые интерфейсы, т.е,. встает проблема повторного связывания набора IP-ядер оптимизированного под новую элементную базу.

Так же в настоящее время ведутся активные разработки по получению описания схемы на уровне регистровых передач, исходя из ее описания на таких языках, как SystemC, Handel-C и др.» которые относят к семейству SLDL (system-level design languages), т.е. на языках поведенческого описания приближенных к аппаратным. Здесь лидирующие позиции занимает фирма SYNOPSYS. Однако набор алгоритмов, которые возможно перевести с SLDL языков на уровень регистровых передач, ограничен следующими правилами: 1. В программе может использоваться любое число простых переменных и переменных с индексами. 2. Единственным типом исполнительного оператора может быть оператор присваивания, правая часть которого есть арифметическое выражение; допускается любое число таких операторов. 3. Все повторяющиеся операции описываются только с помощью цикла с указанием границ изменения параметра; структура вложенности циклов может быть произвольной; шаги изменения параметров циклов всегда равны +1; если у цикла нижняя граница больше верхней, то цикл не выполняется.. 4. Допускается использование любого числа условных и безусловных операторов перехода, передающих управление «вниз» по тексту; не допускается использование побочных выходов из циклов. 5. Все индексные выражения переменных, границы изменения параметров и условия передачи управления задаются в общем случае, неоднородными формами, линейными как по параметрам циклов, так и по внешним переменным программы; все коэффициенты лилейных форм являются целыми числами. 6. Внешние переменные программы всегда целочисленные, и вектора их значений принадлежат некоторым целочисленным многоіранникам; конкретные значения внешних переменных известны только перед началом работы программы и неизвестны в момент её исследования.

Уместно сделать одно замечание относительно терминологии. Обычно под переменной с индексами понимается весь массив простых переменных, объединённых общим идентификатором. При изучении тонкой структуры программы такая «групповая» переменная очень неудобна. Гораздо удобнее рассматривать массив как группу простых переменных, идентификаторы которых составлены из идентификатора массива и индексов. Таким образом, работа с массивом сводится к работе с группой нумерованных переменных. Что резко сужает возможность применения данных методов из за снижения качества получаемого решения.

С другой стороны, разрабатываемое устройство мы можем представить в виде множества простейших компонентов, являющихся аппаратно зависимыми (регистры, очереди, сумматоры и т.д и построенных на их основе более сложных компонентов (фильтр, кодер, декодер и т.д.). Такое разбиение устройства правомерно, т.к. из алгебры логики известно, что в случае если множество простейших компонентов является функционально полной системой, то через его элементы можно выразить любую логическую функцию.

В случае, если разрабатываемое устройство строится на основе данного множества, мы получаем, что только лишь компоненты в него входящие являются зависимыми от конкретного базиса, в котором будет реализовано данное устройство. Описание самого устройства опирается уже на данное множество примитивов, что делает его независимым от базиса, в котором оно будет реализовано. Так же на основе данного множества можно реализовывать и аппаратно независимые IP ядра независимых примитивов В случае смены аппаратного базиса достаточно перенести в него множество аппаратно зависимых примитивов, при этом не трогая описания всего устройства в целом, что дает существенный выигрыш данного подхода по сравнению с двумя предыдущими. Так получаемое в данном случае решение по качеству эквивалентно решению, получаемому при применении технологии IP-ядер, при одновременной простоте переноса разработанного устройства из одного элементного базиса в другой.

В настоящее время данный подход не нашел применения в коммерческих системах САПР, но был применен при построении некоммерческих систем: так профессор Christoph Wolinski из Los Alamos National Laboratory применил данное представление устройства для построения автоматизированной системы проецирования реконфигурируемых вычислителей.

В качестве входного языка системы был выбран Java. Описание внутренней структуры проектируемого устройства производилось в виде набора Java объектов, а связи между объектами устанавливались посредством вызова соответствующих методов объектов. То есть для работы с данной системой от конечного пользователя необходимо знание Java и соответственно умение программировать на нем. Так же, как показало более детальное рассмотрение данной методологии, описание схемы оказывается очень громоздким, так как необходимо прописать каждую связь между внутренними объектами проектируемого устройства. Однако было бы логичней указывать узлы подключения каждого объекта, входящего в состав устройства,. что существенно сократило бы его входное описание в связи с тем, что обычно количество узлов в схеме существенно меньше количества связей между ее отдельными элементами (в худшем случае количество связей и узлов в схеме равны). С этой точки зрения наиболее удобным является описание устройства на SPICE подобном языке.

Как известно, качество получаемого решения при реализации устройства в ПЛИС можно определить по следующим критериям: площадь, занимаемая в кристалле, максимальная частота функционирования, время, затраченное на разработку.

Таблица 17.1

САПР фирм – производителей кристаллов ПЛИС

Таблица 17.2

Общецелевые САПР независимых разработчиков

КОНСПЕКТ ЛЕКЦИЙ

Направление подготовки

(специальность) Техническая эксплуатация транспортного

25.05.03 радиооборудования

код ОКСО наименование

Ведущий лектор:

Бузенков И.И.. доцент, к.т.н.

(Ф.И.О., должность, учен. степень, учен. звание)

Одобрен на заседании кафедры

«01» сентября 2016 г. протокол № 1

Новороссийск

2016 год

СТРУКТУРА

конспекта лекций* по дисциплине Программируемые микроэлектронные

устройства

Лекция № 1

ТЕМА: Введение. Предмет и задачи дисцилины. Современный уровень микропроцессорной техники. Технико-экономические закономерности развития и совершенствования микропроцессорных систем и их влияние на развитие цифровых систем.

Основные вопросы, рассматриваемые на лекции:

1. Введение

2. Цели и задачи дисциплины

3. Современный уровень микропроцессорной техники.

4. Технико-экономические закономерности развития и совершенствования микропроцессорных систем и их влияние на развитие цифровых систем.

1. Цели дисциплины

Дисциплина “ Программируемые микроэлектронные устройства” обеспечивает базовую теоретическую и инженерную подготовку курсантов в области программируемых микроэлектронных устройств.

Она подготавливает студентов к освоению профилирующих дисциплин специальности, рассматривающих теорию и технику радиотехнических систем

2. Место дисциплины в структуре ООП

Дисциплина " Программируемые микроэлектронные устройства" относится к базовой части профессионального цикла ООП.

Перечень учебных дисциплин с указанием разделов (тем), усвоение которых студентами необходимо для изучения данной дисциплины:

- схемотехника;

- информатика и информационные технологии;

- электронные приборы;

- проблемно-ориентированные пакеты прикладных программ в радиотехнике;

- электротехника и электроника;

- радиотехнические цепи и сигналы;

- цифровая и статистическая обработка сигналов.

Иными словами, изучение дисциплины " Программируемые микроэлектронные устройства" необходимо для понимания принципов построения основных узлов радиоэлектронных устройств.

Место микропроцессоров в классификации цифровых устройств.

Стремительное развитие цифровых методов обработки информации обусловлено успехами интегральной технологии, позволяющей изготавливать на сегодняшний день цифровые микросхемы, содержащие сотни тысяч и даже миллионы логических элементов в одном кристалле. Использование микросхем повышенной степени интеграции позволяет существенно улучшить основные технико-экономические характеристики цифровой аппаратуры в целом и измерительной в частности. Во-первых, значительно уменьшается число внешних соединений в аппаратуре из-за большей функциональной сложности самих микросхем. Поскольку в микроэлектронной аппаратуре внешние соединения являются одной из основных причин ее отказов, то их уменьшение при использовании микросхем повышенной степени интеграции позволяет повысить надежность аппаратуры. Во-вторых, сокращается общая длина соединений между элементами. Задержка сигнала на каждые 30 см соединений равна 1 нс. Отсюда следует, что создание устройств со сверхвысоким быстродействием принципиально возможно только на базе микросхем повышенного уровня интеграции, в которых общую длину межсоединений между соседними функциональными элементами можно довести до величины, не превышающей 1 см, что обеспечивает задержку распространения сигнала между элементами не более 0,03 нс. Кроме того, микросхемы повышенного уровня интеграции имеют по сравнению с микросхемами малого уровня интеграции меньшие размеры и более низкую стоимость в расчете на один функциональный элемент. Аппаратура, построенная на микросхемах высокой степени интеграции, является энергоэкономичной, что не маловажно при эксплуатации устройств с автономным электропитанием.

Отмеченные преимущества стали причиной активного развития технологии иготовления микросхем повышенного уровня интеграции (микросхем БИС и СБИС) в начале 70-х годов прошлого века. Однако появление БИС и СБИС на начальном этапе поставило поблемы перед разработчиками микросхем и аппаратуры на их основе. Дело в том, что на начальном этапе БИС и СБИС были узкоспециализированными и представляли собой устройства жесткой логики с неизменяемыми структурой и функциональностью. По этой причине выпуск таких микросхем оставался небольшим и их себистоимость была высока из-за больших первоначальных затрат, обусловленных разработкой их логической структуры, изготовлением фотошаблонов и технологической подготовкой производства при малых объемах выпуска. Решение проблемы было достигнуто разработкой БИС, функции которых задаются путем подачи внешних электрических сигналов, изменяющихся по определенной программе. Такие БИС получили название микропроцессоров.

Микропроцессор - это программно-управляемое устройство, предназначенное для обработки цифровой информации и управления процессом этой обработки, выполненное в виде одной или нескольких БИС. Качественным отличием микропроцессора от других типов микросхем является возможность их функциональной перестройки путем изменения внешней программы. В зависимости от программы микропроцессор может быть использован для решения самых разных задач и в этом способен заменить многие типы интегральных схем с "жесткой" логикой. Подобная универсальность микропроцессоров обусловила массовость их выпуска, что привело к снижению их стоимости, в результате чего экономически выгодным стало их использование в электронной аппаратуре. Создание дешевых микропроцессоров с широкими функциональными возможностями обеспечило дополнительные преимущества цифровым методам обработки информации, что стимулировало их внедрение в такие отрасли, как телефония, радиосвязь, измерительная техника.

Место микропроцессоров в классификации цифровых устройств приведено на рисунке 1.1.

Рисунок 1.1 - Место микропроцессоров в классификации цифровых устройств.

Однако при создании цифровых устройств на микропроцессорах особенности решаемой задачи накладываются на архитектуру конкретного класса микропроцессоров. Рассмотрим основные задачи, которые приходится решать при обработке сигналов (вне зависимости от аналоговой или цифровой реализации схемы):

1. суммирование нескольких сигналов;

2. перенос спектра сигналов;

3. фильтрация сигналов;

4. вычисление спектра сигнала (быстрое преобразование Фурье);

5. помехоустойчивое кодирование (подавление шума для аналоговых систем связи);

6. формирование кадров (только для цифровых систем связи)

7. скремблирование сигнала (формирование одинаковой вероятности передачи нулей и единиц)

Микропроцессорные средства выпускаются промышленностью в

виде наборов микросхем (chip-set) совместимых по уровням напряжения питания, сигналам и представлению информации, включающих МП, микросхемы оперативной и постоянной памяти, управления вводом/выводом, генератора тактовых сигналов и др.

Микропроцессоры (микропроцессорные средства) служат основой

для создания различных универсальных и специализированных микро-ЭВМ, микропроцессорных информационно-управляющих систем, программируемых микроконтроллеров, разнообразных микропроцессорных приборов и устройств контроля, управления и обработки данных.

Микро-ЭВМ или микрокомпьютером называют устройство об-

работки данных, содержащее один или несколько микропроцессоров,

БИС постоянной и оперативной памяти, БИС управления вводом и вы-

водом информации и некоторые другие схемы. Микрокомпьютер такого состава иногда называют «голым» из-за отсутствия в нем периферийных устройств (внешних ЗУ и устройств ввода и вывода информации). Микрокомпьютеры в такой конфигурации часто применяют в качестве встраиваемых в различные станки, машины, технологические процессы управляющих устройств (контроллеров).

Микрокомпьютеры широкого назначения, используемые для вы-

полнения вычислительных работ, управления сложными технологическими процессами, оснащаются необходимыми периферийными устройствами (дисплеями, печатающими устройствами, ЗУ на гибких дисках, аналого-цифровыми и цифроаналоговыми преобразователями и др.).

Микропроцессорной системой (МП-системой) обычно называют

специализированную информационную или управляющую систему,

построенную на основе микропроцессорных средств.

Микрокомпьютер с небольшими вычислительными ресурсами и

упрощенной системой команд, ориентированный не на производство вычислений, а на выполнение процедур логического управления различным оборудованием, называют программируемым микроконтроллером или просто микроконтроллером.

Логическая организация (архитектура) микропроцессоров (микро-

процессорных средств) ориентирована на достижение универсальности

применения, высокой производительности и технологичности.

Универсальность МП (микропроцессорных средств) определяется

возможностью их разнообразного применения и обеспечивается про-

граммным управлением МП, позволяющим производить программную

настройку МП на выполнение определенных функций, магистрально-

модульным принципом построения, а также специальными аппаратур-

но-логическими средствами: сверхоперативной регистровой памятью,

многоуровневой системой прерывания, прямым доступом к памяти,

программно-настраиваемыми схемами управления вводом/выводом и

т. п. Относительно высокая производительность МП достигается ис-

пользованием для их построения быстродействующих больших и

сверхбольших интегральных электронных схем и специальных архи-

тектурных решений, таких как стековая память, разнообразные спосо-

бы адресации, гибкая система команд (или микрокоманд) и др.

Технологичность микропроцессорных средств обеспечивается мо-

дульным принципом конструирования, который предполагает реализацию этих средств в виде набора функционально законченных БИС, просто объединяемых в соответствующие вычислительные устройства,

машины и комплексы.

Высокая универсальность и гибкость МП, достигаемая благодаря

программному управлению, низкая стоимость, небольшие размеры,

повышенная надежность, возможность встраивания микропроцессор-

ных средств в приборы, машины и технологические процессы, обеспе-

чивают микропроцессорам исключительно широкое применение в раз-

личных управляющих и обрабатывающих данные цифровых устройст-

вах и системах.

Использование микропроцессоров приводит к изменению характе-

ра проектной работы разработчика устройств и систем автоматики: во

многих случаях проектирование схем заменяется разработкой про-

грамм настройки микропроцессорной аппаратуры на выполнение оп-

ределенных функций.

При разработке средств микропроцессорной техники нашли даль-

нейшее, более глубокое развитие следующие принципы: модульность;

магистральность; микропрограммируемость; регулярность структуры.

Модульная организация предполагает построение систем на ос-

нове набора модулей конструктивно, функционально и электрически

законченных устройств, позволяющих самостоятельно или в совокупности с другими модулями решать вычислительные или управленче-

ские задачи определенного класса.

Модульный подход способствует стандартизации элементов все

более высоких уровней и сокращению затрат на проектирование систем, а также упрощает наращивание мощности и реконфигурацию систем, отодвигает время морального старения технических средств.

Многофункциональность (универсальность) и специализация мо-

дулей – эти два противоположных качества придаются модулям в про-

цессе компромиссных решений для различных классов систем, исходя

из обеспечения соответствия структуры системы характеру выполняе-

мых задач.

Целесообразно создавать системы в виде совокупности много-

функциональных и специализированных модулей, проблемно и функ-

ционально ориентированных в рамках определенных классов задач, ал-

горитмов, функций.

Магистральность – способ обмена информацией внутри модулей

и между модулями с помощью упорядоченных связей (в отличие от

произвольных связей, реализующих принцип «каждый с каждым»),

минимизирующий число связей. Обмен осуществляется с помощью

общих магистралей (шин), объединяющих входные и выходные линии

отдельных элементов и модулей. Магистральность – один из способов

обеспечения регулярности структуры системы и стандартизации ин-

терфейсов. С технической точки зрения – это способ обмена в виде

создания специальных двунаправленных буферных каскадов с тремя

устойчивыми состояниями и использования временного мультиплек-

сирования каналов обмена.

Микропрограммируемость – способ организации управления,

позволяющий осуществить проблемную ориентацию системы. Микро-

программируемость повышает гибкость устройств (за счет возможно-

сти смены микропрограмм), увеличивает регулярность их структуры

(за счет широкого использования матричных структур типа памяти),

повышает надежность устройств (за счет применения серийно освоен-

ных БИС памяти), упрощает контроль функционирования устройства

(за счет того, что контроль блока микропрограммного управления сво-

дится, по существу, к контролю содержимого ЗУ).

Регулярность структуры – предполагает закономерную повто-

ряемость элементов структуры и связей между ними; регулярность

структуры системы следует рассматривать на различных уровнях еѐ

организации.

В целом можно отметить, что МП как программируемое цифровое

устройство обработки информации характеризуется следующими по- казателями и связями их с внутренней и внешней структурой МП: разрядность; емкость адресуемой памяти; универсальность (специализация); число внутренних регистров; магистральность; микропрограммное управление; возможность и количество уровней прерывания; наличие стековой организации памяти и количество стековых регистров: наличие и состав резидентного и кросс-программного обеспечения.

Микропроцессорная автоматическая система (МПАС) – это ав-

томатическая система со встроенными в нее средствами микропроцес-

сорной техники (МТ).

Лекция № 2

ТЕМА: Классификация микропроцессоров. Многофункциональность и проблемная ориентация микропроцессорных систем

Основные вопросы, рассматриваемые на лекции:

1) Классификация микропроцессоров.

2) Построение микропроцессорных систем.

3) Многофункциональность и проблемная ориентация микропроцессорных систем

Микропроцессор - это программно-управляемое устройство, предназначенное для обработки цифровой информации и управления процессом этой обработки, выполненное в виде одной или нескольких БИС. Качественным отличием микропроцессора от других типов микросхем является возможность их функциональной перестройки путем изменения внешней программы. В зависимости от программы микропроцессор может быть использован для решения самых разных задач и в этом способен заменить многие типы интегральных схем с "жесткой" логикой. Подобная универсальность микропроцессоров обусловила массовость их выпуска, что привело к снижению их стоимости, в результате чего экономически выгодным стало их использование в промышленной автоматике, транспорте, бытовой технике и т.д. Создание дешевых микропроцессоров с широкими функциональными возможностями обеспечило дополнительные преимущества цифровым методам обработки информации, что стимулировало их внедрение в такие отрасли, как телефония, радиосвязь, измерительная техника.

Существует множество классификационных признаков микропроцессоров, вплоть до их поколений. Отметим лишь те признаки, которые исторически сформировались как основные и отражают состояние микропроцессорной техники на современном этапе.

По числу больших интегральных схем (БИС) в микропроцессорном комплекте различают однокристальные, многокристальные и многокристальные секционные микропроцессоры.

Процессоры даже самых простых ЭВМ имеют сложную функцио-

нальную структуру, содержат большое количество электронных элементов и множество разветвленных связей. Изменять структуру процессора необходимо так, чтобы полная принципиальная схема или ее части имели количество элементов и связей, совместимое с возможностями БИС. При этом микропроцессоры приобретают внутреннюю магистральную архитектуру, т. е. в них к единой внутренней информационной магистрали подключаются все основные функциональные блоки (арифметико-логический, рабочих регистров, стека, прерываний, интерфейса, управления и синхронизации и др.).

Для обоснования классификации микропроцессоров по числу БИС

надо распределить все аппаратные блоки процессора между основными тремя функциональными частями: операционной, управляющей и интерфейсной. Сложность операционной и управляющей частей процессора определяется их разрядностью, системой команд и требованиями к системе прерываний; сложность интерфейсной части разрядностью и возможностями подключения других устройств ЭВМ (памяти, внешних устройств, датчиков и исполнительных механизмов и др.).

Интерфейс процессора содержит несколько десятков информационных

шин данных (ШД), адресов (ША) и управления (ШУ). Однокристальные микропроцессоры получаются при реализации всех аппаратных средств процессора в виде одной БИС или СБИС (сверхбольшой интегральной схемы). По мере увеличения степени интеграции элементов в кристалле и числа выводов корпуса параметры однокристальных микропроцессоров улучшаются. Однако возможности однокристальных микропроцессоров ограничены аппаратными ресурсами кристалла и корпуса. Для получения многокристального микропроцессора необходимо провести разбиение его логической структуры на функционально законченные части и реализовать их в виде БИС (СБИС). Функциональная законченность БИС многокристального микропроцессора означает, что его части выполняют заранее определен-

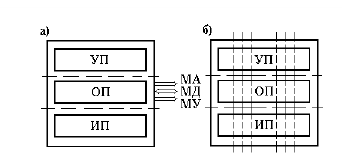

ные функции и могут работать автономно. На рис. 1,а показано функциональное разбиение структуры процессора при создании трехкристального микропроцессора (пунктирные линии), содержащего БИС операционного (ОП), БИС управляющего (УП) и БИС интерфейсного (ИП) процессоров.

Рисунок 1- Функциональная структура процессора (а) и ее разбиение

для реализации процессора в виде комплекта секционных БИС.

Операционный процессор служит для обработки данных, управ-

ляющий процессор выполняет функции выборки, декодирования и вы-

числения адресов операндов и также генерирует последовательности

микрокоманд. Автономность работы и большое быстродействие УП

позволяет выбирать команды из памяти с большей скоростью, чем ско-

рость их исполнения ОП. При этом в УП образуется очередь еще не

исполненных команд, а также заранее подготавливаются те данные,

которые потребуются ОП в следующих циклах работы. Такая опере-

жающая выборка команд экономит время ОП на ожидание операндов,

необходимых для выполнения команд программ. Интерфейсный про-

цессор позволяет подключить память и периферийные средства к мик-

ропроцессору; он, по существу, является сложным контроллером для

устройств ввода/вывода информации. Интерфейсный процессор вы-

полняет также функции канала прямого доступа к памяти.

Выбираемые из памяти команды распознаются и выполняются ка-

ждой частью микропроцессора автономно и поэтому может быть обес-

печен режим одновременной работы всех интегральных схем МП, т. е.

конвейерный поточный режим исполнения последовательности команд

программы (выполнение последовательности с небольшим временным

сдвигом). Такой режим работы значительно повышает производитель-

ность микропроцессора.

Многокристальные секционные микропроцессоры получаются в

том случае, когда в виде БИС реализуются части (секции) логической

структуры процессора при функциональном разбиении ее вертикаль-

ными плоскостями (рис. 1,б). Для построения многоразрядных микро-

процессоров при параллельном включении секций БИС в них добав-

ляются средства "стыковки".

Для создания высокопроизводительных многоразрядных микро-

процессоров требуется столь много аппаратных средств, не реализуе-

мых в доступных БИС, что может возникнуть необходимость еще и в

функциональном разбиении структуры микропроцессора горизонталь-

ными плоскостями. В результате рассмотренного функционального

разделения структуры микропроцессора на функционально и конст-

руктивно законченные части создаются условия реализации каждой из

них в виде БИС. Все они образуют комплект секционных интеграль-

ных схем МП.

Таким образом, микропроцессорная секция – это БИС, предна-

значенная для обработки нескольких разрядов данных или выполнения

определенных управляющих операций. Секционность интегральных

схем МП определяет возможность "наращивания" разрядности обраба-

тываемых данных или усложнения устройств управления микропро-

цессора при "параллельном" включении большего числа БИС.

Однокристальные и трехкристальные интегральных схем МП, как

правило, изготовляют на основе микроэлектронных технологий унипо-

лярных полупроводниковых приборов, а многокристальные секцион-

ные БИС МП на основе технологии биполярных полупроводниковых

приборов. Использование многокристальных микропроцессорных вы-

сокоскоростных биполярных БИС, имеющих функциональную закон-

ченность при малой физической разрядности обрабатываемых данных

и монтируемых в корпус с большим числом выводов, позволяет орга-

низовать разветвление связи в процессоре, а также осуществить кон-

вейерные принципы обработки информации для повышения его произ-

водительности.

По назначению различают универсальные и специализированные

микропроцессоры.

Универсальные микропроцессоры могут быть применены для ре-

шения широкого круга разнообразных задач. При этом их эффективная

производительность слабо зависит от проблемной специфики решае-

мых задач. Специализация МП, т. е. его проблемная ориентация на ус-

коренное выполнение определенных функций позволяет резко увели-

чить эффективную производительность при решении только опреде-

ленных задач.

Среди специализированных микропроцессоров можно выделить

различные микроконтроллеры, ориентированные на выполнение слож-

ных последовательностей логических операций, математические МП,

предназначенные для повышения производительности при выполнении

арифметических операций за счет, например, матричных методов их

выполнения, МП для обработки данных в различных областях приме-

нений и т. д. С помощью специализированных МП можно эффективно

решать новые сложные задачи параллельной обработки данных. На-

пример, конволюция позволяет осуществить более сложную математи-

ческую обработку сигналов, чем широко используемые методы корре-

ляции. Последние в основном сводятся к сравнению всего двух серий

данных: входных, передаваемых формой сигнала, и фиксированных

опорных, а также к определению их подобия. Конволюция дает воз-

можность в реальном масштабе времени находить соответствие для

сигналов изменяющейся формы путем сравнения их с различными эта-

лонными сигналами, что, например, может позволить эффективно вы-

делить полезный сигнал на фоне шума. Разработанные однокристаль-

ные конвольверы используются в устройствах опознавания образов в

тех случаях, когда возможности сбора данных превосходят способно-

сти системы обрабатывать эти данные.

По виду обрабатываемых входных сигналов различают цифро-

вые и аналоговые микропроцессоры.

Сами микропроцессоры – цифровые устройства, однако, могут

иметь встроенные аналого-цифровые и цифроаналоговые преобразова-

тели. Поэтому входные аналоговые сигналы передаются в МП через

преобразователь в цифровой форме, обрабатываются и после обратно-

го преобразования в аналоговую форму поступают на выход. С архи-

тектурной точки зрения такие микропроцессоры представляют собой

аналоговые функциональные преобразователи сигналов и называются

аналоговыми микропроцессорами. Они выполняют функции любой

аналоговой схемы (например, производят генерацию колебаний, моду-

ляцию, смещение, фильтрацию, кодирование и декодирование сигна-

лов в реальном масштабе времени и т. д., заменяя сложные схемы, со-

стоящие из операционных усилителей, катушек индуктивности, кон-

денсаторов и т. д.). При этом применение аналогового микропроцессо-

ра значительно повышает точность обработки аналоговых сигналов и

их воспроизводимость, а также расширяет функциональные возможно-

сти за счет программной "настройки" цифровой части микропроцессо-

ра на различные алгоритмы обработки сигналов.

Обычно в составе однокристальных аналоговых МП имеется не-

сколько каналов аналого-цифрового и цифроаналогового преобразова-

ния. В аналоговом микропроцессоре разрядность обрабатываемых дан-

ных достигает 24 бит и более, большое значение уделяется увеличению

скорости выполнения арифметических операций.

Отличительная черта аналоговых микропроцессоров – способ-

ность к переработке большого объема числовых данных, т. е. к выпол-

нению операций сложения и умножения с большой скоростью при не-

обходимости даже за счет отказа от операций прерываний и переходов.

Аналоговый сигнал, преобразованный в цифровую форму, обрабатыва-

ется в реальном масштабе времени и передается на выход обычно в

аналоговой форме через цифроаналоговый преобразователь. При этом,

согласно теореме Котельникова, частота квантования аналогового сиг-

нала должна вдвое превышать верхнюю частоту сигнала.

Сравнение цифровых микропроцессоров производится сопостав-

лением времени выполнения ими списков операций. Сравнение же

аналоговых микропроцессоров производится по количеству эквива-

лентных звеньев аналого-цифровых фильтров рекурсивных фильтров

второго порядка. Производительность аналогового микропроцессора

определяется его способностью быстро выполнять операции умноже-

ния: чем быстрее осуществляется умножение, тем больше эквивалент-

ное количество звеньев фильтра в аналоговом преобразователе и тем

более сложный алгоритм преобразования цифровых сигналов можно

задавать в микропроцессоре.

Одним из направлений дальнейшего совершенствования аналого-

вых микропроцессоров является повышение их универсальности и

гибкости. Поэтому вместе с повышением скорости обработки большо-

го объема цифровых данных будут развиваться средства обеспечения

развитых вычислительных процессов обработки цифровой информа-

ции за счет реализации аппаратных блоков прерывания программ и

программных переходов.

По характеру временной организации работы микропроцессо-

ры делят на синхронные и асинхронные.

Синхронные микропроцессоры – микропроцессоры, в которых

начало и конец выполнения операций задаются устройством управле-

ния (время выполнения операций в этом случае не зависит от вида вы-

полняемых команд и величин операндов).

Асинхронные микропроцессоры позволяют начало выполнения

каждой следующей операции определить по сигналу фактического

окончания выполнения предыдущей операции. Для более эффективно-

го использования каждого устройства микропроцессорной системы в

состав асинхронно работающих устройств вводят электронные цепи,

обеспечивающие автономное функционирование устройств. Закончив

работу над какой-либо операцией, устройство вырабатывает сигнал за-

проса, означающий его готовность к выполнению следующей опера-

ции. При этом роль естественного распределителя работ принимает на

себя память, которая в соответствии с заранее установленным приори-

тетом выполняет запросы остальных устройств по обеспечению их ко-

мандной информацией и данными.

По количеству выполняемых программ различают одно- и мно-

гопрограммные микропроцессоры. В однопрограммных микропроцессорах выполняется только одна программа. Переход к выполнению другой программы происходит после завершения текущей программы.

В много- или мультипрограммных микропроцессорах одновре-

менно выполняется несколько (обычно несколько десятков) программ.

Организация мультипрограммной работы микропроцессорных управ-

ляющих систем позволяет осуществить контроль за состоянием и

управлением большого числа источников или приемников информа-

ции.

Основные характеристики микропроцессора

Микропроцессор характеризуется:

1) тактовой частотой, определяющей максимальное время выпол-

нения переключения элементов в ЭВМ;

2) разрядностью, т. е. максимальным числом одновременно обра-

батываемых двоичных разрядов;

3) архитектурой.

Разрядность МП обозначается m/n/k/ и включает:

m – разрядность внутренних регистров, определяет принадлеж-

ность к тому или иному классу процессоров;

n – разрядность шины данных, определяет скорость передачи ин-

формации;

k – разрядность шины адреса, определяет размер адресного про-

странства.

Например, МП i8088 характеризуется значениями m/n/k = 16/8/20;

По разрядности обрбатываемых операндов на сегодняшний день можно выделить 8-, 16-, 32- и 64-разрядные микропроцессоры. Микропроцессоры с высокой разрядностью используются в основном в персональных и суперЭВМ. Использование таких микропроцессоров в специализированных задачах неоправданно из-за их высокой стоимости и избыточности разрядности в отношении точности обработки и округления результатов.

Понятие архитектуры микропроцессора включает в себя систему

команд и способы адресации, возможность совмещения выполнения

команд во времени, наличие дополнительных устройств в составе мик-

ропроцессора, принципы и режимы его работы. Выделяют понятия

микроархитектуры и макроархитектуры.

Микроархитектура микропроцессора – это аппаратная организация

и логическая структура микропроцессора, регистры, управляющие

схемы, арифметико-логические устройства, запоминающие устройства

и связывающие их информационные магистрали .

Макроархитектура – это система команд, типы обрабатываемых

данных, режимы адресации и принципы работы микропроцессора.

В общем случае под архитектурой ЭВМ понимается абстрактное

представление машины в терминах основных функциональных модулей, языка ЭВМ, структуры данных.

Дата: 2019-03-05, просмотров: 544.

-(2/s)

-(2/s)