Особенности универсальных процессоров с точки зрения цифровой обработки информации

Особенности процессоров цифровой обработки, повышающее быстродействие

1 ) Гарвардская архитектура;

2) Конвейерная обработка;

3) быстрые специализированные умножители-накопители;

4) специальные команды цифровой обработки;

5) средства дублирования;

6) встроенная кэш-память и обычная память;

7) расширенный параллелизм.

В универсальных процессорах также существуют части этих элементов (2,6,7). По архитектуре глобально отличается.

Конвейерная обработка. Конвейер команд позволяет загружать в процессор одновременно множество команд, которые будут находиться в конвейере команд на разных этапах их обработки.

Быстрые специализированные умножители-накопители: большинство операций цифровой обработки содержат в качестве основы операции умножения и сложения.

Операции типа умножение очень трудоемкие с точки зрения процессора.

Для ускорения выполнения этих операций применяются аппаратные блоки процессора.

Специальные команды цифровой обработки.

Специализированные команды имеют следующие преимущества:

1 ) при компиляции формируется более компактный код;

2) повышенное быстродействие выполнения алгоритмов цифровой обработки;

По содержанию специализированные команды могут быть:

1 ) команды, поддерживающие базовые операции цифровой обработки;

2) команды, снижающие служебные издержки для организации циклов

3) команды, направленные на конкретные приложения.

Средства дублирования. В процессорах цифровой обработки вычислительные блоки могут дублироваться для повышения быстродействия. При этом обеспечивается возможность параллельной обработки.

Встроенная кэш-память. Встроенная память повышает скорость обмена информации между процессором и памятью. Внутренняя кэш процессора хранит часто используемую информацию – данные и фрагменты кода программы (функции).

Внешний кэш предназначен для согласования работы процессора и внешней памяти.

Архитектура специализированных процессоров ЦОС

НОРМ ОТВЕТ

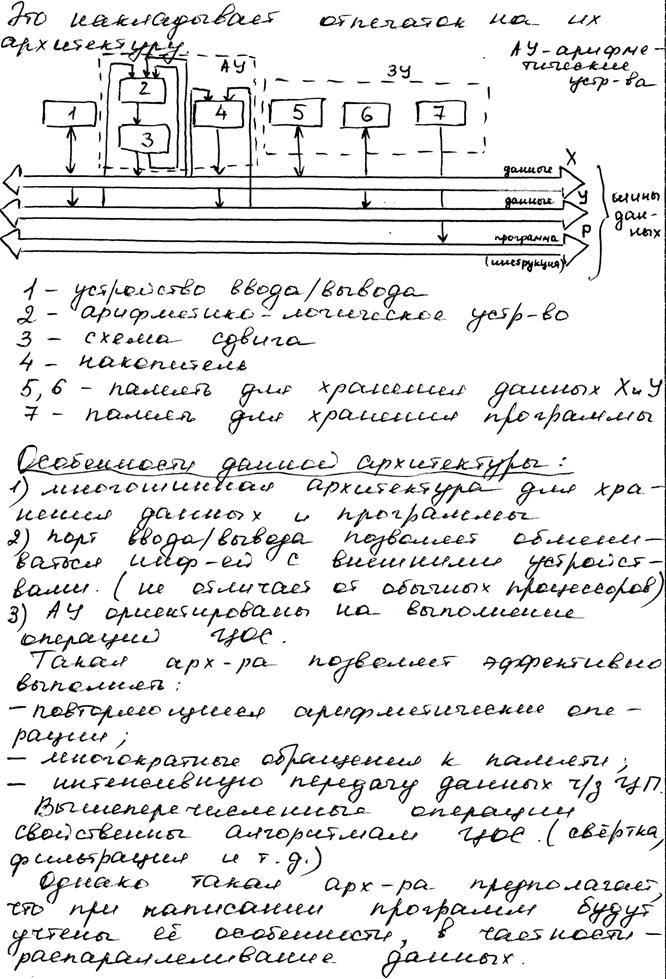

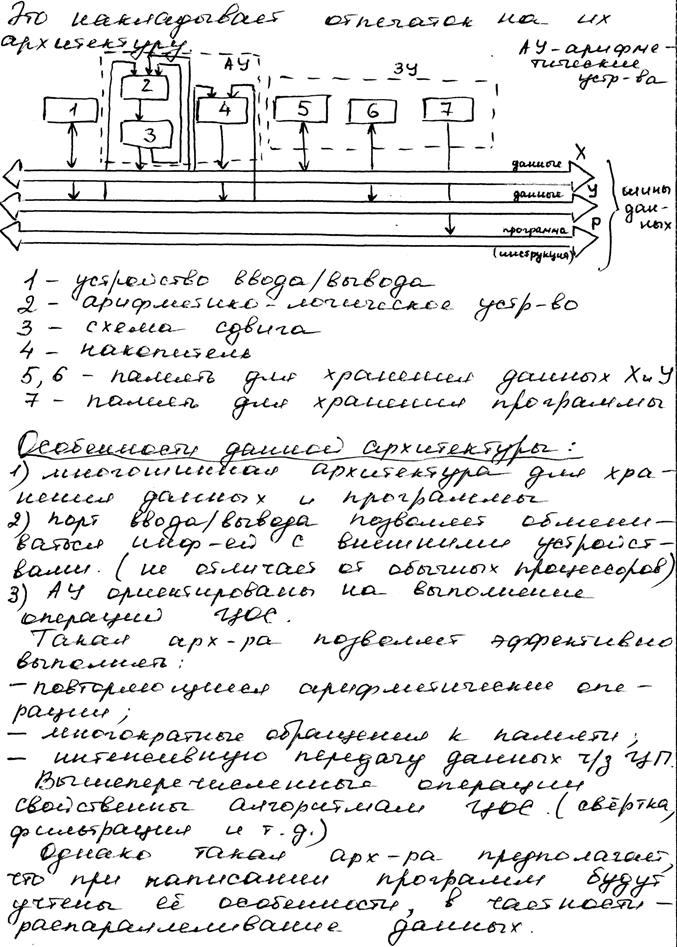

Архитектура процессоров ЦОС

Процессоры ЦОС ориентированы на работу в реальном масштабе времени.

ЦСП строятся на основе Гарвардской архитектуры Цифровые сигнальные процессоры строятся на основе т. н. «Гарвардской архитектуры», отличительной особенностью которой является то, что программы и данные хранятся в различных устройствах памяти — памяти программ и памяти данных. В отличие от архитектуры фон Неймана, где процессору для выборки команды и двух операндов требуется минимум три цикла шины, ЦСП может производить одновременные обращения как к памяти команд, так и к памяти данных, и указанная выше команда может быть получена за два цикла шины. В реальности, благодаря продуманности системы команд и другим мерам, это время может быть сокращено до одного цикла. В реальных устройствах память команд может хранить не только программы, но и данные. В этом случае говорят, что ЦСП построен по модифицированной гарвардской архитектуре. Память команд и память данных обычно располагаются на кристалле ЦСП. В связи с тем, что эта память имеет относительно небольшой объём, возникает необходимость в использовании внешних (относительно кристалла процессора) запоминающих устройств. Для таких устройств раздельные шины команд и данных не используются, так это потребовало бы значительно увеличить количество внешних выводов кристалла, что дорого и непрактично. Поэтому взаимодействие ЦСП с внешними запоминающими устройствами происходит по одному комплекту шин без разделения на команды и данные. Следует также заметить, что обращение к внешней памяти всегда занимает значительно больше времени, чем к внутренней, поэтому в приложениях, критичных ко времени исполнения, такие обращения необходимо минимизировать.

Дата: 2019-03-05, просмотров: 402.