10.1. Перемножители и делители на операционных усилителях.

Среди многообразия методов аналогового перемножения наибольшее распространение получили следующие четыре из-за простоты их реализации на ОУ: с управляемым сопротивлением, импульсные, логарифмические и с переменной крутизной. Последний тип перемножителей, видоизмененный в соответствии с требованиями полупроводниковой технологии, оказался наиболее удачным для изготовления в виде полупроводниковой микросхемы.

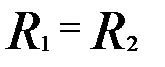

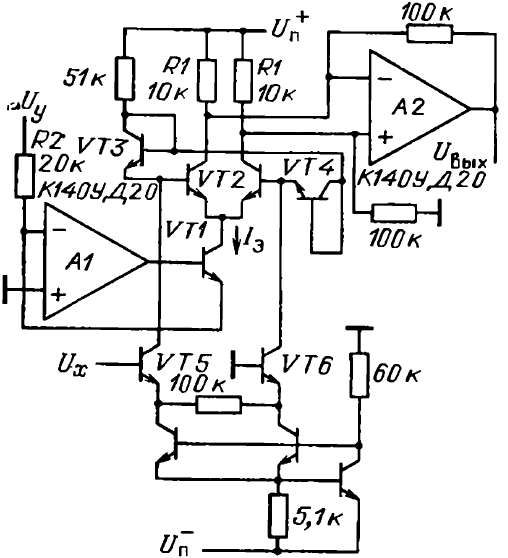

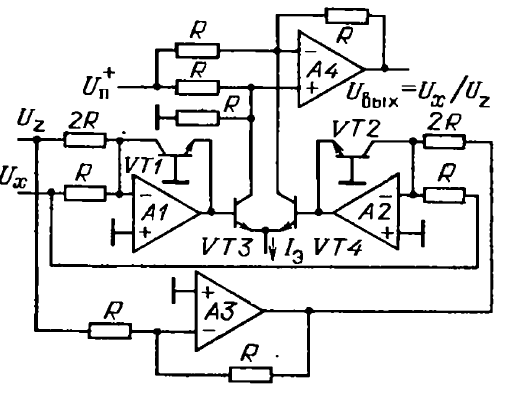

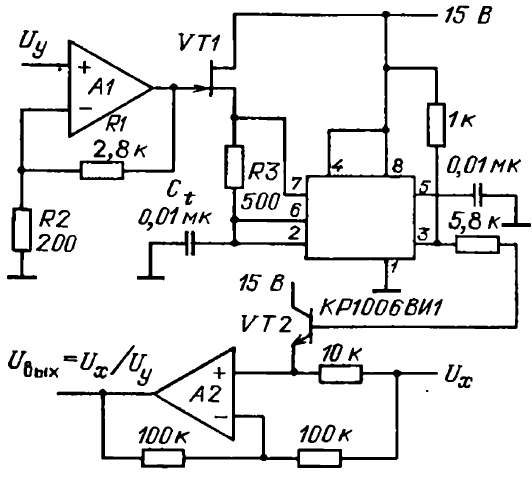

Перемножители на основе управляемого сопротивления наиболее просты. Если сопротивление пропорционально управляющему напряжению, то ток через это сопротивление пропорционален произведению входного и управляющего сигналов или частному от их деления. В качестве управляемых напряжением сопротивлений можно использовать полевые транзисторы (рис. 10.1). На начальном участке вольт-амперной характеристики полевой транзистор по существу является резистором с сопротивлением, управляемым по цепи затвора. Действие температурного дрейфа нелинейной зависимости этого сопротивления от управляющего напряжения на точность умножения значительно уменьшается включением полевого транзистора в цепь ОС усилителя А2.

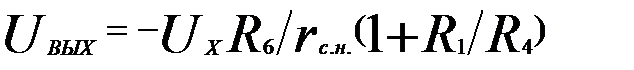

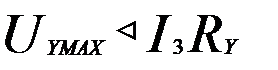

При идентичных по параметрам полевых транзисторах  ,

,  где - сопротивление между стоком и истоком полевых транзисторов. Сопротивление

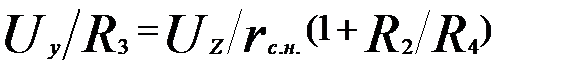

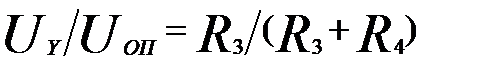

где - сопротивление между стоком и истоком полевых транзисторов. Сопротивление  транзистора VT1 зависит от выходного напряжений А2, которое определяется, ё сбою огередь, напряжениями Uy и Uz. Чтобы обеспечить выполнение транзистором VT2 функции переменного сопротивления, Необходимо установить Uy <0, Uz > 0. Если входной ток А2 пренебрежимо мал по сравнению с током, протекающим по цепи транзистора VT2 и резистора R3, то будет справедливо равенство

транзистора VT1 зависит от выходного напряжений А2, которое определяется, ё сбою огередь, напряжениями Uy и Uz. Чтобы обеспечить выполнение транзистором VT2 функции переменного сопротивления, Необходимо установить Uy <0, Uz > 0. Если входной ток А2 пренебрежимо мал по сравнению с током, протекающим по цепи транзистора VT2 и резистора R3, то будет справедливо равенство  . Определив из последнего равенства значение

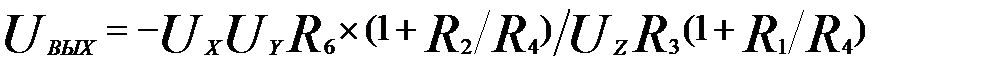

. Определив из последнего равенства значение  , и затем подставив его в выражение для Uвых, получим зависимость выходного напряжения от сопротивлений резисторов

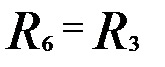

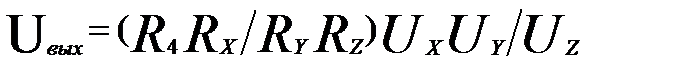

, и затем подставив его в выражение для Uвых, получим зависимость выходного напряжения от сопротивлений резисторов  . Как видно из последнего выражения, при

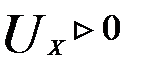

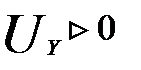

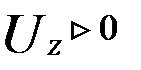

. Как видно из последнего выражения, при  и

и

. Чтобы уменьшить влияние нелинейности и неидентичности зависимостей сопротивлений сток-исток полевых транзисторов, необходимо выбрать сопротивления R1–R5 значительно больше

. Чтобы уменьшить влияние нелинейности и неидентичности зависимостей сопротивлений сток-исток полевых транзисторов, необходимо выбрать сопротивления R1–R5 значительно больше  . Например, при типовом

. Например, при типовом  кОм точность умножения около 2% можно получить, установив R1=R2= 1 МОм, R3 = R6 = 0,1, R4 = 0,2 МОм, R5 = = 20 кОм. Полоса пропускания этой схемы будет определяться ОУ, а динамический диапазон входных сигналов — типом полевых транзисторов. Для получения наименьшей ошибки из-за нелинейности вольт-амперной характеристики VT1и VT2. Целесообразно ограничить амплитуду Ux Uy и Uz напряжениями 3...5 В. Тогда при использовании ОУ К154УДЗ можно получить точность умножения около 2% в диапазоне частот 0...1 МГц. Для устранения возможной неустойчивости в работе устройства между выходами ОУ и их инвертирующими входами целесообразно включить конденсаторы емкостью 10... 100 пФ в зависимости от типа ОУ. Таким образом, рассмотренный тип перемножителя-делителя целесообразно использовать в тех случаях, когда для двух квадрантов в плоскости ху необходимо получить максимальное быстродействие и не требуется высокая точность вычисления.

кОм точность умножения около 2% можно получить, установив R1=R2= 1 МОм, R3 = R6 = 0,1, R4 = 0,2 МОм, R5 = = 20 кОм. Полоса пропускания этой схемы будет определяться ОУ, а динамический диапазон входных сигналов — типом полевых транзисторов. Для получения наименьшей ошибки из-за нелинейности вольт-амперной характеристики VT1и VT2. Целесообразно ограничить амплитуду Ux Uy и Uz напряжениями 3...5 В. Тогда при использовании ОУ К154УДЗ можно получить точность умножения около 2% в диапазоне частот 0...1 МГц. Для устранения возможной неустойчивости в работе устройства между выходами ОУ и их инвертирующими входами целесообразно включить конденсаторы емкостью 10... 100 пФ в зависимости от типа ОУ. Таким образом, рассмотренный тип перемножителя-делителя целесообразно использовать в тех случаях, когда для двух квадрантов в плоскости ху необходимо получить максимальное быстродействие и не требуется высокая точность вычисления.

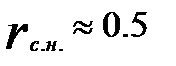

Перемножитель на логарифмических усилителях наиболее очевиден для построения и прост при расчете. Алгоритм его синтеза сводйтся к выполнению Последовательности операций: In х, In у, In x + tn у = \п ху, antilh(lri ху) —ху.

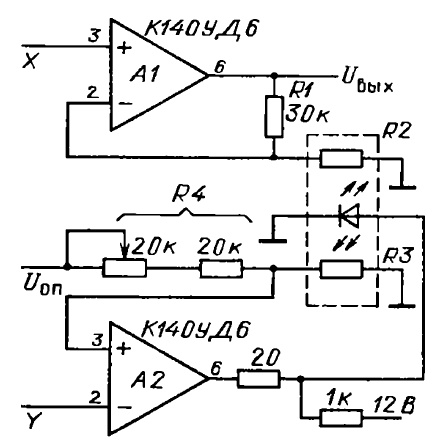

Известно большое число" различных схем одноквадрантных перемножителей-делителей, состоящих из трех логарифмических усилителей и одного антилогарифмического, Одна из них показана на рис. 3.2. Логарифмические усилители At, А2, A3 и антилогарифмический А4 используют .две пары интегральных транзисторов. Могут быть использованы транзисторы К1НТ591 или К198НТ1.

Рисунок 10.1 Схема перемножителя на полевых транзисторах

Рисунок 10.2 Схема перемножителя на логарифмических усилителях

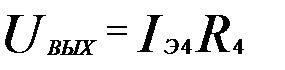

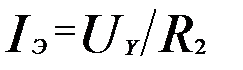

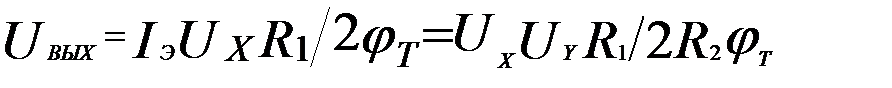

Выходное напряжение Перемножителя  , где

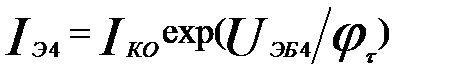

, где  —эмиттерный ток транзистора VT4.

—эмиттерный ток транзистора VT4.

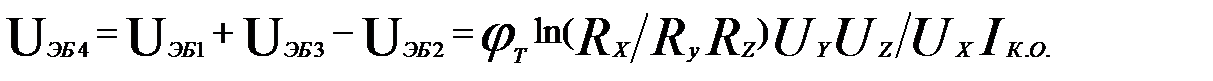

Напряжение 0Э Б4 определяется из равенства

Подставляя  в выражение для

в выражение для  , а затем

, а затем  в

в  и предполагая идентичными транзисторы и ОУ, получаем

и предполагая идентичными транзисторы и ОУ, получаем  где

где  ,

,  B

B  .

.

Из последнего выражения видно, что выходное напряжение логарифмического умножителя не зависит от температуры, а масштабный коэффициент определяется отношением сопротивлений внешних резисторов.

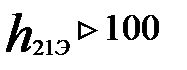

Высокая точность и большой динамический диапазон амплитуд входных сигналов при умножении и делении, характерные для данной схемы, обусловлены следующими факторами. Используются идентичные пары транзисторов с коэффициентом передачи базового тока  и ОУ К140УД6 с температурным дрейфом менее 20 мкВ/°С и входными токами менее 30 нА. Поэтому даже при входных сигналах порядка 100 мВ приведенная ко входу погрешность не превышает 0,5%, а ошибка из-за нелинейности не больше 0,2%. Суммируются логарифмы токов, а не их абсолютные величины. Благодаря этому исключается насыщение транзисторов в широком диапазоне изменения входных напряжений.

и ОУ К140УД6 с температурным дрейфом менее 20 мкВ/°С и входными токами менее 30 нА. Поэтому даже при входных сигналах порядка 100 мВ приведенная ко входу погрешность не превышает 0,5%, а ошибка из-за нелинейности не больше 0,2%. Суммируются логарифмы токов, а не их абсолютные величины. Благодаря этому исключается насыщение транзисторов в широком диапазоне изменения входных напряжений.

Недостаток схемы — общий для большинства схем на логарифмических усилителях — заключается в зависимости полосы рабочих частот от величины входных сигналов. Например, ширина полосы пропускания при входном напряжении 10 В составляет 100 кГц, а при 1 В сужается до 10 кГц. Объясняется это тем, что при больших входных напряжениях в цепях логарифмического перемножителя протекают большие входные токи и, следовательно, быстрее перезаряжаются паразитные емкости в схеме. Приведенная схема умножителя применима только при одинаковой полярности входных сигналов. Следовательно, логарифмический перемножитель является одноквадрантным. В принципе на базе логарифмического перемножителя можно построить четырехквадрантный умножитель, но при значительных аппаратурных затратах. Для устойчивой работы логарифмических усилителей между выходами и инвертирующими входами А1 — A3 следует включать конденсаторы емкостью 200... ...250 пФ.

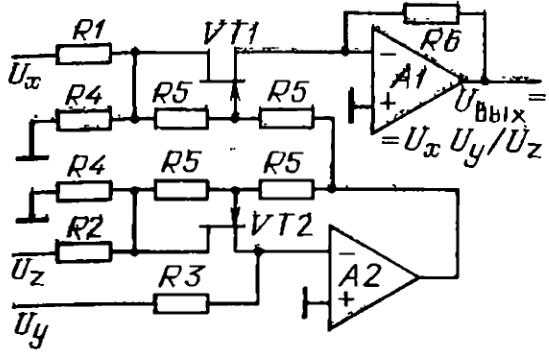

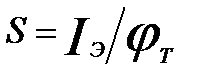

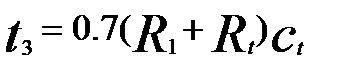

Перемножитель на основе переменной крутизны в простейшем двухквадрантном исполнении (рис. 3.3) реализуется посредством изменения эмиттерного тока  (а следовательно, и крутизны

(а следовательно, и крутизны  ) транзисторов VT1 и VT2. Изменение коллекторного тока

) транзисторов VT1 и VT2. Изменение коллекторного тока  любого из указанных транзисторов в зависимости от

любого из указанных транзисторов в зависимости от  описывается выражением

описывается выражением  . ОУ преобразует дифференциальный выходной ток транзисторов VT1, VT2 в напряжение

. ОУ преобразует дифференциальный выходной ток транзисторов VT1, VT2 в напряжение  . Учитывая, что изменение тока

. Учитывая, что изменение тока  от напряжения

от напряжения  определяется равенством

определяется равенством  , получаем

, получаем  .

.

Для компенсации нелинейности вольт-амперной характеристики транзисторов VT1 и VT2 при Ux>10 мВ используются логарифмирующие свойства диодов VT3 и VT4. Последние логарифмируют токи, поступающие от транзисторов VT5 и VT6, а транзисторы VT1 и VT2 осуществляют экспонирование эмиттерно-базовых напряжений VT3 и VT4. Таким образом достигается линейная зависимость между токами через транзисторы VT5, VT6 и VT13 VT2.

Благодаря использованию источника тока, построенного на усилителе А1, расширяется диапазон линейной зависимости  от

от  вплоть до

вплоть до  . Перед применением схемы сначала при

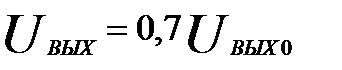

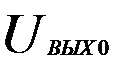

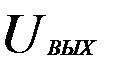

. Перед применением схемы сначала при  резистором R 5, затем при максимальном напряжении

резистором R 5, затем при максимальном напряжении  резистором R6 устанавливается

резистором R6 устанавливается  .

.

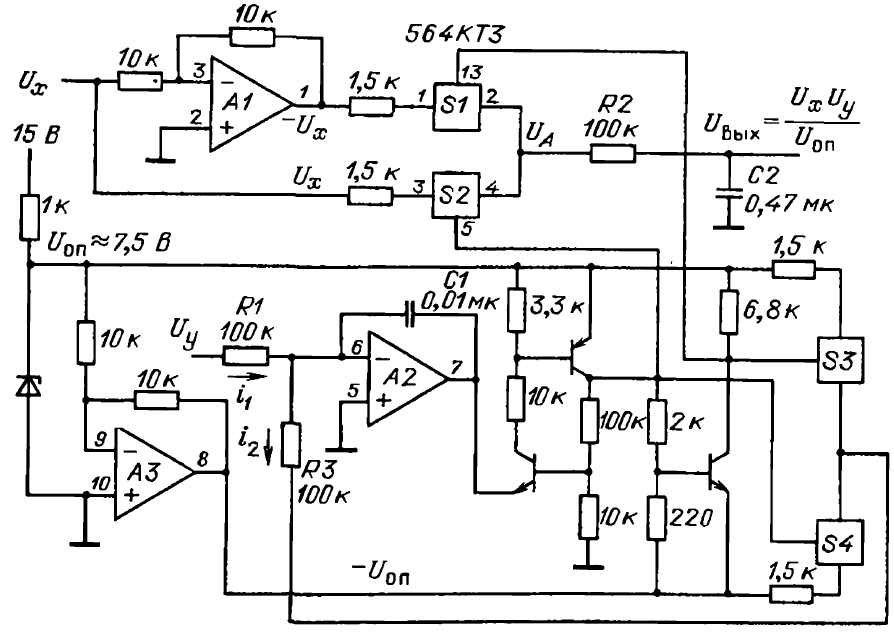

Импульсный перемножитель применяют, когда использованием рассмотренных выше схем невозможно достичь точности- перемножения лучше 0,1%. Если необходима такая точность и достаточна полоса рабочих частот в несколько десятков герц, целесообразно применять импульсные перемножители. Последние при умножении низкочастотных аналоговых сигналов обеспечивают по крайней мере на порядок более высокую точность, чем перемножители, работающие по принципу нормировки токов. Например, описанный ниже перемножитель К525ПС1 позволяет получить погрешность умножения около 1%. В то же время приведенная на рис. 3.4 схема* позволяет умножить два сигнала с погрешностью не более 0,05%, т. е. в 20 раз точнее.

Рассмотрим принцип работы представленного на рисунке импульсного перемножителя, состоящего из инвертирующего усилителя на А1, интегратора на А2, инвертора опорного напряжения на A3 и триггера, собранного на биполярных транзисторах. Переключатели SI - S4 выполнены на КМОП микросхемах.

Рисунок 10.3 Схема перемножения на дифиринциальном усилителе.

Рисунок 10.4 Схема импульсного перемножителя

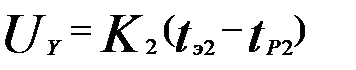

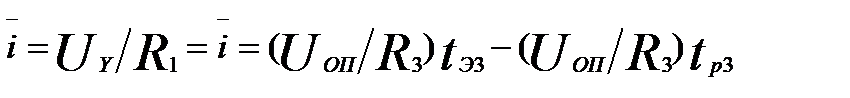

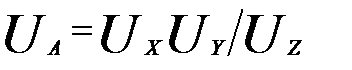

Напряжение UA на выходе переключателей S1, S2 в любой момент времени является функцией их положения, которое, в свою очередь, зависит от управляющего сигнала, снимаемого с выхода триггера Шмитта. В зависимости от того, какой из переключателей S1 или S2 замкнут, напряжение UA становится равным Ux или -Ux. Среднее значение напряжения UA будет определяться выражением

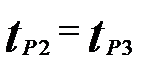

где  — время, в течение которого замкнут переключатель S2,

— время, в течение которого замкнут переключатель S2,  — время, в течение которого разомкнут переключатель S2 и замкнут S1t К1 — масштабный коэффициент. Таким образом, в течение времени

— время, в течение которого разомкнут переключатель S2 и замкнут S1t К1 — масштабный коэффициент. Таким образом, в течение времени  получим UA=-UX, а в течение времени tp2 будет UA = — UX, т. е. при работе устройства напряжение UA будет иметь вид прямоугольных .импульсов, амплитуда которых изменяется от - Ux до Ux. Если скважность периодического импульсного сигнала, определяемую выражением

получим UA=-UX, а в течение времени tp2 будет UA = — UX, т. е. при работе устройства напряжение UA будет иметь вид прямоугольных .импульсов, амплитуда которых изменяется от - Ux до Ux. Если скважность периодического импульсного сигнала, определяемую выражением  сделать пропорциональной второму входному аналоговому сигналу Uy, то будет справедливо следующее выражение:

сделать пропорциональной второму входному аналоговому сигналу Uy, то будет справедливо следующее выражение:

где  — масштабный коэффициент. Решая совместно уравнения (3.1) и (3.2), получаем UA = UKUy/K1, К2, что и требовалось.

— масштабный коэффициент. Решая совместно уравнения (3.1) и (3.2), получаем UA = UKUy/K1, К2, что и требовалось.

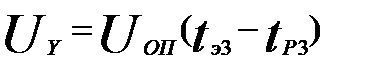

Показанную в выражении (3.2) зависимость Uy от  и

и  обеспечивает в рассматриваемой схеме широтно-импульсный модулятор, состоящий из интегратора на А2 и триггера Шмнтта. Среднее значение входного тока интегратора за период его работы будет приблизительно равно нулю благодаря небольшому (меньше 1 мкА) входному току ОУ К1401УД2. Поэтому

обеспечивает в рассматриваемой схеме широтно-импульсный модулятор, состоящий из интегратора на А2 и триггера Шмнтта. Среднее значение входного тока интегратора за период его работы будет приблизительно равно нулю благодаря небольшому (меньше 1 мкА) входному току ОУ К1401УД2. Поэтому  , где

, где  — время, в течение которого переключатель S3 замкнут,

— время, в течение которого переключатель S3 замкнут,  — время, в течение которого переключатель S3 разомкнут, S4 замкнут. В течение времени Uз на вход интегратора через R3 подается напряжение

— время, в течение которого переключатель S3 разомкнут, S4 замкнут. В течение времени Uз на вход интегратора через R3 подается напряжение  , а в течение

, а в течение  напряжение —

напряжение —  . Из последнего уравнения следует, что

. Из последнего уравнения следует, что

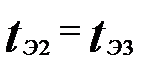

Из сравнения последнего уравнения для Uy с (3.1) видно, что если установить во время работы схемы  и

и  , то можно получить

, то можно получить  . Чтобы это обеспечить, триггер Шмитта управляет одновременно переключателями S1 - S4 так, что когда S2 и S3 замкнуты, то S 1 и S4 разомкнуты.

. Чтобы это обеспечить, триггер Шмитта управляет одновременно переключателями S1 - S4 так, что когда S2 и S3 замкнуты, то S 1 и S4 разомкнуты.

В интеграторе широтно-импульсного модулятора напряжение  является сигналом ОС, поступающим на суммирующий вход А2. Благодаря этому достигается пропорциональность разности

является сигналом ОС, поступающим на суммирующий вход А2. Благодаря этому достигается пропорциональность разности  -

-  напряжению

напряжению  . Следует, однако, отметить,- что, хотя напряжение

. Следует, однако, отметить,- что, хотя напряжение  управляет скважностью выходного импульсного напряжения

управляет скважностью выходного импульсного напряжения  , частота этих импульсов не зависит от него. При Uy=0 получим

, частота этих импульсов не зависит от него. При Uy=0 получим  =

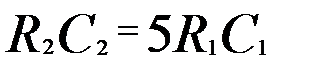

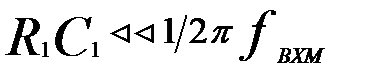

=  . Импульсное напряжение UA интегрируется на выходе перемножителя с помощью пассивной RC-цепи. Постоянная времени цепи R2C2 должна быть больше постоянной рремени цепи R1C1. На практике желательно выбрать

. Импульсное напряжение UA интегрируется на выходе перемножителя с помощью пассивной RC-цепи. Постоянная времени цепи R2C2 должна быть больше постоянной рремени цепи R1C1. На практике желательно выбрать  . Чтобы обеспечить высокую точность умножения аналоговых сигналов, необходимо R1C1 выбрать из условия

. Чтобы обеспечить высокую точность умножения аналоговых сигналов, необходимо R1C1 выбрать из условия  , где

, где  — максимальная частота входных сигналов U Х и U у.

— максимальная частота входных сигналов U Х и U у.

Рассмотренные типы перемножителей используются главным образом для построения специализированных схем, поскольку каждую отличает характерная особенность. Для решения задач, требующих средней точности и быстродействия, были изготовлены полупроводниковые перемножители, большинство из которых используют метод нормировки токов .

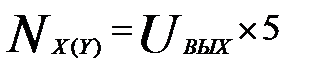

Делитель аналоговых сигналов просто получить из обычного инвертирующего усилителя, у которого последовательно с Rос включен перемножитель. Выход перемножителя подключается к Rос, а вход U перемножителя к выходу ОУ. Делимое Uz подается через резистор Rвх на инвертирующий вход ОУ, а делитель Ux на вход X перемножителя. Выходной сигнал такого делителя определяется выражением Uвых= -KдUz/Ux, где выбирают Kд=1 В при Uz> Ux и Кд=10 В при Uz.≤ Ux. В такой схеме при уменьшении Ux уменьшается и выходное напряжение умножителя. Однако Uz остается неизменным, поэтому и выходное напряжение перемножителя должно оставаться неизменным. Следовательно, обратно пропорционально Ux должно увеличиться Uy =Uвых, а это эквивалентно пропорциональному увеличению Uz. При Ux→0 сопротивление цепи ОС ОУ стремится к бесконечности. Таким образом реализуется деление Uz на Ux. Деление может осуществиться в двух квадрантах, поскольку схема работает только при условии, что Ux> 0, хотя и при любой полярности Uz.

Деление сигналов можно осуществить и с помощью только одного перемножителя К525ПС1, управляя значением тока I 3. В этом случае Uвых = KUxUy/UZy, где Uz - функция от тока I 3. Ток I 3=( Uz – Uп – Uэб)/(R 3 + 0,5 кОм)≈Uz/14,3 кОм+ 1 мА. При постоянных величинах Ux=Uy=5 В нормированное относительно тока 1 мА выходное напряжение Uвых = 2,31/ I 3, где ток I 3 — в миллиамперах. Начальный сдвиг выходного уровня устраняется внешней регулировкой.

Аналоговые делители на перемножителях имеют обычно точность не лучше 5%, которая сохраняется в сравнительно узком дипазоне изменения амплитуды входных сигналов. Поэтому разработаны специализированные аналоговые делители, в основу лучших из которых положен метод переменной крутизны или использованы логарифмические усилители.

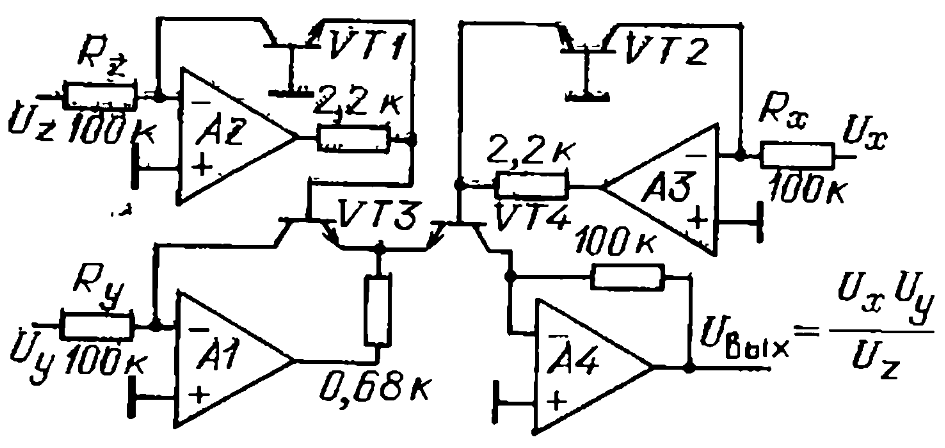

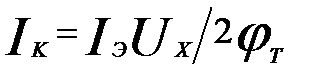

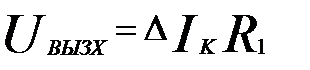

В делителе, построенном на основе метода переменной крутизны (рис. 3.5), напряжение подается на два идентичных усилителя А1 и А2. Сигналы Uz через инвертор A3 (— Uz) прикладываются в суммирующие точки тех же усилителей. Напряжения Ux и Uz преобразуются в токи, которые суммируются и вычитаются усилителями А1 и А2. Напряжения Ux и Uz пропорциональны логарифмам суммы и разности этих токов. Транзисторы VT3 и VT4 дифференциального антилогарифмического усилителя преобразуют разность коллекторных токов в напряжение Uвых=∆IK2Rос, где ∆IK =IосIz/2Ix, Iz=Uz/2R, IX=UX/R. Поэтому Uвых = 2IoпRocUz/Ux.

Точность деления такой схемы существенно зависит от параметров ОУ. Поскольку входные токи большинства ОУ порядка 100 нА, они существенно ограничивают динамический диапазон входных сигналов, который мог бы определяться диапазоном «идеальности» вольт-амперной характеристики р-п перехода, равным 10 пА... ... 100 мкА. Несколько лучшие результаты можно получить, используя ОУ с полевыми транзисторами на входе, сохраняя постоянную температуру и вводя регулировку смещения нуля ОУ. Симметричная структура схемы обеспечивает ее работу в двух квадрантах. При идеально сбалансированных токах в симметричных цепях нелинейные искажения отсутствуют. Балансировку можно провести, подбирая сопротивления входных резисторов. Если диапазон изменения значений делителя ограничен напряжениями 10 мВ ... 1 В, то, используя 1%-ные резисторы, можно получить точность около 1%. При токе Iоп = 0,2 мА и применении ОУ К1401УД2 или аналогичных по параметрам полоса пропускания около 0,5 МГц: Полоса пропускания расширяется более чем на порядок при использовании ОУ К154УДЗ и большем токе Iоп.

Рисунок 10.5. Схема усилителя на основе дифференциального усилителя.

Рисунок 10.6. Делитель на диодно-резисторном оптоэлектронном элементе.

Логарифмический делитель целесообразно применять при одинаковой полярности входных сигналов. Хорошей совокупностью параметров в режиме деления обладает описанная выше схема логарифмического умножителя-делителя (см. рис. 3.2). Эта схема выполняет умножение и деление с одинаковой точностью, что позволяет ее применять для вычисления квадратных корней, средне- квадратических значений и решения векторных уравнений. Например, для извлечения квадратного корня при сигналах, изменяющихся в большом диапазоне, требуется только соединить выход со входом Ux. Тогда Uвых=10Uz/Uвых  .

.

Когда необходимо получить деление сравнительно широкополосных сигналов и не предъявляются высокие требования к точности операции деления, можно воспользоваться простой схемой на рис. 10.6. Этот делитель использует диодно-резисторную оптоэлектроную пару, обеспечивающую обратную связь в цепи одного из усилителей (в данном случае А2). Устройство состоит из двух каналов подачи аналогового сигнала. ОУ А1 включен по схеме обычного не инвертирующего усилителя. В ОУ А2 входной сигнал подается на инвертирующий вход, а сигнал ОС — на неинвертирующий. Однако последнее не приводит к самовозбуждению усилителя благодаря тому, что сигнал инвертируется в цепи оптоэлектронной связи.

Усилитель на А1 имеет коэффициент усиления, зависящий от соотношения резисторов R1, R2, и полосу пропускания, определяе мую в основном типом ОУ. Сопротивление резистора R1 устанавливается таким образом, чтобы при выбранном типе оптоэлектрон- ной пары коэффициент усиления схемы иг А1 был близок к 1. Сопротивлением фоторезистора R2 в процессе работы делителя управляет сигнал Y посредством изменения излучения светодиода.

Фоторезистор R3 включен в петлю ОС для корректирования эффектов, вызванных нелинейностью зависимости тока через светодиод и фоторезистор R2. Коэффициент усиления усилителя на А1 в неинвертирующем включении определяется выражением Uвых/Ux = (R 1 + R2)/R2. В свою очередь, для усилителя на А2 ток через R3 зависит как от тока через светодиод, так и от напряжения источника опорного сигнала, т. е.  . Из сопоставления двух последних уравнений видно, что деление двух входаых сигналов Ux и Uy может быть достигнуто только при R1=R4 и R2 =R 3. Тогда Uвых = (Ux/Uy)Uоп.

. Из сопоставления двух последних уравнений видно, что деление двух входаых сигналов Ux и Uy может быть достигнуто только при R1=R4 и R2 =R 3. Тогда Uвых = (Ux/Uy)Uоп.

Для устранения влияния рассогласования проводимости фоторезисторов в зависимости от входных сигналов и разброса сопротивлений резисторов Rl, R4 последний состоит из постоянного и переменного резисторов. После подстройки R4 можно получить точность деления в пределах ±5% при изменении напряжений на входах X и Y в пределах ±10 В. Если настройка делителя производится при напряжениях на обоих входах, равных Uоп/2, то регулировкой R4 добиваются установления на выходе напряжения, равного Uoп. Так устраняются ошибки, вызванные действием напряжения смещения нуля, входных токов ОУ и рассогласованием проводимостей фоторезисторов.

Первоначально спроектированный для автоматического управления контрастностью в сканирующих электронных микроскопах делитель может быть также полезен в модемах с акустическим согласованием и других устройствах, где необходимо автоматическое управление усилением сигнала в цепи управления процессом [14]. Если используются две фотоэлектронные пары, содержащие каждая светодиод и фоторезистор, то необходимо ввести вторую регулировку в цепи ОС A1. Если заменить ОУ К140УД6 на ОУ К154УДЗ с малосигнальной полосой пропускания около 20 МГц, то ошибка на уровне 5% получается при частоте около 1 МГц, т. е. примерно на порядок больше, чем в исходной схеме. Чтобы обеспечить указанную точность, необходимо подавать на входы Ux и Uy максимальные по амплитуде напряжения, но не больше |Uon|— 2 В для А1 и меньше Uоп для А2. Отметим, что если напряжение U у выйдет за указанные пределы, зависимость выходного напряжения от нап-ряжения Ux останется линейной.

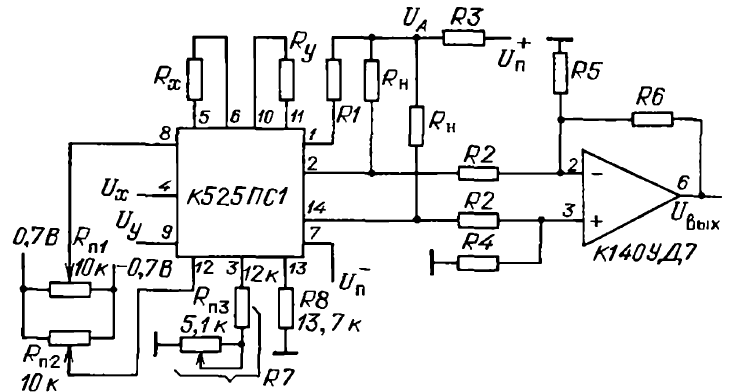

Делитель напряжений можно построить, включив последовательно преобразователь напряжение — частота на таймере и амплитудный модулятор на ОУ (рис. 3.7). В преобразователе напряжение Uy усиленное в R1/R2 раз, поступает на полевой транзистор.

Рисунок 10.7. Схема делителя на основе таймера.

Последний выполняет роль управляемого напряжения времязадающего резистора Rt в мультивибраторе на таймере (см. гл. 7). Сопротивление сток-исток транзистора VT1 равно Rt = R2U0/ R 1 I со, где U0 — напряжение отсечки полевого транзистора, Iсо — ток стока при Uy =0. Конденсатор Ct перезаряжается в процессе работы так, что напряжение на нем остается в диапазоне от Uп/3 до 2Uп/3. Напряжение UХ поступающее на вход модулятора, инвертируется на его выходе, когда открыт транзистор VT2, и передается без инверсии при закрытом транзисторе VT2. Таким образом, на выходе А2 напряжение равно—Ux во время  заряда конденсатора Ct, а во время его разряда tp = 0,7R1CT равно Ux. Среднее значение выходного напряжения за один цикл работы таймера Uвых.c=Ux(tp--t3)/(tp + t3)=UoUx/Uy(1+R1/R) если установить R1 = Uo/2Ico. Для полевого транзистора, у которого U0≈2В и IСО==2 мА, получим R1 =0,5 кОм. Если выбрать R1 = 14R2, то среднее значение выходного напряжения Uвых. с = (Ux/Uу), В, что можно, например, наблюдать на осциллографе, подключив к его выходу резистивно-емкостной фильтр, или измерить это напряжение с помощью низкочастотного вольтметра.

заряда конденсатора Ct, а во время его разряда tp = 0,7R1CT равно Ux. Среднее значение выходного напряжения за один цикл работы таймера Uвых.c=Ux(tp--t3)/(tp + t3)=UoUx/Uy(1+R1/R) если установить R1 = Uo/2Ico. Для полевого транзистора, у которого U0≈2В и IСО==2 мА, получим R1 =0,5 кОм. Если выбрать R1 = 14R2, то среднее значение выходного напряжения Uвых. с = (Ux/Uу), В, что можно, например, наблюдать на осциллографе, подключив к его выходу резистивно-емкостной фильтр, или измерить это напряжение с помощью низкочастотного вольтметра.

10.2 Базовая структура полупроводниковых перемножителей и их параметры

Описанные методы умножения и деления аналоговых сигналов имеют такие недостатки, как нелинейная зависимость от одного или обоих сигналов, ограниченный диапазон изменения выходного напряжения, большое остаточное выходное напряжение при конечном одном из входных сигналов и нулевом втором (так называемое «пролезание»), зависимость Кп от температуры и напряжения источников питания. Главный же их недостаток — громоздкость схем.

Эти недостатки минимизированы в балансных схемах умножения-деления, построеннных на дифференциальных транзисторных каскадах по методу переменной крутизны (см. рис. 3.3 и 3.5). Этот метод основан на использовании экспоненциальной зависимости тока через р-п переход от напряжения [13]. Изменение дифференциального напряжения, приложенного к базам транзисторов дифференциального каскада, вызывает пропорциональное изменение крутизны каскада (см. гл.^2). Основными преимуществами этого метода перемножения являются высокая точность, широкая полоса пропускания и простота реализации в интегральном исполнении. В то же время температурная стабильность таких схем значительно ниже, чем логарифмических перемножителей, что обусловлено зависимостью характеристик транзисторов от температуры. Вместе с тем использование в дифференциальном каскаде идеальной пары интегральных транзисторов позволяет значительно уменьшить температурные погрешности таких перемножителей.

В полупроводниковых микросхемах перемножителей распространение получила разновидность дифференциального каскада на основе трех ДУ, каждый из которых работает в режиме управляемого напряжением делителя тока. Эту разновидность метода переменной крутизны обычно называют методом нормировки токов. На основе этого метода были реализованы первые отечественные перемножители напряжения К140МА1 и К526ПС1, называемые балансными модуляторами. Последнее объясняется тем, что К140МА1 и К526ПС1 сохраняют сравнительно низкую погрешность перемножения только при небольших входных напряжениях. Недостатки первых перемножителей устранены в К525ПС1, а благодаря особенностям структуры этой микросхемы достигнута сравнительно высокая линейность и точность перемножения (1%). В К525ПС1 реализованы возможность регулировки масштабного коэффициента, высокая температурная стабильность передаточной характеристики и широкий диапазон входного напряжения (±10 В).

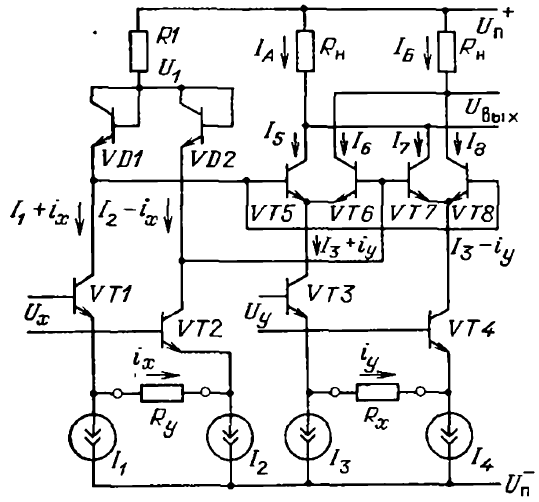

В упрощенной схеме перемножителя К525ПС1 показаны три его основных узла, определяющих параметры и особенности применения микросхемы: узел умножения на транзисторах VT5 — VT8y логарифмический преобразователь напряжения Ux в ток на транзисторах VT 1, VT2 и диодах VD1, VD2 и линейный преобразователь напряжения Uy в ток на транзисторах VT3 и VT4 (рис. 10.8).

В узле умножения в двух дифференциальных каскадах перекрестное включение коллекторов обеспечивает в каждой из объединенных коллекторных цепей противофазные токи, пропорциональные произведению сигнальных токов iy и постоянных составляющих токов генераторов I3; I4. При подключении к дифференциальному выходу узла умножения разностной схемы (например, усилителя разности двух токов) постоянные составляющие выходных токов устраняются и в нагрузке остается сигнал, пропорциональный только произведению сигнальных токов. Если бы на вход узла умножения сигнал Ux подавался, минуя логарифмический преобразователь, то между Ux и Uвых существовала бы экпоненциальная зависимость. Чтобы сделать эту зависимость линейной, напряжение Ux предварительно преобразуется в ток, а затем этот ток логарифмируется с помощью диодов VD 1, VD 2. В результате получается логарифмическая зависимость дифференциального напряжения, поступающего на вход узла перемножения, от Ux и достигается линейная зависимость U вых от Ux.

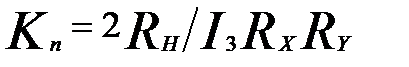

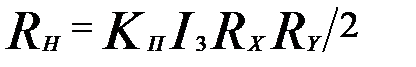

В схеме на рис. 10.8 резисторы Rx , Ry и R 1 и R н являются внешними для К525ПС1. Токи I 1 = I 2 и I 3 = I 4 задаются резисторами, подключаемыми к выводам соответственно 3 и 13 (рис. 10.9). Таким образом, установив токи I 3 и I 13, протекающие по цепям выводов соответственно 3 и 13, получим I 3 = I 1 = I 2 и I 13 I 13 = I 3 = I 4, причем обычно I 3 ≈ I 13. Выходное напряжение перемножителя определяется из соотношения U вых = KnUxUy , где Kn =2 R н / I 3 RxRy .

Рисунок 10.8. Упрощенная схема полупроводникового

перемножителя К525ПС1

Рисунок 10.9. Основная схема включения перемножителя К525ПС1

| Напряжение источников питания | Диапазон входных сигналов | Rx | Ry | R1 | Rн | R2 | R3 | R4 | R5 | R6 | UA |

| В | В | кОм | |||||||||

|

| 15 | 15 | 11 | 11 | 100 | 3,92 | 9,09 | 10 | 100 | 32 |

|

| 15 | 15 | 10 | 8,06 | 100 | 0 | 9,31 | 10 | 127 | 30 |

|

| 15 | 15 | 1,5 | 1,5 | 100 | 0 | 10 | 10 | 759 | 15 |

|

| 8,2 | 8,2 | 3 | 3,4 | 100 | 0 | 9,09 | 10 | 100 | 15 |

|

| 8,2 | 8,2 | 2,5 | 1,5 | 100 | 0 | 9,53 | 10 | 223 | 12 |

|

| 1,5 | 1,5 | 1,3 | 1 | 10 | 0 | 113 | ∞ | 113 | 6 |

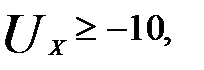

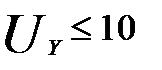

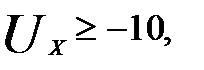

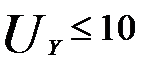

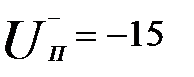

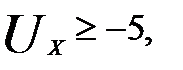

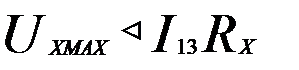

Сопротивления Rx и Ry выбираются так, чтобы при максимальных входных напряжениях нелинейные искажения в схеме были минимальны. Для этого необходимо выполнить неравенства  ,

,  . Если

. Если  , где

, где  .

.

Токи I 3 и I 13 должны быть как можно меньше, чтобы свести к минимуму рассеяние мощности в умножителе. Если, однако, ток I 3 очень мал, то трудно получить требуемую величину K п. Практически приемлемые величины I 3 лежат в диапазоне 0,1...2 мА. Если выбрать I 3= 1 мА, то Rx = RY≥10 кОм. Однако это значение Rx и Ry только гарантирует, что входной сигнал 10 В не вызывет отключения входных усилителей. Во время выбросов входных сигналов эмиттерный ток может достигать нуля, и в усилителе будут возникать нелинейные искажения. Чтобы избежать этого, надо выбирать сопротивления Rx и Ry примерно на 50% больше рассчитанного выше значения, т. е. около 15 кОм. Если  , то

, то  ≈11 кОм.

≈11 кОм.

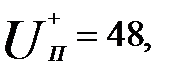

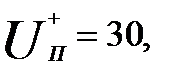

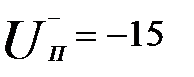

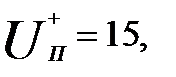

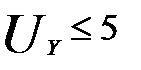

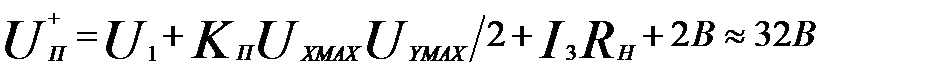

Схема требует трех значений напряжений питания: UI (в точке подключения диодов),  и

и  . Для максимально допустимого входного сигнала ±10 В минимальное значение U 1 = 12 В, а с запасом U1 = 13,5 В. Требуемое положительное напряжение питания

. Для максимально допустимого входного сигнала ±10 В минимальное значение U 1 = 12 В, а с запасом U1 = 13,5 В. Требуемое положительное напряжение питания  определяется из соотношения

определяется из соотношения  , где увеличение напряжения на 2 В обеспечивает запас на нестабильность напряжения

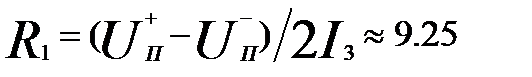

, где увеличение напряжения на 2 В обеспечивает запас на нестабильность напряжения  - Отсюда находим требуемое сопротивление

- Отсюда находим требуемое сопротивление  кОМ. Отрицательное напряжение питания

кОМ. Отрицательное напряжение питания  выбирается так, чтобы при максимальном положительном входном напряжении разность потенциалов между входом и шиной

выбирается так, чтобы при максимальном положительном входном напряжении разность потенциалов между входом и шиной  не превышала максимально допустимую величину 30 В. Кроме того,

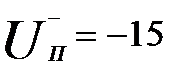

не превышала максимально допустимую величину 30 В. Кроме того,  должно быть по меньшей мере на 2 В меньше отрицательного входного напряжения — 10 В. Поэтому выбирается

должно быть по меньшей мере на 2 В меньше отрицательного входного напряжения — 10 В. Поэтому выбирается  =-15 В.

=-15 В.

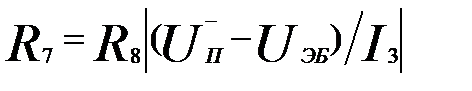

Токи I 3 и I 13 задаются резисторами, подключаемыми между выводами 3, 13 и землей. Сопротивления этих резисторов определяются из выражения  —0,5 кОм. Для получения токов I 3, I 13, равных 1 мА, R7= R8 = 13,75 кОм. При объединенных выводах 3 и 13 достаточно одного резистора с сопротивлением 6,8 кОм.

—0,5 кОм. Для получения токов I 3, I 13, равных 1 мА, R7= R8 = 13,75 кОм. При объединенных выводах 3 и 13 достаточно одного резистора с сопротивлением 6,8 кОм.

Параметры микросхем перемножителей во многом аналогичны параметрам ОУ, за исключением некоторых точностных и динамических характеристик (см. табл. ПЗ). Основным параметром, характеризующим качество перемножителя, является погрешность перемножения. Вычисляемая в процентах от полного диапазона изменения входного напряжения, погрешность определяется как разность между фактическим и теоретическим значениями выходного напряжения перемножителя, предварительно настроенного на минимальную погрешность. Настройка микросхемы на минимальную погрешность перемножения (балансировка) заключается во взаимном уравновешивании статических составляющих погрешности, включающих смещения по входам X и У (разбаланс входных каскадов), смещение на выходе (разбаланс выходного каскада) и погрешность масштабного коэффициента K п. Погрешность перемножения в % определяется из выражения  , где

, где  — фактическое выходное напряжение. Например, для К525ПС1 погрешность 1% при Ux = Uy = 10 В соответствует напряжению 0,1 В.

— фактическое выходное напряжение. Например, для К525ПС1 погрешность 1% при Ux = Uy = 10 В соответствует напряжению 0,1 В.

Основной составляющей погрешности перемножения является нелинейность перемножения, измеряемая по обоим входам X и У. Эта погрешность определяется как половина от пикового значения амплитуды отклонения реального выходного напряжения от идеального в процентах к максимальному входному напряжению  , где

, где  , В.

, В.

Если на один вход перемножителя подается конечное напряжение, а напряжение на втором входе равно нулю,  = 0. В реальном перемножителе

= 0. В реальном перемножителе  и его значение определяет остаточное напряжение Uостx или Uостн.

и его значение определяет остаточное напряжение Uостx или Uостн.

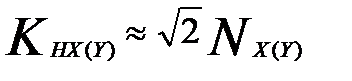

Динамические параметры микросхем перемножителей аналогичны ОУ. Основные отличия состоят в определении частотных характеристик. Полоса пропускания перемножителя измеряется при максимальном по амплитуде постоянном сигнале на одном входе и 10%-ном от этого сигнала синусоидальном напряжении на другом. При увеличении частоты синусоидального сигнала фиксируется значение частоты, когда  , где

, где  — выходное напряжение при низкой частоте. Таким образом определяется полоса пропускания на уровне 3 дБ спада выходного напряжения. Одновременно может быть измерена частота, при которой амплитуда выходного напряжения уменьшится на 1%. Эта частота называется граничной частотой амплитудной погрешности перемножителя. К динамическим параметрам перемножителей относят также частотные зависимости дифференциального смещения фаз входных сигналов и коэффициента нелинейных искажений выходного напряжения Кн. Дифференциальный сдвиг фаз входных сигналов характеризует перемножители, у которых в исходном состоянии разность фаз сигналов по входам X и Y не равна нулю. Зависимость от частоты коэффициента нелинейных искажений

— выходное напряжение при низкой частоте. Таким образом определяется полоса пропускания на уровне 3 дБ спада выходного напряжения. Одновременно может быть измерена частота, при которой амплитуда выходного напряжения уменьшится на 1%. Эта частота называется граничной частотой амплитудной погрешности перемножителя. К динамическим параметрам перемножителей относят также частотные зависимости дифференциального смещения фаз входных сигналов и коэффициента нелинейных искажений выходного напряжения Кн. Дифференциальный сдвиг фаз входных сигналов характеризует перемножители, у которых в исходном состоянии разность фаз сигналов по входам X и Y не равна нулю. Зависимость от частоты коэффициента нелинейных искажений  для входов X и Y измеряют обычно с помощью анализатора нелинейных искажений. Как правило, оказывается справедливым соотношение

для входов X и Y измеряют обычно с помощью анализатора нелинейных искажений. Как правило, оказывается справедливым соотношение  .

.

Дата: 2019-02-19, просмотров: 1102.