13.1. Общие сведения о компараторах

Компаратор - это устройство сравнения. Аналоговый компаратор предназначен для сравнения величин двух аналоговых сигналов. Если обозначить входной анализируемый сигнал  , а опорный сигнал (или уровень сравнения)

, а опорный сигнал (или уровень сравнения)  то выходной сигнал компаратора

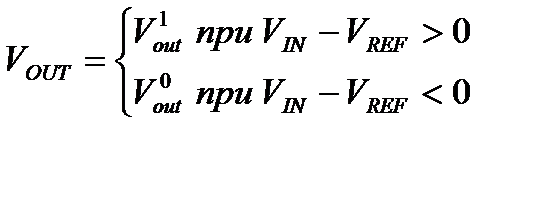

то выходной сигнал компаратора  - (представляющий собой логический сигнал, содержащий 1 бит информации) будет определяться по правилу

- (представляющий собой логический сигнал, содержащий 1 бит информации) будет определяться по правилу

Выходной сигнал компаратора в большинстве случаев подается на входы логических устройств и потому согласуется по уровню и мощности с их входами. Таким образом, компаратор - это элемент перехода от аналоговых к цифровым сигналам, и по сути дела является одноразрядным аналого-цифровым преобразователем.

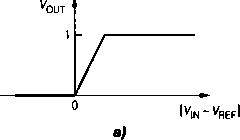

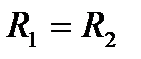

Неопределенность состояния выхода компаратора при разности входных сигналов  нет необходимости уточнять, так как реальный компаратор всегда имеет либо конечный коэффициент усиления (Рис. 13.1а), либо петлю гистерезиса (Рис. 13.1б).

нет необходимости уточнять, так как реальный компаратор всегда имеет либо конечный коэффициент усиления (Рис. 13.1а), либо петлю гистерезиса (Рис. 13.1б).

Рисунок 13.1. Характеристики компараторов (при  ): а – с конечным коэффициентом усиления, б – с гистерезисом (

): а – с конечным коэффициентом усиления, б – с гистерезисом (  – ширина петли гистерезиса)

– ширина петли гистерезиса)

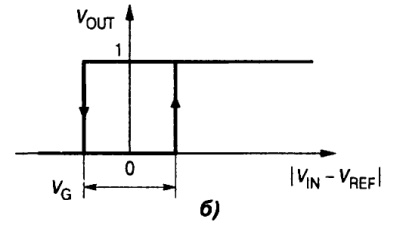

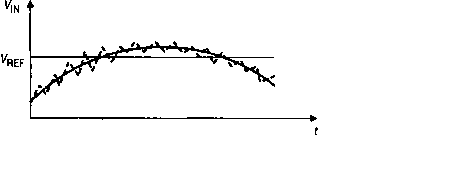

Чтобы выходной сигнал компаратора изменился на конечную величину  при бесконечно малом изменении входного сигнала, компаратор должен был бы иметь бесконечно большой коэффициент усиления (Рис. 13.2 б -1) и работать при полном отсутствии шумов.

при бесконечно малом изменении входного сигнала, компаратор должен был бы иметь бесконечно большой коэффициент усиления (Рис. 13.2 б -1) и работать при полном отсутствии шумов.

К такой характеристике можно приблизится двумя способами: либо использовать усилитель с очень большим коэффициентом усиления, либо ввести

положительную обратную связь. В первом случае при  характеристика компаратора будет иметь вид Рис. 13.1а. Это приводит к двум неприятным последствиям. Прежде всего, при очень медленном изменении

характеристика компаратора будет иметь вид Рис. 13.1а. Это приводит к двум неприятным последствиям. Прежде всего, при очень медленном изменении  выходной сигнал также будет изменяться замедленно (Рис. 13.2 б - 2), что может вызвать нечеткое срабатывание последующих логических схем. Еще хуже то, что при таком медленном изменении

выходной сигнал также будет изменяться замедленно (Рис. 13.2 б - 2), что может вызвать нечеткое срабатывание последующих логических схем. Еще хуже то, что при таком медленном изменении  около

около  может появиться так называемый «дребезг», при котором выход компаратора многократно с большой частотой меняет свое состояние под действием помех или шумов (Рис. 4.2б-3). Для устранения этого явления обычно вводят положительную обратную связь, которая обеспечивает переходной характеристике компаратора гистерезис (Рис. 4.1б). Наличие гистерезиса хотя и вызывает некоторую задержку в переключении компаратора (Рис. 4.2б-4), но существенно уменьшает или даже полностью устраняет «дребезг»

может появиться так называемый «дребезг», при котором выход компаратора многократно с большой частотой меняет свое состояние под действием помех или шумов (Рис. 4.2б-3). Для устранения этого явления обычно вводят положительную обратную связь, которая обеспечивает переходной характеристике компаратора гистерезис (Рис. 4.1б). Наличие гистерезиса хотя и вызывает некоторую задержку в переключении компаратора (Рис. 4.2б-4), но существенно уменьшает или даже полностью устраняет «дребезг»

a)

б)

Рисунок 13.2. Временные диаграммы переключения компараторов: а – входные напряжения, б – выходные напряжения компараторов с бесконечным усилением (1), с конечным усилением(2), при наличии внутреннего или входного шума (3), с гистерезисом (4)

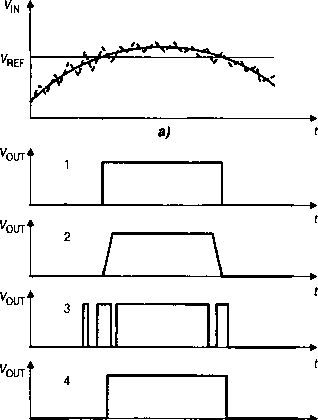

Рисунок 13.3. Схема компаратора на ОУ

В качестве компаратора может быть использован и обычный операционный усилитель (ОУ), как это показано на Рис. 13.3. Усилитель включен по схеме инвертирующего сумматора, однако вместо резистора в цепи обратной связи включены параллельно стабилитрон  и диод

и диод  .

.

Пусть  . Если

. Если  , то диод

, то диод  открыт и выходное напряжение схемы равно падению напряжения на открытом диоде и не превышает 0.5...0.7 В. При

открыт и выходное напряжение схемы равно падению напряжения на открытом диоде и не превышает 0.5...0.7 В. При  на стабилитроне установится напряжение, равное его напряжению стабилизации

на стабилитроне установится напряжение, равное его напряжению стабилизации  . Это напряжение должно соответствовать единичному логическому уровню цифровых интегральных микросхем, входы которых подключены к выходу компаратора. Таким образом, выход ОУ принимает два состояния, причем в обоих усилитель работает в линейном режиме. Многие типы ОУ не допускают сколько-нибудь существенное входное дифференциальное напряжение. ОУ, включенный по схеме, приведенной на Рис. 13.3, работает в режиме компаратора практически с нулевыми дифференциальными и синфазными входными напряжениями. Недостатком данной схемы является относительно низкое быстродействие, обусловленное необходимостью частотной коррекции, так как ОУ работает в линейном режиме со 100% отрицательной обратной связью. Поэтому в компараторах на обычных ОУ трудно получить время переключения менее 1 мкс.

. Это напряжение должно соответствовать единичному логическому уровню цифровых интегральных микросхем, входы которых подключены к выходу компаратора. Таким образом, выход ОУ принимает два состояния, причем в обоих усилитель работает в линейном режиме. Многие типы ОУ не допускают сколько-нибудь существенное входное дифференциальное напряжение. ОУ, включенный по схеме, приведенной на Рис. 13.3, работает в режиме компаратора практически с нулевыми дифференциальными и синфазными входными напряжениями. Недостатком данной схемы является относительно низкое быстродействие, обусловленное необходимостью частотной коррекции, так как ОУ работает в линейном режиме со 100% отрицательной обратной связью. Поэтому в компараторах на обычных ОУ трудно получить время переключения менее 1 мкс.

13.2. Аналоговый интегральный компаратор

Принципы построения интегральных компараторов.

Итак, компаратор - это быстродействующий дифференциальный усилитель постоянного тока с большим усилением, малым дрейфом, малым смещением нуля и логическим выходом. Его входной каскад должен обладать большим коэффициентом ослабления синфазного сигнала (КОСС) и способностью выдерживать большие синфазные и дифференциальные напряжения на входах, не попадая в режим насыщения, приводящий к значительному снижению быстродействия. Для повышения помехозащищенности желательно снабдить компаратор стробирующим логическим входом, разрешающим сравнение и переключение компаратора только в задаваемые внешним (тактовым) сигналом моменты времени.

Рисунок 13.4. Схема компаратора µА710

Схема первого промышленного интегрального компаратора µА710 (отечественный аналог – 521СА2), разработанного Р. Видларом в 1965 г. [4.1], приведена на Рис. 13.4.

Она представляет собой дифференциальный усилитель на транзисторах  ,

,  , нагруженный на каскады ОЭ на

, нагруженный на каскады ОЭ на  и

и  . Каскад на

. Каскад на  через транзистор

через транзистор  управляет коллекторным режимом входного каскада и через транзистор в диодном включении

управляет коллекторным режимом входного каскада и через транзистор в диодном включении  фиксирует потенциал базы транзистора VT8, делая его независимым от изменений положительного напряжения питания. Каскад на

фиксирует потенциал базы транзистора VT8, делая его независимым от изменений положительного напряжения питания. Каскад на  представляет собой второй каскад усиления напряжения. Эмиттерные выводы транзисторов

представляет собой второй каскад усиления напряжения. Эмиттерные выводы транзисторов  и

и  подключены к стабилитрону

подключены к стабилитрону  с напряжением стабилизации 6.2 В, поэтому (с учетом падения напряжения на переходах база -эмиттер) потенциалы баз указанных транзисторов соответствуют = 6.9 В. Следовательно, допустимое напряжение на входах компаратора относительно общей точки может достигать 7 В. На транзисторе

с напряжением стабилизации 6.2 В, поэтому (с учетом падения напряжения на переходах база -эмиттер) потенциалы баз указанных транзисторов соответствуют = 6.9 В. Следовательно, допустимое напряжение на входах компаратора относительно общей точки может достигать 7 В. На транзисторе  выполнен эмиттерный повторитель, передающий сигнал с коллектора

выполнен эмиттерный повторитель, передающий сигнал с коллектора  на выход. Постоянный уровень выходного сигнала смещается к нулю стабилитроном

на выход. Постоянный уровень выходного сигнала смещается к нулю стабилитроном  .

.

Если дифференциальное входное напряжение превышает +5...+10 мВ, то транзистор  закрыт, a

закрыт, a  близок к насыщению. Выходной сигнал компаратора при этом не может превысить +4 В, так как при более положительных сигналах открывается диод, выполненный на транзисторе

близок к насыщению. Выходной сигнал компаратора при этом не может превысить +4 В, так как при более положительных сигналах открывается диод, выполненный на транзисторе  в диодном включении, не допуская излишнего роста выходного напряжения и насыщения

в диодном включении, не допуская излишнего роста выходного напряжения и насыщения  . При обратном знаке входного напряжения

. При обратном знаке входного напряжения  насыщается, потенциал его коллектора оказывается близок к напряжению стабилизации стабилитронов

насыщается, потенциал его коллектора оказывается близок к напряжению стабилизации стабилитронов  и

и  , а поэтому потенциал выхода близок к нулю. Транзистор

, а поэтому потенциал выхода близок к нулю. Транзистор  – источник тока 3 мА для начального смещения

– источник тока 3 мА для начального смещения  и

и  . Часть этого тока (до 1.6 мА) может ответвляться в нагрузку с вытекающим (отрицательным) входным током (например, при подключении одного входа ИМС ТТЛ серии 155 или 133).

. Часть этого тока (до 1.6 мА) может ответвляться в нагрузку с вытекающим (отрицательным) входным током (например, при подключении одного входа ИМС ТТЛ серии 155 или 133).

В дальнейшем схема этого компаратора развивалась и совершенствовалась. Схемы многих современных компараторов имеют стробирующий вход для синхронизации, а некоторые модификации снабжены на выходе триггерами защелками, фиксирующими состояние выхода компаратора в момент прихода синхроимпульса.

Рисунок 13.5. Варианты включения выходного каскада компаратора 521 САЗ: а – по схеме с ОЭ, б – по схеме эмиттерного повторителя

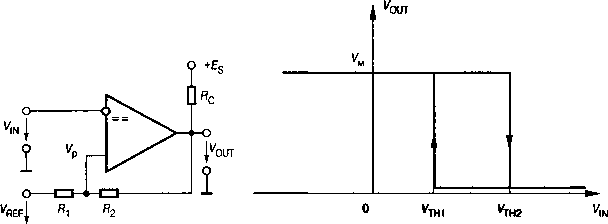

Выходные каскады компараторов обычно обладают большей гибкостью, чем выходные каскады операционных усилителей. В обычном ОУ используют двухтактный выходной каскад, который обеспечивает размах напряжения в интервале между уровнями напряжения питания (например, ±13 В для ОУ типа 140УД7, работающего от источников ±15 В). В выходном каскаде компаратора эмиттер, как правило, заземлен, а выходной сигнал снимается с «открытого» коллектора. Выходные транзисторы некоторых типов компараторов, например, 521САЗ или LM311, имеют открытые (т. е. неподключенные) не только коллектор, но и эмиттер. Две основные схемы включения компараторов такого типа приведены на Рис. 13.5 [4.2].

На Рис. 13.5са выходной транзистор компаратора включен по схеме с общим эмиттером (ОЭ). При потенциале на верхнем выводе резистора, равном +5 В к выходу можно подключать входы TTЛ, nМОП- и КМОП - логику с напряжением питания 5 В. Для управления КМОП - логикой с более высоким напряжением питания следует верхний вывод резистора подключить к источнику питания используемой цифровой микросхемы.

Если требуется изменение выходного напряжения компаратора в пределах от  до

до  , выходной каскад включается по схеме эмиттерного повторителя (ЭП) (Рис. 13.5 б). При этом заметно снижается быстродействие компаратора и, кроме того, в отличие от схемы на Рис. 13.5 а выходной сигнал компаратора инвертируется относительно входного.

, выходной каскад включается по схеме эмиттерного повторителя (ЭП) (Рис. 13.5 б). При этом заметно снижается быстродействие компаратора и, кроме того, в отличие от схемы на Рис. 13.5 а выходной сигнал компаратора инвертируется относительно входного.

Некоторые модели интегральных компараторов (например, AD790, МАХ907) имеют внутреннюю неглубокую положительную обратную связь, обеспечивающую их переходной характеристике гистерезис с шириной петли, соизмеримой с напряжением смещения нуля.

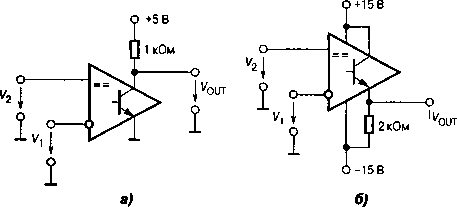

На Рис. 13.6 а приведена схема включения компаратора с открытым коллектором на выходе, переходная характеристика которого имеет гистерезис (Рис. 13.6 б).

а) б)

Рисунок 13.6. Компаратор с положительной обратной связью: a – схема включения, 6 – переходная характеристика с гистерезисом

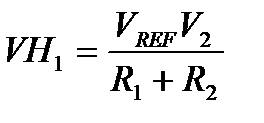

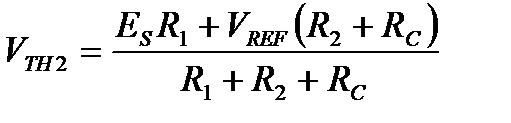

Пороговые напряжения этой схемы определяются по формулам

,

,  . (13.1)

. (13.1)

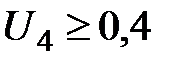

Из-за асимметрии выходных напряжений компаратора петля гистерезиса оказывается несимметричной относительно опорного напряжения. Обычно выбирают  , так что

, так что

.

.

Компараторы с однополярным питанием.

Компараторы с однополярным питанием удобны для использования в носимой аппаратуре, имеющей батарейное питание, легко сопрягаются с КМОП и ТТЛ цифровыми схемами, поэтому они получили широкое распространение. Одна из первых моделей LM139/239/339 (отечественный аналог – 1401СА1), была создана Р. Видларом в начале 70-х годов прошлого века и оказалась настолько удачной, что и поныне выпускается несколькими фирмами в больших количествах и многих модификациях (LM3302, LM393, TL331 и др.). ИМС LM139 представляет собой маломощный счетверенный компаратор среднего быстродействия с выходом в виде биполярного транзистора с открытым коллектором.

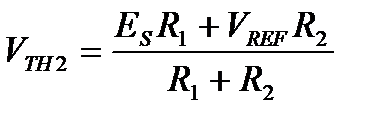

Схема входного каскада одного их четырех компараторов LM139 приведена на Рис. 13.7.

Рисунок 13.7. Схема входного усилительного каскада компаратора LM139

Транзисторы  , включенные попарно по схеме Дарлингтона, составляют p-n-p-дифференциальный входной каскад с нагрузкой в виде токового зеркала на транзисторах

, включенные попарно по схеме Дарлингтона, составляют p-n-p-дифференциальный входной каскад с нагрузкой в виде токового зеркала на транзисторах  и

и  . Это позволяет преобразовать дифференциальный входной сигнал в несимметричный выходной без потери усиления. Такое включение позволяет оперировать с синфазными входными сигналами, сниженными вплоть до потенциала общей шины (земли). Если оба входа имеют потенциал общей шины, то напряжения эмиттеров транзисторов

. Это позволяет преобразовать дифференциальный входной сигнал в несимметричный выходной без потери усиления. Такое включение позволяет оперировать с синфазными входными сигналами, сниженными вплоть до потенциала общей шины (земли). Если оба входа имеют потенциал общей шины, то напряжения эмиттеров транзисторов  и

и  относительно общей шины равны

относительно общей шины равны  , а эмиттеров транзисторов

, а эмиттеров транзисторов  и

и  . Для переключения компаратора достаточно, чтобы потенциалы коллекторов транзисторов

. Для переключения компаратора достаточно, чтобы потенциалы коллекторов транзисторов  и

и  токового зеркала были бы выше потенциала общей шины на величину

токового зеркала были бы выше потенциала общей шины на величину  . Поскольку транзисторы

. Поскольку транзисторы  и

и  могут работать с нулевыми напряжениями коллектор–база, то компаратор нормально работает при

могут работать с нулевыми напряжениями коллектор–база, то компаратор нормально работает при  В. Однако при переходе через эту границу, может произойти отпирание диода подложки, что приведет к непредсказуемому состоянию выхода или даже к повреждению компаратора, если входные токи не ограничены.

В. Однако при переходе через эту границу, может произойти отпирание диода подложки, что приведет к непредсказуемому состоянию выхода или даже к повреждению компаратора, если входные токи не ограничены.

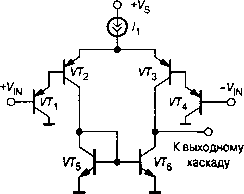

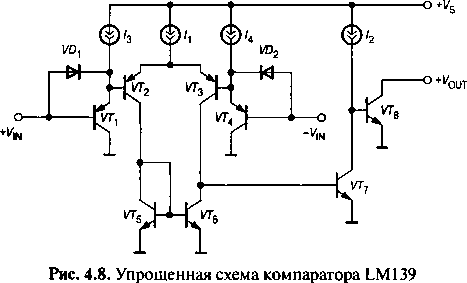

На Рис. 13.8 показана упрощенная схема компаратора LM139 с выходным каскадом.

Рисунок 13.8. Упрощенная схема компаратора LM139

В каскадах с общим эмиттером на транзисторах  и

и  осуществляется дополнительное усиление разностного сигнала. Коллектор транзистора

осуществляется дополнительное усиление разностного сигнала. Коллектор транзистора  оставлен открытым, чтобы обеспечить более гибкое применение компаратора. Включение нагрузочного, так называемого «подтягивающего» (pull-up), резистора между коллектором

оставлен открытым, чтобы обеспечить более гибкое применение компаратора. Включение нагрузочного, так называемого «подтягивающего» (pull-up), резистора между коллектором  и

и  или любым другим источником питания с напряжением вплоть до +36 В позволяет управлять сравнительно мощной нагрузкой, например, индикаторами или реле. Несколько выходов могут быть соединены вместе, для того, чтобы обеспечить логическую операцию «проводное (монтажное) И/ИЛИ». Транзистор

или любым другим источником питания с напряжением вплоть до +36 В позволяет управлять сравнительно мощной нагрузкой, например, индикаторами или реле. Несколько выходов могут быть соединены вместе, для того, чтобы обеспечить логическую операцию «проводное (монтажное) И/ИЛИ». Транзистор  в полностью открытом состоянии обеспечивает ток коллектора (нагрузки) до 15 мА. При этом его напряжение коллектор-эмиттер не превышает 1 В. При коллекторном токе 4 мА типичное значение этого напряжения составляет 0.25 В.

в полностью открытом состоянии обеспечивает ток коллектора (нагрузки) до 15 мА. При этом его напряжение коллектор-эмиттер не превышает 1 В. При коллекторном токе 4 мА типичное значение этого напряжения составляет 0.25 В.

Источники тока  и

и  по 3.5 мкА каждый используются для ускорения перезаряда паразитных емкостей эмиттеров транзисторов

по 3.5 мкА каждый используются для ускорения перезаряда паразитных емкостей эмиттеров транзисторов  и

и  , что увеличивает скорость нарастания входного каскада. Диоды

, что увеличивает скорость нарастания входного каскада. Диоды  и

и  установлены для защиты от пробоя перехода база–эмиттер транзисторов

установлены для защиты от пробоя перехода база–эмиттер транзисторов  и

и  при больших колебаниях входного напряжения.

при больших колебаниях входного напряжения.

Скоростные компараторы.

Быстродействие универсальных компараторов типа рА710, LM111 и LM139 не всегда достаточно. Для цифровых ИМС типа ТТЛШ или ЭСЛ достижимо быстродействие на уровне 1...10 не, поэтому желательно обеспечить такую скорость и для аналогового компаратора.

Быстродействие компараторов, работающих без обратной связи с большими входными токами, можно увеличить за счет совершенствования схемотехники и интегральных структур. Один из основных принципов проектирования:

биполярные транзисторы, входящие в состав компаратора, ни при каких допустимых режимах не должны входить в состояние насыщения. В компараторах этого труднее избежать, чем в ОУ, поскольку:

· на входах компаратора в нормальном режиме работы могут быть большие дифференциальные и синфазные напряжения;

· выходные каскады компараторов представляют собой логические элементы, работающие в ключевом режиме.

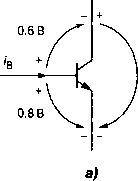

Один из путей устранения насыщения транзисторов заключается в шунтировании перехода база–коллектор диодом Шоттки. На Рис. 13.9 приведены упрощенные схемы транзисторных ключей с указанием разностей потенциалов между выводами в открытом состоянии.

Рисунок 13.9. Упрощенные схемы ключей на биполярных транзисторах: а – без диода Шоттки, б – с диодом Шоттки, шунтирующим переход база-коллектор ключа

Ключ без диода Шоттки (Рис. 13.9 а) находится в глубоком насыщении. При его переводе в режим отсечки требуется значительное время на рассасывание избыточных зарядов в базе. Включение диода Шоттки (Рис. 13.9 б), имеющего низкое прямое падение напряжения и малое время восстановления, позволяет исключить переход транзистора в режим насыщения. При этом избыточный входной ток ключа ID ответвляется через диод в цепь коллектора, что устраняет накопление неосновных носителей в базовой области транзистора происходящее в режиме насыщения. Тем самым обеспечивается наименьшее время выхода транзистора из открытого состояния. Применение этого принципа при построении скоростного компаратора SE527 (отечественный аналог – 521СА4) позволило снизить время переключения до 15 не. Диоды Шоттки использованы также в выходном каскаде скоростного компаратора TL714C, имеющего время переключения 6 нс. Дальнейшее повышение быстродействия достигается построением всех каскадов компаратора на дифференциальных парах, которые всегда работают в линейном режиме. Это наиболее удобно в случае, когда компаратор предназначен для работы с ЭСЛ - логикой, основой схемотехники которой также являются дифференциальные пары транзисторов. Примером такого компаратора может служить МАХ9692, типичное время переключения которого составляет 1.2 нс.

Для повышения скорости нарастания выходного напряжения входные каскады скоростных компараторов выполняют по схеме, аналогичной схеме ОУ с токовой обратной связью (см. Рис. 3.7 в главе 3). Именно так построен входной каскад компаратора TL714C.

В заключение перечислим некоторые особенности компараторов по сравнению с ОУ:

· несмотря на то что компараторы очень похожи на операционные усилители, в них почти никогда не используют отрицательную обратную связь, так как в этом случае весьма вероятно (а при наличии внутреннего гистерезиса – гарантировано) самовозбуждение;

· в связи с тем что в схеме нет отрицательной обратной связи, напряжения на входах компаратора неодинаковы;

· из-за отсутствия отрицательной обратной связи входное сопротивление компаратора относительно невелико и может меняться при изменении входных сигналов;

· выходное сопротивление компараторов значительно и различно для разной полярности выходного напряжения.

13.3. Применение компараторов

Двухпороговый компаратор.

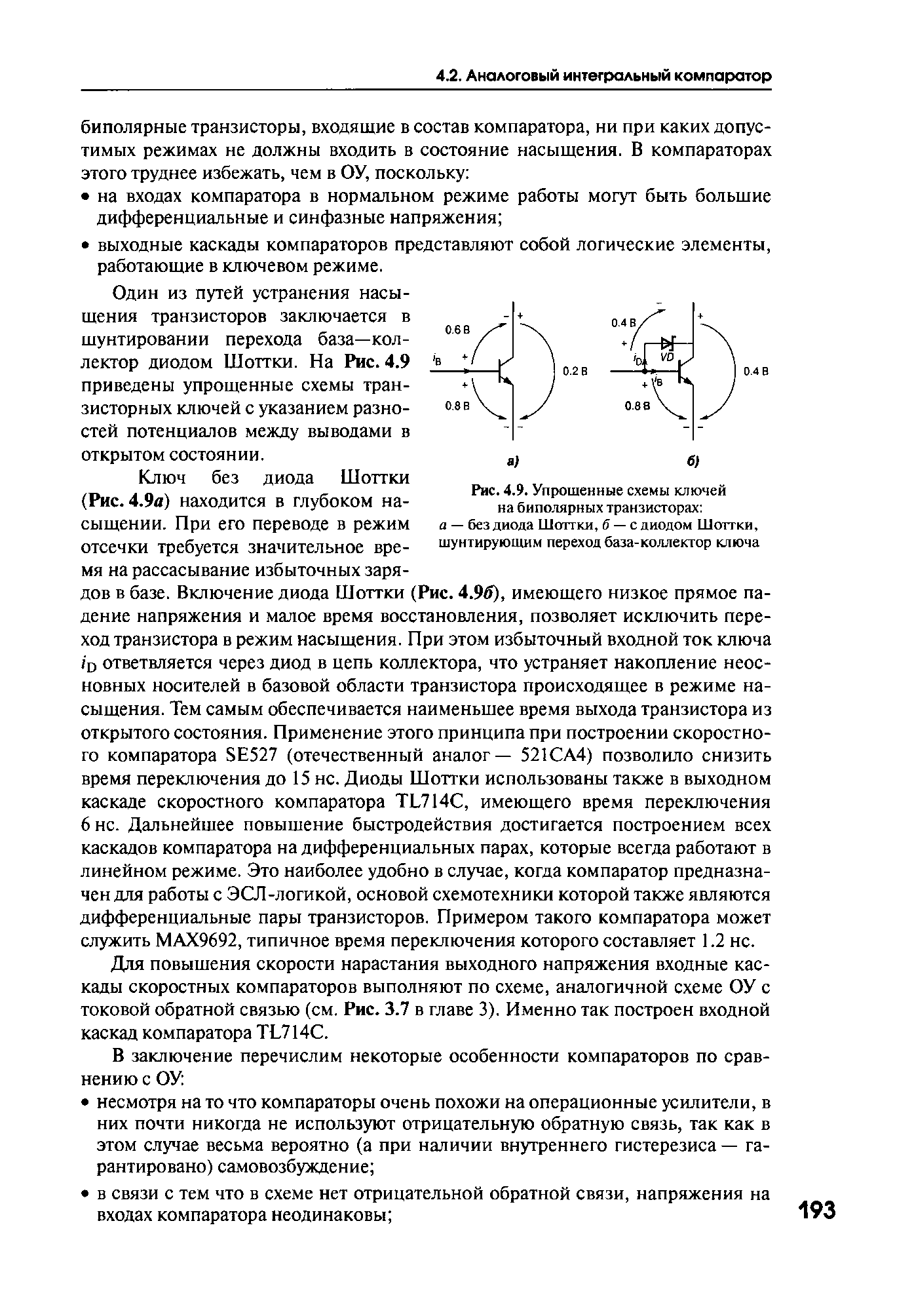

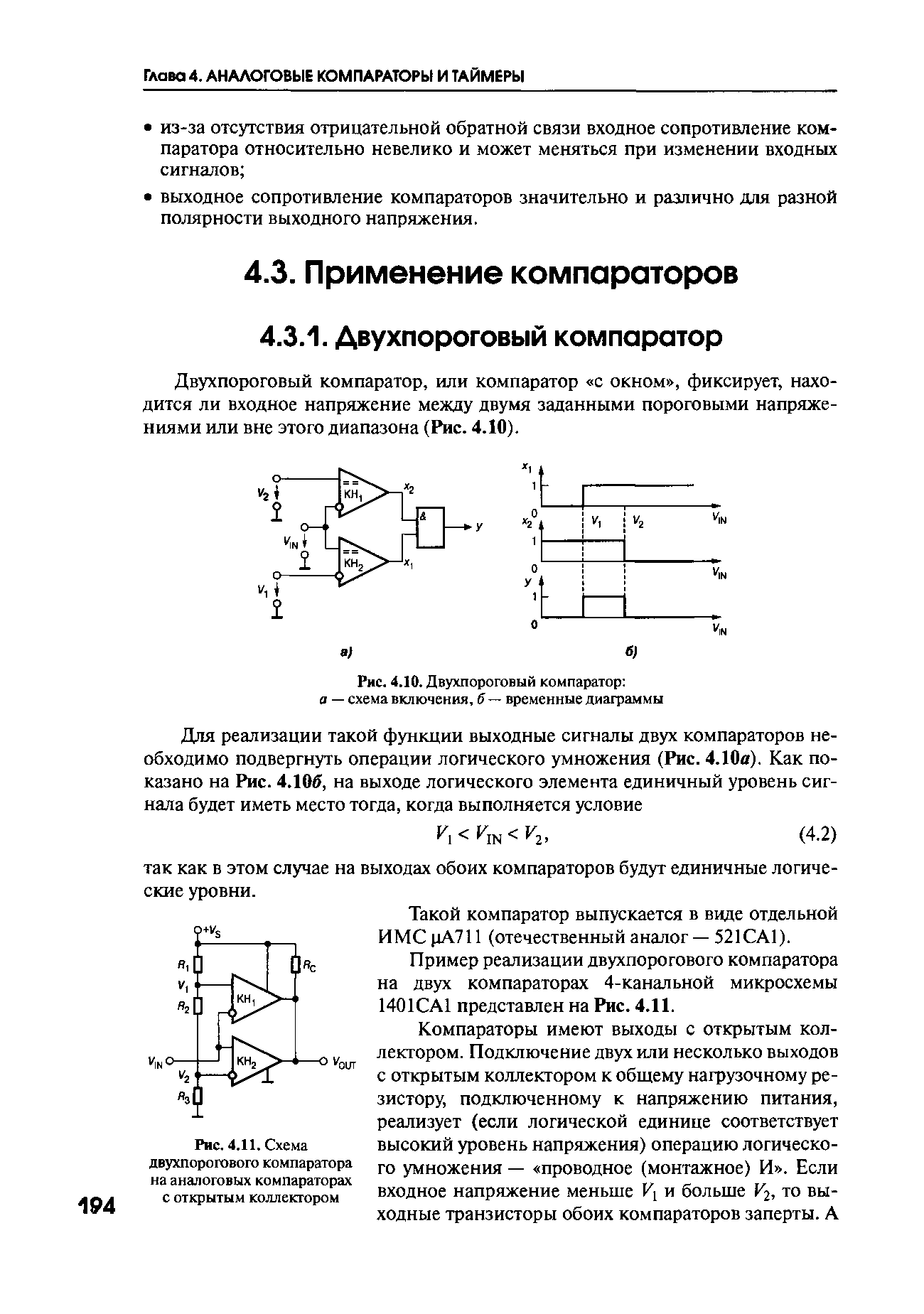

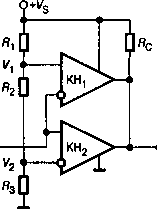

Двухпороговый компаратор, или компаратор «с окном», фиксирует, находится ли входное напряжение между двумя заданными пороговыми напряжениями или вне этого диапазона (Рис. 13.10).

Рис. 13.10. Двухпороговый компаратор: а – схема включения, б – временные диаграммы

Для реализации такой функции выходные сигналы двух компараторов необходимо подвергнуть операции логического умножения (Рис. 4.10 а). Как показано на Рис. 4.10 б, на выходе логического элемента единичный уровень сигнала будет иметь место тогда, когда выполняется условие

, (13.2)

, (13.2)

так как в этом случае на выходах обоих компараторов будут единичные логические уровни.

Пример реализации двухпорогового компаратора на двух компараторах 4-канальной микросхемы 1401СА1 представлен на Рис. 13.11.

Рисунок 13.11. Схема двухпорогового компаратора на аналоговых компараторах с открытым коллектором

Такой компаратор выпускается в виде отдельной ИМС µА711 (отечественный аналог – 521СА1).

Компараторы имеют выходы с открытым коллектором. Подключение двух или несколько выходов с открытым коллектором к общему нагрузочному резистору, подключенному к напряжению питания, реализует (если логической единице соответствует высокий уровень напряжения) операцию логического умножения – «проводное (монтажное) И». Если входное напряжение меньше  и больше

и больше  , то выходные транзисторы обоих компараторов заперты. А так как выход схемы соединяется с напряжением питания через нагрузочный резистор

, то выходные транзисторы обоих компараторов заперты. А так как выход схемы соединяется с напряжением питания через нагрузочный резистор  , то выходное напряжение имеет высокий уровень. В противном случае какой-либо из транзисторов остается открытым, и на выходе устанавливается низкий уровень напряжения. Значения пороговых напряжений определяются выбором резисторов

, то выходное напряжение имеет высокий уровень. В противном случае какой-либо из транзисторов остается открытым, и на выходе устанавливается низкий уровень напряжения. Значения пороговых напряжений определяются выбором резисторов  ,

,  ,

,  .

.

Детектор пересечения нуля.

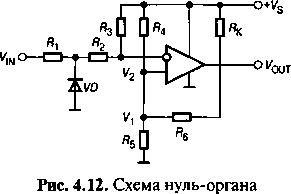

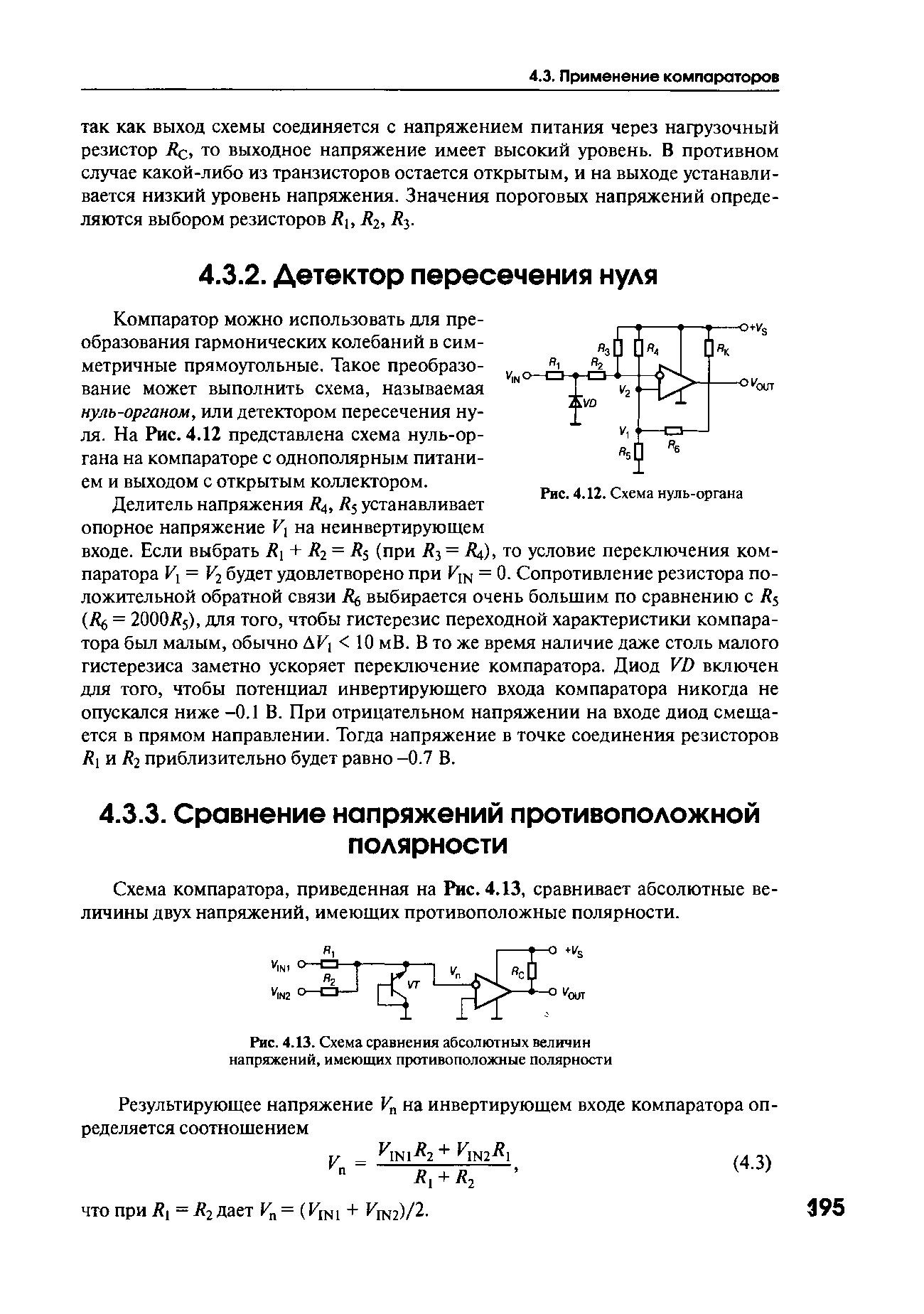

Компаратор можно использовать для преобразования гармонических колебаний в симметричные прямоугольные. Такое преобразование может выполнить схема, называемая нуль - органом, или детектором пересечения нуля. На Рис. 13.12 представлена схема нуль - органа на компараторе с однополярным питанием и выходом с открытым коллектором.

Рис. 13.12. Схема нуль – органа

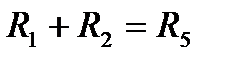

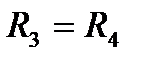

Делитель напряжения  ,

,  устанавливает опорное напряжение

устанавливает опорное напряжение  на не инвертирующем входе. Если выбрать

на не инвертирующем входе. Если выбрать  (при

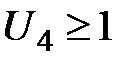

(при  ), то условие переключения компаратора

), то условие переключения компаратора  будет удовлетворено при

будет удовлетворено при  . Сопротивление резистора положительной обратной связи

. Сопротивление резистора положительной обратной связи  выбирается очень большим по сравнению с

выбирается очень большим по сравнению с  (

(  ), для того, чтобы гистерезис переходной характеристики компаратора был малым, обычно

), для того, чтобы гистерезис переходной характеристики компаратора был малым, обычно  10 мВ. В то же время наличие даже столь малого гистерезиса заметно ускоряет переключение компаратора. Диод

10 мВ. В то же время наличие даже столь малого гистерезиса заметно ускоряет переключение компаратора. Диод  включен для того, чтобы потенциал инвертирующего входа компаратора никогда не опускался ниже –0.1 В. При отрицательном напряжении на входе диод смещается в прямом направлении. Тогда напряжение в точке соединения резисторов R1 и R2 приблизительно будет равно -0.7 В.

включен для того, чтобы потенциал инвертирующего входа компаратора никогда не опускался ниже –0.1 В. При отрицательном напряжении на входе диод смещается в прямом направлении. Тогда напряжение в точке соединения резисторов R1 и R2 приблизительно будет равно -0.7 В.

Сравнение напряжений противоположной полярности.

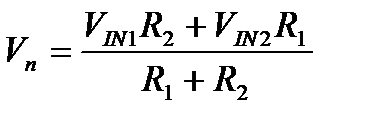

Схема компаратора, приведенная на Рис. 13.13, сравнивает абсолютные величины двух напряжений, имеющих противоположные полярности.

Рисунок 13.13. Схема сравнения абсолютных величин напряжений, имеющих противоположные полярности

Результирующее напряжение  на инвертирующем входе компаратора определяется соотношением

на инвертирующем входе компаратора определяется соотношением

, (13.3)

, (13.3)

что при  дает

дает  .

.

Транзистор VT в диодном включении защищает вход компаратора от отрицательных перенапряжений, что требуется в случае, если компаратор имеет однополярное питание. Если необходимо, небольшой гистерезис переходной характеристики компаратора может быть получен методами, рассмотренными выше. Выходное напряжение схемы принимает высокий уровень  в том случае, если положительное напряжение по абсолютной величине меньше отрицательного.

в том случае, если положительное напряжение по абсолютной величине меньше отрицательного.

Тема 14. Аналоговые таймеры

14.1. Принципы построения таймеров

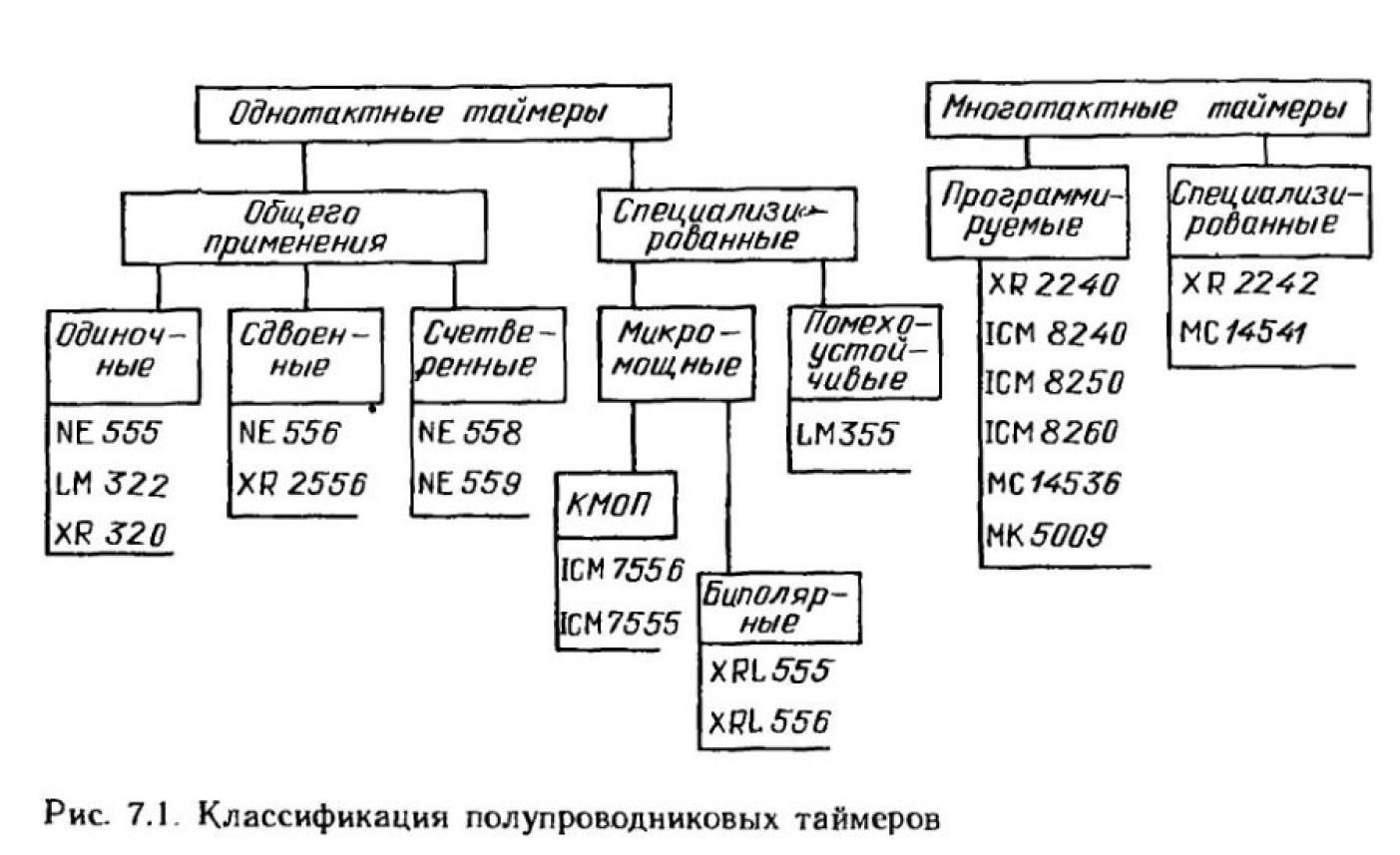

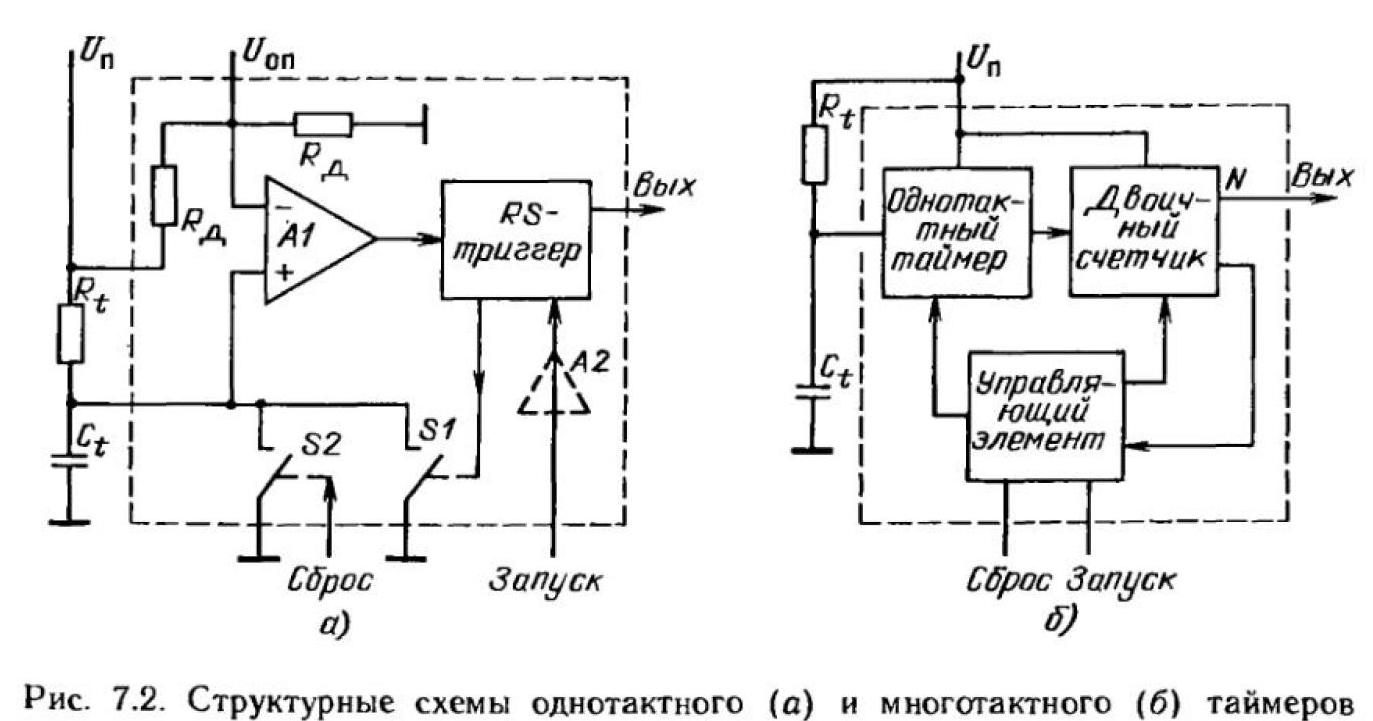

Семейство однотактных таймеров можно разделить на две группы: таймеры общего применения и специализированные таймеры (рис. 14.1). В однотактном таймере (рис. 14.2, а) длительность формируемого интервала времени определяется током заряда внешнего времязадающего конденсатора  , а ток заряда

, а ток заряда  - сопротивлением внешнего времязадающего резистора

- сопротивлением внешнего времязадающего резистора  . Формируемый таймером временной интервал

. Формируемый таймером временной интервал  пропорционален постоянной времени

пропорционален постоянной времени  - цепи и определяется длительностью изменения напряжения на Ct в пределах некоторого диапазона, установленного внутренним резисторным делителем таймера.

- цепи и определяется длительностью изменения напряжения на Ct в пределах некоторого диапазона, установленного внутренним резисторным делителем таймера.

Рисунок 14.1. Классификация полупроводниковых таймеров

Однотактный таймер (рис. 14.2, а) работает следующим образом. В исходном состоянии, когда переключатель S1 замкнут, напряжение на конденсаторе уменьшается до нуля и на выходе таймера устанавливается низкое напряжение, равное 0,1 В. При подаче импульса на вход триггера в нем формируется сигнал, размыкающий переключатель S1, и на выходе таймера устанавливается высокое напряжение. Если входное сопротивление компаратора А1 значительно больше сопротивления  , конденсатор

, конденсатор  , будет заряжаться только через

, будет заряжаться только через  , а напряжение на

, а напряжение на  , будет экспоненциально нарастать с постоянной времени

, будет экспоненциально нарастать с постоянной времени  , стремясь к своему максимальному значению

, стремясь к своему максимальному значению  . Как только напряжение на конденсаторе достигнет

. Как только напряжение на конденсаторе достигнет

Рисунок 14.2. Структурные схемы однотактного (а) и многотактного (б) таймеров

некоторой величины  , компаратор начнет вырабатывать сигнал, устанавливающий триггер (а следовательно, и весь таймер) в исходное состояние (

, компаратор начнет вырабатывать сигнал, устанавливающий триггер (а следовательно, и весь таймер) в исходное состояние (  ). Временной интервал

). Временной интервал  должен быть значительно больше, чем длительность запускающего импульса. Опорное напряжение

должен быть значительно больше, чем длительность запускающего импульса. Опорное напряжение  формируется в таймере внутренним резисторным делителем.

формируется в таймере внутренним резисторным делителем.

Описанный цикл работы таймера имеет место при включении его по схеме одновибратора, когда формируется один выходной импульс после подачи внешнего сигнала запуска на вход триггера. Для того чтобы таймер мог работать в режиме асинхронного мультивибратора, управляющий выходной сигнал от времязадающей  - цепи подается на RS-триггер через компаратор А2 с опорным напряжением

- цепи подается на RS-триггер через компаратор А2 с опорным напряжением  .

.

Чтобы иметь возможность прервать выполнение таймером заданной функции независимо от завершенности временного цикла, введем переключатель S 2. При подаче сигнала сброса S 2 замыкается, конденсатор полностью разряжается и напряжение на нем остается близким к нулю до тех пор, пока сигнал сброса не будет снят. Обычно при подаче сигнала сброса на выходе таймера устанавливается низкое напряжение.

Многотактные таймеры разработаны для аппаратуры, требующей использования генераторов сигналов сверхнизкой частоты с продолжительностью импульсов до нескольких суток. Семейство этих*, таймеров делится на две основные группы (см. рис. 14.1). К первой группе относятся программируемые таймеры, в которых формируемый временной интервал задается программно, установкой соответствующих перемычек на выходах счетчика. В зависимости от вида соединения выходов счетчика многотактный таймер умножает постоянную времени  - цепи в n раз (n определяет диапазон программирования или коэффициент умножения счетчиков). Программируемые таймеры содержат таймеры общего применения, выполненные по биполярной технологии, и микромощные. Ко второй группе относятся специализированные таймеры со встроенными счетчиками, у которых однозначно задан коэффициент умножения п.

- цепи в n раз (n определяет диапазон программирования или коэффициент умножения счетчиков). Программируемые таймеры содержат таймеры общего применения, выполненные по биполярной технологии, и микромощные. Ко второй группе относятся специализированные таймеры со встроенными счетчиками, у которых однозначно задан коэффициент умножения п.

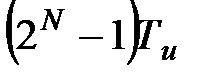

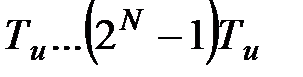

Программируемые таймеры работают следующим образом (рис. 7.2,6). При подаче на вход запуска импульса включается внутренний мультивибратор на однотактном таймере, генерирующий импульсы длительностью  . Подключенный к выходу таймера N - разрядный двоичный счетчик подсчитывает входные импульсы и формирует на N выходах счетчика временные интервалы, длительность которых может устанавливаться от

. Подключенный к выходу таймера N - разрядный двоичный счетчик подсчитывает входные импульсы и формирует на N выходах счетчика временные интервалы, длительность которых может устанавливаться от  до

до  .На первом выходе формируется импульс длительностью

.На первом выходе формируется импульс длительностью  , на втором - длительностью 2

, на втором - длительностью 2  , на N -м - длительностью

, на N -м - длительностью  .Счетчик допускает объединение выходов, причем длительность формируемого в этом случае временного интервала определяется суммой длительности импульсов на объединенных выходах. Например, объединены выходы, формирующие отдельно импульсы длительностью

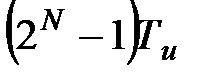

.Счетчик допускает объединение выходов, причем длительность формируемого в этом случае временного интервала определяется суммой длительности импульсов на объединенных выходах. Например, объединены выходы, формирующие отдельно импульсы длительностью  :

:

Рисунок 14.3. Структурные схемы типового (а) и прецизионного (б) однотактных таймеров

8  и 128

и 128  ,тогда длительность формируемого временного интервала

,тогда длительность формируемого временного интервала  . Таким образом, объединив соответствующие выходы, получим любую длительность импульса или задержку его фронта в диапазоне

. Таким образом, объединив соответствующие выходы, получим любую длительность импульса или задержку его фронта в диапазоне  .Выполнение таким таймером предварительно заданной программы можно прервать, подав на специальный вход импульс сброса. Для синхронной работы внутреннего однотактного таймера и счетчика используется управляющая цифровая микросхема.

.Выполнение таким таймером предварительно заданной программы можно прервать, подав на специальный вход импульс сброса. Для синхронной работы внутреннего однотактного таймера и счетчика используется управляющая цифровая микросхема.

В полупроводниковых таймерах наибольшее распространение получили структуры, использованные в однотактных таймерах NE555, LM322 и программируемом XR2240. Структура таймера КР1006ВИ1, аналогичного NE555, показана на рис. 14.3, а. Эти таймеры состоят из четырех функциональных узлов: двух компараторов напряжения на входе, RS-триггера и инвертирующего усилителя мощности на выходе. Внутренний резисторный делитель задает пороговые напряжения, равные  для компаратора А1 и

для компаратора А1 и  для компаратора А2. Длительность генерируемых выходных импульсов устанавливается внешней времязадающей цепью

для компаратора А2. Длительность генерируемых выходных импульсов устанавливается внешней времязадающей цепью  . Аналогичен NE555 по структуре и параметрам таймер XR320, разработанный фирмой EXAR. Этот таймер в отличие от NE555 может управляться не только спадом, но и фронтом импульса. Кроме того, таймер XR320 в дополнение к низкоомному выходу имеет инверсный выходе открытым коллектором. Существенным преимуществом XR320 является то, что времязадающий конденсатор

. Аналогичен NE555 по структуре и параметрам таймер XR320, разработанный фирмой EXAR. Этот таймер в отличие от NE555 может управляться не только спадом, но и фронтом импульса. Кроме того, таймер XR320 в дополнение к низкоомному выходу имеет инверсный выходе открытым коллектором. Существенным преимуществом XR320 является то, что времязадающий конденсатор  заряжается внутренним генератором постоянного тока, величину которого определяет внешний резистор

заряжается внутренним генератором постоянного тока, величину которого определяет внешний резистор  . Благодаря этому напряжение на

. Благодаря этому напряжение на  увеличивается линейно, что важно для некоторых применений однотактных таймеров. Тем не менее этот таймер используется сравнительно редко, не имеет такого схемотехнического обеспечения, как NE555, и обладает незначительными преимуществами по сравнению с последним.

увеличивается линейно, что важно для некоторых применений однотактных таймеров. Тем не менее этот таймер используется сравнительно редко, не имеет такого схемотехнического обеспечения, как NE555, и обладает незначительными преимуществами по сравнению с последним.

Наиболее удачной структурой таймера является использованная в LM322 (рис. 14.3, б). Этот таймер, второй по массовости применения среди однотактных, существенно превосходит NE555 по сочетанию параметров точности, быстродействия и потребления Таймер LM322 часто относят к прецизионным, подразумевая под этим не столько его высокие точностные характеристики, сколько специфичность применения в аппаратуре. Таймер содержит источник опорного напряжения 3,15 В, в которому подключается внешний времязадающий резистор. Применен только один компаратор, быстродействие которого можно увеличить, подключив дополнительный вывод N к источнику питания  . Запускается таймер положительным фронтом импульса. Таймер LM322 существенно отличается от NE555 конструкцией выходного каскада. Хотя использованное в схеме включение транзистора VT 2 и делает более универсальным выход таймера, для большинства применений предпочтительнее мощный выходной каскад как в NE555.

. Запускается таймер положительным фронтом импульса. Таймер LM322 существенно отличается от NE555 конструкцией выходного каскада. Хотя использованное в схеме включение транзистора VT 2 и делает более универсальным выход таймера, для большинства применений предпочтительнее мощный выходной каскад как в NE555.

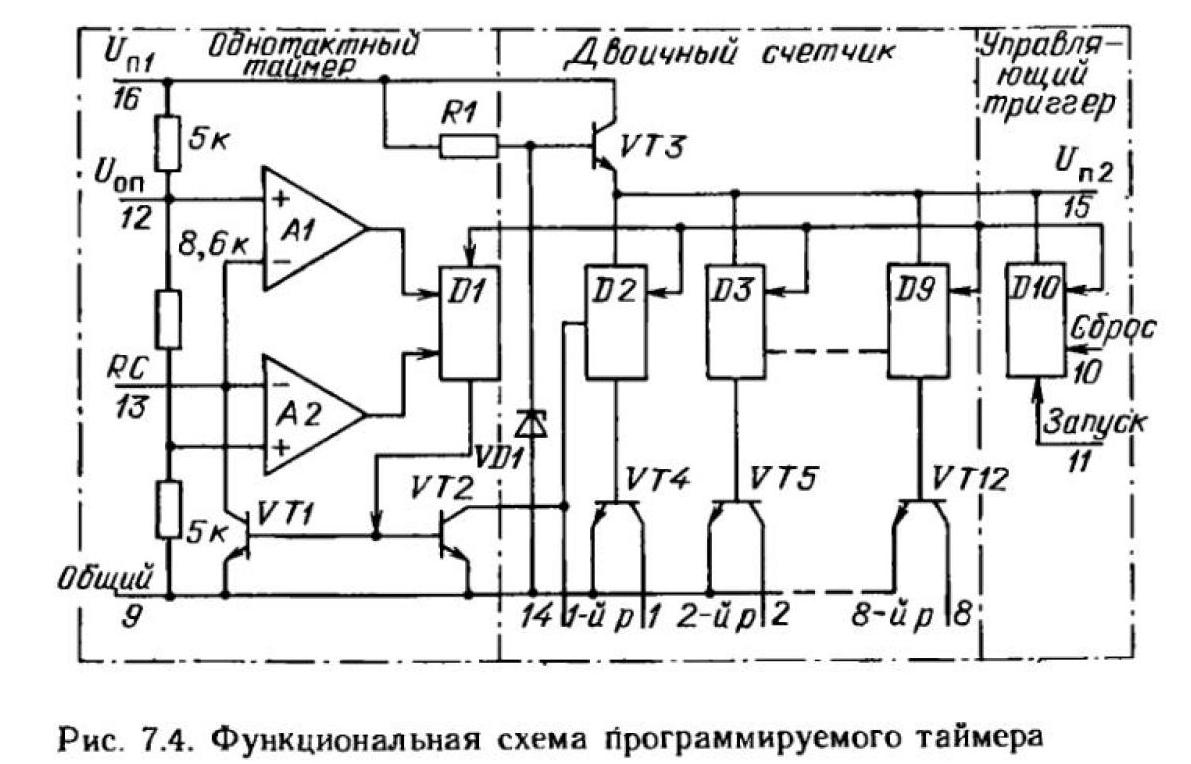

Наиболее распространенным в современной микроэлектронной аппаратуре среди многотактных программируемых таймеров является XR2240, полная функциональная схема которого приведена на рис. 14.4.

Рисунок 14.4. Функциональная схема программируемого таймера

Таймер состоит из трех основных узлов, выделенных штрихпунктирными линиями: однотактного таймера, подобного NE555; 8-разрядного двоичного счетчика и управляющего триггера. Двоичный счетчик и управляющий триггер питаются от внутреннего источника стабилизированного напряжения 6,3 В, образованного цепью VD 1 RIVT 3. Внутренний резисторный делитель устанавливает на входах компараторов А1 и А2 пороговые напряжения переключения, равные  и

и  соответственно. Выходами двоичного счетчика являются открытые коллекторы транзисторов VT 4-VT 12'. Триггер D 10 управляет работой счетчика D 2 — D 9 и триггера DI в однотактном таймере, который, в свою очередь, управляет работой первого каскада D 2 счетчика.

соответственно. Выходами двоичного счетчика являются открытые коллекторы транзисторов VT 4-VT 12'. Триггер D 10 управляет работой счетчика D 2 — D 9 и триггера DI в однотактном таймере, который, в свою очередь, управляет работой первого каскада D 2 счетчика.

14.2. Особенности применения таймеров

Для полного и правильного использования различных возможностей таймера КР1006ВИ1 необходимо знать назначение его выводов, характеристики и требования к выбору параметров времязадающих элементов. Назначение выводов таймера КР1006ВИ1 (см. рис. 14.3, а) незначительно отличается от рассмотренного ранее для обобщенной структуры на рис. 14.2, а. Напряжение питания  подаваемое на вывод 8 и измеряемое относительно вывода 1, равно 5 ... 16,5 В. Приращение потребляемого таймера тока на I В изменения

подаваемое на вывод 8 и измеряемое относительно вывода 1, равно 5 ... 16,5 В. Приращение потребляемого таймера тока на I В изменения  равно 0,7 мА. Таймер способен отдать в нагрузку или принять из нее ток не более 200 мА, что позволяет управлять непосредственно лампочками и даже электромагнитными реле. Выходное сопротивление около 10 Ом как для низкого (

равно 0,7 мА. Таймер способен отдать в нагрузку или принять из нее ток не более 200 мА, что позволяет управлять непосредственно лампочками и даже электромагнитными реле. Выходное сопротивление около 10 Ом как для низкого (  В), так и для высокого (

В), так и для высокого (  В) уровней выходного напряжения. Запуск таймера осуществляется подачей на вывод 2 напряжения менее

В) уровней выходного напряжения. Запуск таймера осуществляется подачей на вывод 2 напряжения менее  (эту цепь обычно называют триггерным входом). По отношению к выходу этот вход является инвертирующим. При высоком напряжении на выводе 2 состоянием выхода таймера можно управлять с помощью компаратора А1 по выводу 6, называемому обычно пороговым входом (см. рис. 7.3, а). Относительно изменений выходного напряжения этот вывод является не инвертирующим входом таймера.

(эту цепь обычно называют триггерным входом). По отношению к выходу этот вход является инвертирующим. При высоком напряжении на выводе 2 состоянием выхода таймера можно управлять с помощью компаратора А1 по выводу 6, называемому обычно пороговым входом (см. рис. 7.3, а). Относительно изменений выходного напряжения этот вывод является не инвертирующим входом таймера.

Входной ток, втекающий для компаратора А1 (вывод 6) и вытекающий для компаратора А2 (вывод 2), не превышает 0,5 мкА. Для сброса таймера, т. е. установления на его выходе низкого напряжения независимо от напряжения на выводах 2 и 6, используется вывод 4. Если напряжение на этом выводе  В, напряжение на выходе равно 0,1 ... 0,2 В. При напряжении

В, напряжение на выходе равно 0,1 ... 0,2 В. При напряжении  B цепь сброса выключена и не влияет на работу таймера. Кроме низкоомного выхода (вывод 3) таймер имеет и вспомогательный высокоомный выход (вывод 7), представляющий собой открытый коллектор транзистора VT 1 (см. рис. 7.3, а). Этот вывод обычно используется для организации обратной связи с выхода на входы (выводы 2 и 6) таймера. Допустимое изменение напряжения на выводах 2, 4, 6 и 7 лежит в пределах 0 ... 16,5 В. В таймере имеется доступ через вывод 5 к входам внутренних компараторов, на которые поданы пороговые напряжения. Этот вывод от резисторного делителя позволяет дополнительно управлять работой таймера, изменяя пороговые напряжения компараторов при постоянном напряжении питания. Чтобы избежать влияния внешних помех и пульсаций напряжения питания на точность работы таймера, рекомендуется шунтировать вывод 5 конденсатором емкостью около 0,01 мкФ.

B цепь сброса выключена и не влияет на работу таймера. Кроме низкоомного выхода (вывод 3) таймер имеет и вспомогательный высокоомный выход (вывод 7), представляющий собой открытый коллектор транзистора VT 1 (см. рис. 7.3, а). Этот вывод обычно используется для организации обратной связи с выхода на входы (выводы 2 и 6) таймера. Допустимое изменение напряжения на выводах 2, 4, 6 и 7 лежит в пределах 0 ... 16,5 В. В таймере имеется доступ через вывод 5 к входам внутренних компараторов, на которые поданы пороговые напряжения. Этот вывод от резисторного делителя позволяет дополнительно управлять работой таймера, изменяя пороговые напряжения компараторов при постоянном напряжении питания. Чтобы избежать влияния внешних помех и пульсаций напряжения питания на точность работы таймера, рекомендуется шунтировать вывод 5 конденсатором емкостью около 0,01 мкФ.

В режиме прямой трансляции сигнала со входа на выход таймер может работать в диапазоне частоты до 10 МГц. Однако приводимое в справочных данных значение погрешности формирования временного интервала, равное 0,5%, измеряется обычно при формировании импульсов длительностью более 10 мкс. Время нарастания выходного напряжения таймера не превышает 100 не.

Временные параметры этого однотактного таймера слабо зависят от изменений Un и температуры и полностью определяются схемотехникой внутренних компараторов и качеством бинолярной технологии их изготовления. В таймерах, изготовленных по КМОП технологии, отличающейся худшим согласованием параметров парных транзисторов, зависимость характеристик от  и температуры значительно выше, чем у таймеров, изготовленных по биполярной технологии-

и температуры значительно выше, чем у таймеров, изготовленных по биполярной технологии-

Особенности применения таймера КР1006ВИ1 связаны с не идеальностью его параметров и схемотехникой узлов. Чтобы параметры времязадающей цепи  не влияли на точность формирования временных интервалов, необходимо ограничить диапазон изменения сопротивления

не влияли на точность формирования временных интервалов, необходимо ограничить диапазон изменения сопротивления  и емкости

и емкости  . Максимальное сопротивление

. Максимальное сопротивление  определяется входным током

определяется входным током  компараторов, протекающим по выводам 2 и 6. Для формирования устойчивых временных интервалов достаточно выбрать максимальное сопротивление

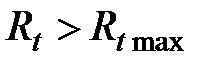

компараторов, протекающим по выводам 2 и 6. Для формирования устойчивых временных интервалов достаточно выбрать максимальное сопротивление  из условия

из условия  20 МОм при

20 МОм при  = 10 В и

= 10 В и  0,5 мкА. При включении таймера по схеме мультивибратора, когда выводы 2 и 6 объединены, входные токи (втекающий по выводу 6 и вытекающий по выводу 2) частично взаимокомпенсируются и таймер может сохранить работоспособность при

0,5 мкА. При включении таймера по схеме мультивибратора, когда выводы 2 и 6 объединены, входные токи (втекающий по выводу 6 и вытекающий по выводу 2) частично взаимокомпенсируются и таймер может сохранить работоспособность при  . При включении таймера по схеме одновибратора для

. При включении таймера по схеме одновибратора для  20 МОм отдельные типы таймеров не будут выполнять требуемую функцию. Поэтому не рекомендуется использовать времязадающие резисторы сопротивлением

20 МОм отдельные типы таймеров не будут выполнять требуемую функцию. Поэтому не рекомендуется использовать времязадающие резисторы сопротивлением  > 10 МОм.

> 10 МОм.

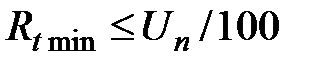

Минимальное сопротивление  определяется максимально допустимым током, протекающим через внутренний транзистор VT1 таймера при его насыщении. Хотя допустимый выходной ток по выводу 7 устанавливают обычно на уровне 100 мА, не рекомендуется использовать малые сопротивления

определяется максимально допустимым током, протекающим через внутренний транзистор VT1 таймера при его насыщении. Хотя допустимый выходной ток по выводу 7 устанавливают обычно на уровне 100 мА, не рекомендуется использовать малые сопротивления  в сочетании с большими емкостями

в сочетании с большими емкостями  . Объясняется это тем, что при разряде конденсаторов

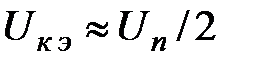

. Объясняется это тем, что при разряде конденсаторов  большой емкости транзистор VT1 не мгновенно переходит в режим насыщения, а через время

большой емкости транзистор VT1 не мгновенно переходит в режим насыщения, а через время  . В течение этого времени транзистор работает в активном режиме при напряжении коллектор-эмиттер

. В течение этого времени транзистор работает в активном режиме при напряжении коллектор-эмиттер  и, если

и, если  мА, транзистор VT1 может выйти из строя из-за чрезмерной рассеиваемой на нем мощности. Поэтому при формировании малых временных интервалов рекомендуется ограничиться значением

мА, транзистор VT1 может выйти из строя из-за чрезмерной рассеиваемой на нем мощности. Поэтому при формировании малых временных интервалов рекомендуется ограничиться значением  =1 кОм и выбрать исходя из этого емкость

=1 кОм и выбрать исходя из этого емкость  . Если же таймер применяется в схеме, где

. Если же таймер применяется в схеме, где  100 пФ, то сопротивление

100 пФ, то сопротивление  может быть уменьшено до 150 Ом, что для аппаратуры специального назначения должно подтверждаться соответствующими техническими условиями.

может быть уменьшено до 150 Ом, что для аппаратуры специального назначения должно подтверждаться соответствующими техническими условиями.

Минимальная емкость времязадающего конденсатора  , должна быть значительно больше изменений собственной входной емкости таймера на выводе 2, 6 и 7 в зависимости от напряжения на них. Поскольку изменение входной емкости при перезарядке

, должна быть значительно больше изменений собственной входной емкости таймера на выводе 2, 6 и 7 в зависимости от напряжения на них. Поскольку изменение входной емкости при перезарядке  не превышает нескольких пикофарад, не рекомендуется при формировании точных временных интервалов использовать

не превышает нескольких пикофарад, не рекомендуется при формировании точных временных интервалов использовать  пФ. Можно применять конденсаторы

пФ. Можно применять конденсаторы  сколь угодно большой емкости, если их ток утечки пренебрежимо мал. Фактически же чем больше емкость конденсатора, тем больше его ток утечки. Для нормальной работы таймера необходимо, чтобы ток утечки

сколь угодно большой емкости, если их ток утечки пренебрежимо мал. Фактически же чем больше емкость конденсатора, тем больше его ток утечки. Для нормальной работы таймера необходимо, чтобы ток утечки  не превышал зарядный ток через

не превышал зарядный ток через  . Для формирования точных (

. Для формирования точных (  ) временных интервалов ток утечки через

) временных интервалов ток утечки через  дол жен быть более чем на два порядка меньше зарядного тока.

дол жен быть более чем на два порядка меньше зарядного тока.

Выходной инвертирующий усилитель таймера (см. рис. 7.3, а) работает в режиме АБ, вследствие чего на переходной характеристике возникает «полка» длительностью 10...20 не при напряжении 1,5 В. Если таймер нагружен на быстродействующие ТТЛ схемы (например, серий 130 или 533), то наличие такой «полки» недопустимо, так как она находится в их пороговой области и может вызвать ложное срабатывание логического элемента. Чтобы выровнять линию переходного процесса, необходимо выход таймера за шунтировать конденсатором емкостью около 100 пФ.

Программируемые таймеры со встроенными счетчиками обеспечивают такую же точность формирования временных интервалов, как и однотактные. Однако диапазон, в котором достигается эта точность, значительно расширен (от единиц микросекунд до нескольких суток).

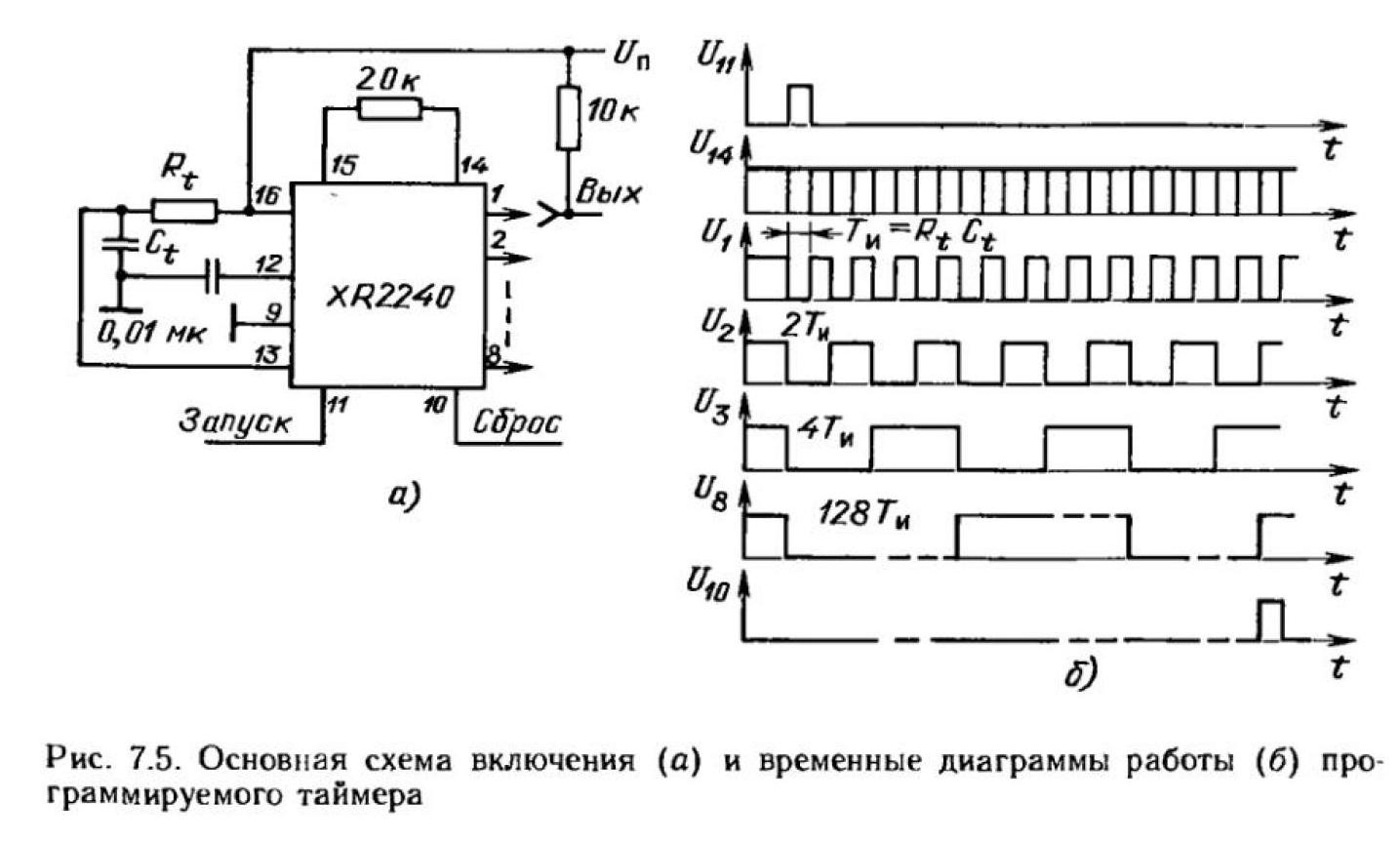

Назначение выводов программируемого таймера следует из его функциональной схемы (см. рис. 14.4). Основное напряжение питания, подаваемое на вывод 16 и измеряемое относительно вывода 9 равно 4... 15 В. Приращение потребляемого таймером тока на I В увеличения напряжения  равно 1 мА. При напряжении питания 4,5 внутренний источник стабилизированного напряжения

равно 1 мА. При напряжении питания 4,5 внутренний источник стабилизированного напряжения  перестает работать, поэтому выводы 15 и 16 следует объединить, чтобы обеспечить нормальную работу счетчика. Максимальный ток, который выходы счетчика (выводы 1 - 8) могут принимать от нагрузки, не должен превышать 5 мА. Допустимое изменение напряжения на выводах 1 - 8 лежит в пределах 0...15. В Запуск таймера осуществляется положительным фронтом импульса, подаваемого на вывод 11 управляющего триггера (рис. 14.5, а). В момент запуска напряжения на выводах 1- 8 начинают изменяться в соответствии с временной диаграммой (рис. 14.5, б). Соединением выводов 1-8 обеспечивается выполнение на выходе логической функции Проводное ИЛИ. Таймер не воспринимает следующий импульс запуска, поступивший в течение формирования установленного заранее временного интервала. Сброс таймера осуществляется положительным фронтом импульса, подаваемого на вывод 10. В момент подачи импульса сброса транзисторы VT4 - VT12 (см. рис. 14.4) закрываются. Для управления таймером по выводам 10, 11 необходимы импульсы с логическими уровнями, соответствующими ТТЛ схемам, и с длительностью более 1,5 мкс.

перестает работать, поэтому выводы 15 и 16 следует объединить, чтобы обеспечить нормальную работу счетчика. Максимальный ток, который выходы счетчика (выводы 1 - 8) могут принимать от нагрузки, не должен превышать 5 мА. Допустимое изменение напряжения на выводах 1 - 8 лежит в пределах 0...15. В Запуск таймера осуществляется положительным фронтом импульса, подаваемого на вывод 11 управляющего триггера (рис. 14.5, а). В момент запуска напряжения на выводах 1- 8 начинают изменяться в соответствии с временной диаграммой (рис. 14.5, б). Соединением выводов 1-8 обеспечивается выполнение на выходе логической функции Проводное ИЛИ. Таймер не воспринимает следующий импульс запуска, поступивший в течение формирования установленного заранее временного интервала. Сброс таймера осуществляется положительным фронтом импульса, подаваемого на вывод 10. В момент подачи импульса сброса транзисторы VT4 - VT12 (см. рис. 14.4) закрываются. Для управления таймером по выводам 10, 11 необходимы импульсы с логическими уровнями, соответствующими ТТЛ схемам, и с длительностью более 1,5 мкс.

Рисунок 14.5. Основная схема включения (а) и временные диаграммы работы (б) программируемого таймера

Выход внутреннего однотактного таймера (вывод 14) необходимо подключать через резистор сопротивлением более 20 кОм к шине стабилизированного внутреннего источника напряжения питания. Вывод 14 можно использовать и в качестве автономного входа счетчика, работающего от внешних импульсов. Для этого необходимо закрыть транзистор VT2, заземлив, например, вывод 13 через резистор сопротивлением 1 кОм. В этом случае счетчик срабатывает по срезу положительных импульсов, подаваемых на вывод 14. Этот вывод может использоваться и в качестве дополнительной цепи управления работой счетчика. Счет прекращается независимо от состояний транзистора VT2, если вывод 14 заземлить. Для управления по выводу 14 необходимы ТТЛ уровни напряжений.

Внутренний однотактный таймер генерирует импульсы длительностью около 0,35 мкс с частотой, равной  . Времязадающая цепь включается между выводами 9 и 16, а ее средняя точка соединяется с выводом 13. Максимальная частота генерируемых импульсов равна 130 кГц (при

. Времязадающая цепь включается между выводами 9 и 16, а ее средняя точка соединяется с выводом 13. Максимальная частота генерируемых импульсов равна 130 кГц (при  =1 кОм,

=1 кОм,  = 0,007 мкФ). Не рекомендуется устанавливать частоту меньше

= 0,007 мкФ). Не рекомендуется устанавливать частоту меньше  Гц. (

Гц. (  = 10 МОм,

= 10 МОм,  мкФ). В то же время счетчик может работать от внешних сигналов с частотой до 1,5 МГц.

мкФ). В то же время счетчик может работать от внешних сигналов с частотой до 1,5 МГц.

Как и в однотактном таймере, в программируемом имеется вывод от внутреннего резисторного делителя. Это позволяет управлять работой счетчика с помощью аналогового сигнала, подаваемого на вывод 12.

Таймер спроектирован таким образом, что в момент включения его напряжения питания  производится автоматический самосброс счетчика, если на выводах 10 и 11 напряжения около 0 В. Цепи сброса и запуска не равносильны при управлении триггером D10. Если одновременно поданы положительные импульсы на выводы 10 и 11, то управляющий триггер D10 отреагирует только на импульс запуска.

производится автоматический самосброс счетчика, если на выводах 10 и 11 напряжения около 0 В. Цепи сброса и запуска не равносильны при управлении триггером D10. Если одновременно поданы положительные импульсы на выводы 10 и 11, то управляющий триггер D10 отреагирует только на импульс запуска.

При разомкнутой цепи ОС с выходов счетчика на вывод 10 таймер работает в режиме мультивибратора, генерирующего непрерывные последовательности выходных импульсов после подачи на вывод 11 положительного импульса. Если цепь ОС замкнута, то после подачи положительного импульса на вывод 11 таймер генерирует последовательности выходных импульсов до прихода первого положительного импульса на вывод 10.

Дата: 2019-02-19, просмотров: 950.