По мере развития цифровых микросхем возникло противоречие между возможной степенью интеграции и номенклатурой выпускаемых микросхем. Экономически оправдано было выпускать микросхемы средней интеграции, таких как регистры, счетчики, сумматоры. Более сложные схемы приходилось создавать из этих узлов. Разместить более сложную схему на полупроводниковом кристалле не было проблем, но это было оправдано либо очень большой серийностью аппаратуры, либо ценой аппаратуры (военная, авиационная или космическая). Заказные микросхемы не могли удовлетворить возникшую потребность в миниатюризации аппаратуры. Решение могло быть только одним — предоставить разработчикам аппаратуры возможность изменять внутреннюю структуру микросхемы (программировать).

История развития программируемых логических интегральных схем (ПЛИС) начинается с появления программируемых постоянных запоминающих устройств. Первое время программируемые ПЗУ использовались исключительно для хранения данных, однако вскоре их стали применять для реализации цифровых комбинаторных устройств с произвольной таблицей истинности. В качестве недостатка подобного решения следует отметить экспоненциальный рост сложности устройства в зависимости от количества входов. Добавление одного дополнительного входа цифрового устройства приводит к удвоению требуемого количества ячеек памяти ПЗУ. Это не позволяет реализовать многовходовые комбинационные цифровые схемы.

Для реализации цифровых комбинационных устройств с большим числом входов были разработаны программируемые логические матрицы (ПЛМ). В иностранной литературе они получили название — Programmable Logic Arrays (PLA). Именно программируемые логические матрицы можно считать первыми программируемыми логическими интегральными схемами (Programmable Logic Devices — PLDs). ПЛМ получили широкое распространение в качестве первых универсальных микросхем большой интеграции.

Классификация ПЛИС

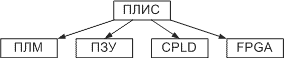

В настоящее время программируемые логические интегральные схемы развиваются по нескольким направлениям, поэтому возникла необходимость как то различать эти микросхемы. Классификация программируемых логических интегральных схем (ПЛИС) приведена на рисунке 2.1.

Рисунок 2.1. Классификация программируемых логических интегральных схем (ПЛИС)

Следует отметить, что программируемые логические матрицы (ПЛМ) реализуют хорошо известные принципы создания цифровой комбинационной схемы по таблице истинности (СДНФ). Применение постоянных запоминающих устройств (ПЗУ) в качестве комбинационной схемы позволяет вообще обойтись без составления комбинационной функции и ее минимизации. Области применения этих микросхем сразу определились. ПЗУ применялись для создания комбинационных схем с малым количеством входов. При росте количества входов сложность внутреннего устройства ПЗУ и его цена резко возрастали (по квадратичному закону). ПЛМ позволяли реализовывать таблицы истинности с относительно малым количеством единичных сигналов на выходе и большим количеством входных сигналов, либо хорошо минимизирующиеся логические функции.

Первоначально цифровые устройства с памятью реализовывали либо на нескольких ПЛМ, либо добавляли внешние триггеры , затем стали включать их в состав программируемых логических устройств. По мере увеличения степени интеграции микросхем возникла необходимость объединять полученные сложные микросхемы на одном кристалле. В результате возникли сложные программируемые логические устройства (CPLD). В них появилась возможность программировать не только таблицу истинности комбинационного устройства, но и линии соединения входов и выходов ПЛД между собой. Таким образом можно считать CPLD дальнейшим развитием ПЛМ и ПЛД.

Точно так же развивались цифровые устройства на ПЗУ. Сначала к их выходам добавили триггер. Естественно предоставили возможность отключать его при необходимости. Затем несколько этих схем разместили на одном кристалле и предоставили возможность программировать соединения их входов и выходов между собой. Подобные устройства называются FPGA.

Дата: 2019-02-25, просмотров: 369.