Сумматоры представляют собой функциональные цифровые устройства, выполняющие операцию сложения чисел. В цифровой технике суммирование осуществляется в двоичном или, реже, в двоично-десятичном коде.

По характеру действия сумматоры подразделяются на комбинационные и накопительные; п о количеству одновременно обрабатываемых разрядов складываемых чисел сумматоры делятся на одноразрядные и многоразрядные.

По числу входов и выходов одноразрядные двоичные сумматоры подразделяются на:

– четвертьсумматоры (элементы "сумма по модулю 2"; элементы "исключающее ИЛИ"), характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма;

– полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноименные разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом – перенос в следующий (более старший разряд);

– полные одноразрядные двоичные сумматоры, характеризующиеся наличием трех входов, на которые подаются одноименные разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма в данном разряде, а на другом – перенос в следующий (более старший разряд).

По способу представления и обработки складываемых чисел многоразрядные двоичные сумматоры подразделяются на:

– последовательные, в которых обработка разрядов чисел ведется поочередно, разряд за разрядом на одном и том же оборудовании;

– параллельные, в которых слагаемые складываются одновременно по всем разрядам и для каждого разряда имеется свое оборудование.

Сумматор имеет n входов разрядов слагаемого A, n входов разрядов слагаемого В и вход переноса cr (carry – перенос). Выходами сумматора являются n выходов разрядов суммы S и выход переноса (переполнения) CR. Сумматор характеризуется четырьмя значениями задержки распространения:

TcrS – от подачи входного переноса до установления всех выходов суммы при постоянном уровне на всех входах слагаемых (А и В);

TAS – от одновременной подачи всех слагаемых до установления всех выходов суммы при постоянном уровне на входе переноса (выходной перенос CR не учитывается);

TcrCR – от подачи входного переноса до установления выходного переноса CR при постоянном уровне на входах слагаемых;

Tacr – от подачи всех слагаемых до установления выходного переноса CR при постоянном уровне на входах слагаемых.

Как последовательные, так и параллельные многоразрядные сумматоры строятся на основе одноразрядных суммирующих схем.

Четвертьсумматор

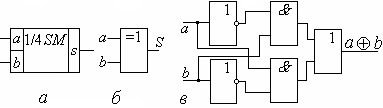

Простейшим двоичным суммирующим элементом является четвертьсумматор. Происхождение названия этого элемента следует из того, что он имеет в два раза меньше выходов и в два раза меньше строк в таблице истинности по сравнению с полным двоичным одноразрядным сумматором. Наиболее известны для данной схемы названия: элемент "сумма по модулю 2" и элемент "исключающее ИЛИ". Схема (рис. 11.1) имеет два входа а и b для двух слагаемых и один выход S для суммы. Работу ее отражает таблица истинности (табл. 11.1), а соответствующее уравнение имеет вид:

|

| a | b | S |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Таблица 11.1

Таблица 11.1

Рис. 11.1 Условное обозначение (а, б) и схема реализации четвертьсумматора (в)

На рис. 11.1 представлены условное графическое обозначение элемента и схема реализации в базисе И-ИЛИ-НЕ. Состояния четвертьсумматора при различных значениях входных сигналов представлены в таблице истинности (табл. 11.1). Здесь старшая единица, возникающая при суммировании двух единиц, не учитывается.

Дата: 2019-02-25, просмотров: 599.