Узлы и устройства ЭВМ

Иерархия уровней элементов. Характеристики ИС. Виды цифровых устройств.

Элементы (в широком смысле) – наименьшие функциональные части, на которые разбивают цифровое устройство при логическом проектировании и технической реализации.

Иерархия уровней элементов:

1. Электронные компоненты (простейшие элементы) (элементы в узком смысле): резисторы, конденсаторы, диоды, транзисторы.

2. Логические и запоминающие элементы: коньюнкторы, дизьюнкторы, элементы Шеффера, элементы Пирса и др., различные виды триггеров.

3. Функциональные узлы или субсистемы: регистры, счетчики, дешифраторы, мультиплексоры и сумматоры.

4. Функциональные устройства: АЛУ, запоминающие устройства и др.

5. Вычислительная машина в целом: микроконтроллеры.

Каждый из уровней элементов выпускается в виде интегральных микросхем (ИС).

Каждый предшествующий уровень является основой для следующего.

Разновидности интегральных микросхем.

Существует 4 типа интегральных схем:

1. Полупроводниковые ИС.

2. Гибридные ИС.

3. Совмещенные ИС.

4. Микросхемы функциональной электроники.

Полупроводниковые интегральные схемы.

Изготавливаются на основе активной, обычно кремниевой, подложке. Все элементы изготавливаются на поверхности или в объеме подложки в одном технологическом процессе.

Технологические линии по производству получаются дорогие, а сами микросхемы дешевые.

Гибридные интегральные схемы.

Изготавливаются на пассивной подложке (стекло, керамика), на которую методом пленочной технологии напыляют пассивные элементы. Активные элементы (бескорпусные транзисторы и диоды) являются навесными.

Оборудование для производства проще и дешевле, чем в полупроводниковых ИС, микросхемы же получаются дорогими.

Совмещенные интегральные схемы.

Активные элементы изготавливаются в объеме активной подложки (например, кремний), пассивные же элементы напыляются на поверхность методом пленочной технологии.

Оборудование дорогое (занимает промежуточное положение между 1 и 2), микросхемы тоже не и дешевые (между 1 и 2). По этой технологии могут изготавливать полузаказные БИС.

Комбинационные узлы (КУ).

Последовательностные узлы (ПУ) или автоматы.

Комбинационные узлы математически описываются с помощью переключательных функций и их выходные значения не зависят от времени поступления входного, и однозначно входным определяются.

Последовательностные узлы описываются графами, и их поведение рассматривается в курсе теории автоматов. Они вырабатывают последовательность выходных сигналов, учитывая предысторию, а значит, содержат элементы памяти.

Линейный дешифратор.

В линейном дешифраторе непосредственно реализуется система переключательных функций, с помощью которой описывается его функционирование.

Пример: 2 в 4 (2 входа и 4 выхода)

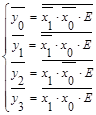

Реализуем дешифратор с инверсными выходами:

Два инвертора подряд установлены по той же причине, что и у мультиплексора.

Особенности схемы:

1) Линейный дешифратор имеет максимальное быстродействие

2) С увеличением количества выходов:

· Увеличивается число входов у элементов «И-НЕ»

· Возрастает нагрузка на вход инвертора

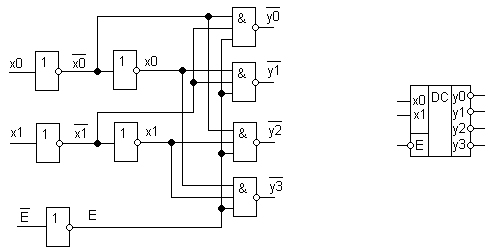

Дешифратор 1 в 2 имеет следующий вид:

Мультиплексор (КУ).

Мультиплексор – это коммутирующий элемент, подключающий к своему единственному выходу в зависимости от управляющих сигналов один из информационных входов. Мультиплексор является комбинационным узлом.

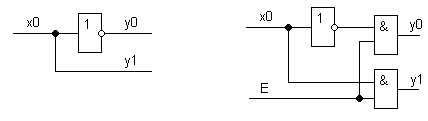

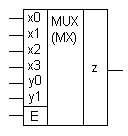

Схематическое представление:

Условное графическое обозначение:

Х – информационные входы.

Y – управляющие входы.

Е – вход разрешения работы.

Если Е=0, то z=0.

Мультиплексор используется для подключения к какому-либо устройству поочередно выходы некоторых устройств.

Для мультиплексора справедливо выражение m=2l (где l – число управляющих входов, m – число информационных входов).

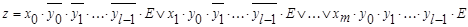

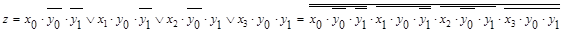

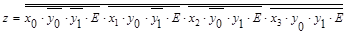

Дизъюнктивная нормальная форма:

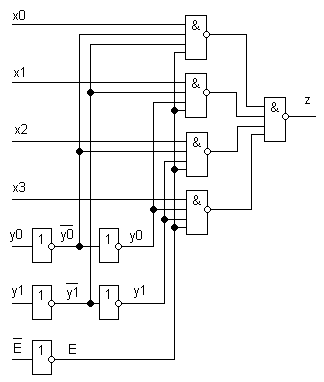

Построим четырех входной мультиплексор:

Добавив вход Е, получим:

Два инвертора по входам yi установлены с целью обеспечения по этим входам нагрузки равной одному входу элемента.

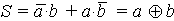

Четвертьсумматор

Простейшим двоичным суммирующим элементом является четвертьсумматор. Происхождение названия этого элемента следует из того, что он имеет в два раза меньше выходов и в два раза меньше строк в таблице истинности по сравнению с полным двоичным одноразрядным сумматором. Наиболее известны для данной схемы названия: элемент "сумма по модулю 2" и элемент "исключающее ИЛИ". Схема (рис. 11.1) имеет два входа а и b для двух слагаемых и один выход S для суммы. Работу ее отражает таблица истинности (табл. 11.1), а соответствующее уравнение имеет вид:

|

| a | b | S |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Таблица 11.1

Таблица 11.1

Рис. 11.1 Условное обозначение (а, б) и схема реализации четвертьсумматора (в)

На рис. 11.1 представлены условное графическое обозначение элемента и схема реализации в базисе И-ИЛИ-НЕ. Состояния четвертьсумматора при различных значениях входных сигналов представлены в таблице истинности (табл. 11.1). Здесь старшая единица, возникающая при суммировании двух единиц, не учитывается.

Управляющие сигналы

Выполняемые операции

^ B

^ B

) + C0

) + C0

) + C0

) + C0

) + C0

) + C0

+ C0

+ C0

) + C0

) + C0

v B

v B

) + (A ^ B) + C0

) + (A ^ B) + C0

) + A + C0

) + A + C0

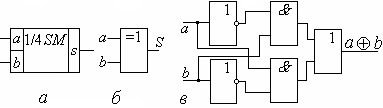

Классификация триггеров.

По логическому функционированию триггеры делят на:

1) RS (Reset, Set)

2) JK (Jump, Kill)

3) D (Delay)

4) T (Toggle)

5) DV, TV (Valve)

6) Прочие: R, S, E и другие (разновидности RS триггера)

По способу записи информации триггеры делятся на:

|

В синхронных триггерах запись информации происходит только по синхросигналу. Если новое значение на выходе триггера появляется после снятия входного сигнала, который вызвал появление этого нового значения, то триггер называется триггер с разделением процессов записи и считывания или с внутренней задержкой. Для асинхронного триггера это рассматривается относительно логических сигналов, а синхронного – относительно синхроимпульса. Если синхронный однотактный триггер с внутренней задержкой реагирует только на фронт синхросигнала, то он является динамическим.

Поведение триггеров может быть описано с помощью характеристического уравнения триггера:

где x – логические сигналы, C – синхросигнал, Q – состояние триггера.

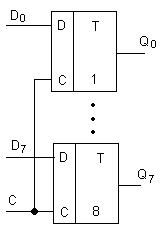

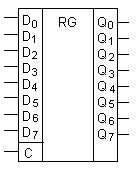

Регистр – защелка.

Условное графическое обозначение:

Данный регистр имеет максимальное быстродействие из всех известных регистров. Регистр не имеет внутренней задержки, а, следовательно, в схемах с обратной связью (автоматах) его использовать нельзя.

Классификация счетчиков.

1) По направлению счета:

· Суммирующие (прямого счета).

· Вычитающие (обратного счета).

· Реверсивные (с изменением направления счета).

2) По организации процесса получения результата:

· С последовательным переносом.

· С параллельным переносом.

· Со сквозным переносом.

· С комбинированным переносом.

3) По использованной системе счисления:

· Двоичные.

· Не двоичные.

4) По наличию дополнительного синхросигнала:

· Асинхронные.

· Синхронные.

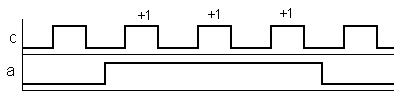

асинхронный: N+1

синхронный: N+3

Счетчики характеризуются модулем счета М – число импульсов на входе счетчика до его переполнения, равное числу внутренних состояний счетчика.

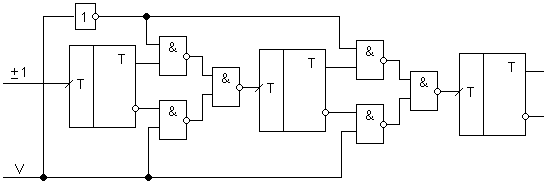

Реверсивные счетчики.

Существуют два способа построения реверсивных счетчиков:

· Основанный на изменении межразрядных связей.

· Основанный на обращении кодов.

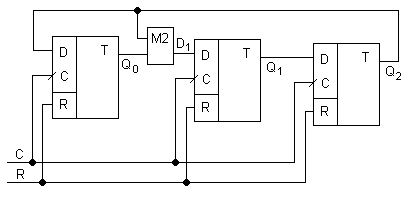

Построение реверсивного счетчика способом изменения межразрядных связей.

При V=1 верхние конъюнкторы заблокированы. Сигнал с инверсного выхода триггера  через два инвертора «И-НЕ» поступает на вход Т, получаем схему суммирующего счетчика с последовательным переносом. При V=0 блокируются нижние конъюнкторы и прямой выход триггера через два инвертора «И-НЕ» поступает на вход Т, получаем схему вычитающего счетчика с последовательным переносом.

через два инвертора «И-НЕ» поступает на вход Т, получаем схему суммирующего счетчика с последовательным переносом. При V=0 блокируются нижние конъюнкторы и прямой выход триггера через два инвертора «И-НЕ» поступает на вход Т, получаем схему вычитающего счетчика с последовательным переносом.

Построение реверсивного счетчика способом обращения кода.

Прямые значения Инверсные значения

с триггеров с триггеров

Если прямые значения выходов разрядов увеличивается на 1, то их инверсии уменьшаются на 1, следовательно, при выдаче прямого значения разрядов получаем суммирование, а при выдаче инверсного – вычитание. Однако, если в момент смены направления счета, вместо прямого значения выдать инверсное, или наоборот, то момент смены приведет к изменения значения на выходе. Чтобы этого не произошло надо произвести двойную инверсию: 1 – инвертировать содержимое счетчика и 2 – выдать инверсное значение.

Данный способ удобен лишь в том случае, если в счетчике имеются обе микрооперации.

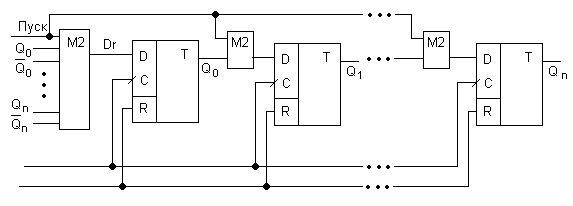

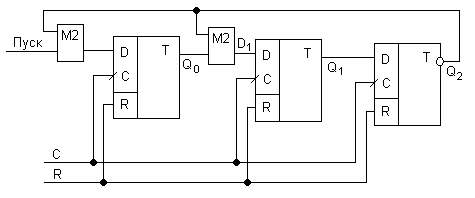

Полиноминальные счетчики.

Полиноминальными счетчиками называют пересчетные схемы, получаемые на основе сдвигающих регистров, в которые заведены обратные связи через сумматоры по модулю 2. Часто используют для получения псевдослучайной последовательности чисел.

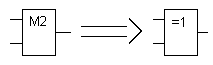

Сумматор по модулю 2:

| x1 | x2 | y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Условное графическое обозначение:

Двухвходовые сумматоры на входе D используются лишь в начальный момент для установки начального кода. На вход триггера Q0 устанавливается многовходовой сумматор, на вход которого заводят прямые или инверсные выходы триггеров. Количество разрядов которые заводят на вход М2 не регламентируются (может быть 1, а может и n+1). Если на вход М2 заводятся только прямые значения Q или четное количество инверсных, то счетчику обязательно требуется сигнал «Пуск». Если число инверсных входов не четно, то сигнал «Пуск» не обязателен, а тогда не нужны и двухвходовые сумматоры по модулю 2.

Многовходовой сумматор дополнительно может быть установлен и на входы других разрядов, не только Q0. В стандартном полиноминальном счетчике на вход многовходового сумматора М2 заводят только прямые значения Q и начальная установка такого счетчика состоит из двух этапов:

- В начале подают сигнал R, который сбрасывает все триггера и счетчик получает значение 0000. В этом состоянии он может находиться сколь угодно долго.

- Далее на один такт сигнала С подается сигнал «Пуск». И в те разряды, куда заведен сигнал «Пуск» вдвинется 1. Во время работы сигнал «Пуск» равен 0. При этом получаем обычный сдвиговый регистр, только на вход Dr заведена сумма разрядов.

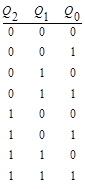

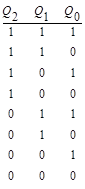

Пример: Стандартный счетчик на 7 состояний.

| Q2 | Q1 | Q0 | D1 | Пуск | ||

| 0 | 0 | 0 | 0 | 1 | ||

0 0

| 0 | 1 | 1 | 0 | ||

| 0 | 1 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 0 | ||

| 0 | 1 | 1 | 1 | 0 | ||

| 1 | 1 | 0 | 1 | 0 | ||

| 1 | 1 | 1 | 0 | 0 | ||

| 1 | 0 | 1 | 0 | 0 | ||

| 0 | 0 | 1 | 1 | 0 |

М=7 (модуль счета)

| Q2 | Q1 | Q0 | D1 |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 |

М=7 (модуль счета)

Если полиноминальный счетчик имеет 2n-1 состояний и одно состояние – начальное устойчивое, то его называют генератор псевдослучайной последовательности.

Проблемы проектирования БИС

Повышение степени интеграции ИМС естественным образом сопровождается и порождает ограничения и проблемы разнообразного свойства, в ряду которых выделяются следующие [1, 3, 4, 9, 10, 12, 14]:

– уменьшения геометрических размеров элементов ИМС;

– увеличения размеров конструкций, реализуемых методами групповой технологии производства (кристаллов, плат);

– совершенствования элементной базы устройств;

– совершенствования структурной организации устройств;

– совершенствования конструкций корпусов;

– совершенствования средств проектирования, сопровождения проектов в производстве и эксплуатации.

Возможности уменьшения геометрических размеров радиоэлементов ИМС определяются, с одной стороны, необходимыми электрическими параметрами, а с другой — разрешающей способностью технологических процессов и оборудования. Технические методы и оборудование производства изделий микроэлектроники совершенствуются, приближая минимальные геометрические размеры элементов к предельным значениям, сравнимым с длиной световой волны. Дальнейшее повышение степени интеграции может достигаться для принятой технологии увеличением размеров кристаллов и плат, развитием конструкций объёмного исполнения. Реализация технологических процессов производства БИС становится доступной исключительно автоматическому и автоматизированному оборудованию.

Увеличение размеров конструкций кристаллов и плат сопровождается повышением процента бракованных изделий в процессе производства. Обеспечение приемлемого процента выхода годных изделий при увеличении размеров конструкций кристаллов и плат является достаточно острой проблемой их производства. Требования к качеству технологического процесса характеризуются выражением [10]

P = exp (–B∙ d ∙ S), (5.1)

где P — процент выхода годных изделий;

В — коэффициент производственной «поражаемости» изделий;

d — плотность на единице площади изделия;

S — площадь, занимаемая изделием.

Согласно выражению (5.1), процент Р выхода годных БИС уменьшается с увеличением площади кристалла или платы. Эту зависимость можно улучшить, совершенствованием качества технологии путем уменьшения коэффициента «поражаемости» В и плотности дефектов d.

Коэффициент производственной «поражаемости» БИС рассматривается как отношение части площади, дефект на которой выводит изделие из строя, к полной площади, занимаемой БИС. В свою очередь, плотность дефектов есть число поражающих дефектов на единице площади пластины.

Высокая плотность упаковки и увеличение числа элементов на кристалле повышают энергопотребление и тепловыделение быстродействующих микроэлектронных устройств и обуславливают повышение удельной мощности рассеяния до (10–20) Вт/см3. Отвод таких мощностей требует проектирования специальных конструкций корпусов с принудительным охлаждением.

Высокие быстродействие схем (менее 1 мкс) и энергопотребление приводят к повышению скорости переключения тока до значений dI/dt ≈ (10–20)∙106 А/с, вследствие чего даже незначительные индуктивности монтажа вызывают существенные колебания напряжения питания и обостряют проблему влияния паразитных связей и помех.

Острота названных проблем снижается применением элементной базы адекватной уровню проблем. Наиболее эффективные по энергии переключения логические элементы, исполненные по биполярной и полевой технологии рассмотрены в разд. 2, 3 пособия. В основу новых схемотехнических решений по элементной базе закладывается снижение рабочих потенциалов логических уровней до единиц термического потенциала и рабочих токов до единиц микроампер. Структуры и решения, направленные на сокращение потерь рабочей площади кристалла, обсуждались в подразд. 2.20.

Совершенствование структурной организации устройств высокой степени интеграции осуществляется в направлениях:

– разбиения изделия на функционально полные конструктивные модули с целью снижения потерь от обработки бракованных изделий;

– разбиения изделия на функционально полные конструктивные модули для покрытия спроса на рынке этих функциональных изделий;

– поиска и проектирования новых структурных образований для достижения более совершенных функциональных и параметрических качеств устройств.

Повышение степени интеграции, сопровождаемое увеличением габаритов кристаллов и плат, обуславливает увеличение размеров установочной (монтажной) зоны корпусов ИМС и, преимущественно, сопровождается увеличением числа выводов для внешних соединений изделий. Названные факторы требуют, наряду с решением задач проектирования кристаллов и плат, решения задачи проектирования новых конструкций корпусов (увеличенных размеров при повышенном числе выводов). Если корпуса микросхем первой, второй степени интеграции имели 12–40 выводов для внешних подключений, то корпуса современных микропроцессоров имеют более 60–200 выводов и являются многослойными коммутационными платами, оборудованными выводами внешних подключений. Параллельно решаются проблемы совершенствования структурной организации устройств в части сокращения числа выводов внешних связей использованием ресурсов последовательной передачи информации.

Следствием усложнения функций, выполняемых БИС, и увеличения числа выводов является усложнение и повышение трудоёмкости контроля функционирования и проведения испытаний БИС. Функциональный контроль БИС без применения специализированного автоматического оборудования становится невозможным.

Повышение степени интеграции существенно повышает трудозатраты по выполнению проектно-конструкторских работ, составной частью которых является проектирование топологии микросхем. Согласно [4] трудоемкость ручного проектирования БИС может быть приближенно оценена следующими формулами:

Та = 70 ∙ N 0,55 (5.2 a)

для аналоговых схем,

Тd = 45 ∙ N 0,55 (5.2 б)

для цифровых схем.

В выражениях (5.1) N есть число элементов БИС, а Тi — трудоемкость проектирования, в часах. При N = 10000 время проектирования составляет около 4500 часов при годовом ресурсе рабочего времени одного проектировщика 2200 часов. К приведенной оценке следует добавить проблему обнаружения и исправления ошибок проектирования, число которых повышается с увеличением числа компонуемых элементов.

Применение средств систем автоматизированного проектирования (САПР) БИС снижает трудоемкость проектирования до значения, определяемого по формуле [5]

Т = 22 ∙ N 0,22. (5.2 в)

Уже при четвёртой степени интеграции рост ошибок, вносимых при ручном проектировании, и затрат времени на их обнаружение и исправление делает процесс достижения положительного результата проектирования проблематичным.

Проектирование БИС без применения САПР становится практически невозможным, как по срокам исполнения и внедрения проекта в приемлемые сроки, так и самому факту экономически оправданного достижения результата.

Применение и совершенствование средств автоматизации проектирования на разных этапах этого процесса, средств автоматизированного и автоматического сопровождения проектов в производстве и эксплуатации изделий повышенной степени интеграции является основной составляющей технического обеспечения проектов проектирования БИС.

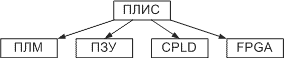

Классификация ПЛИС

В настоящее время программируемые логические интегральные схемы развиваются по нескольким направлениям, поэтому возникла необходимость как то различать эти микросхемы. Классификация программируемых логических интегральных схем (ПЛИС) приведена на рисунке 2.1.

Рисунок 2.1. Классификация программируемых логических интегральных схем (ПЛИС)

Следует отметить, что программируемые логические матрицы (ПЛМ) реализуют хорошо известные принципы создания цифровой комбинационной схемы по таблице истинности (СДНФ). Применение постоянных запоминающих устройств (ПЗУ) в качестве комбинационной схемы позволяет вообще обойтись без составления комбинационной функции и ее минимизации. Области применения этих микросхем сразу определились. ПЗУ применялись для создания комбинационных схем с малым количеством входов. При росте количества входов сложность внутреннего устройства ПЗУ и его цена резко возрастали (по квадратичному закону). ПЛМ позволяли реализовывать таблицы истинности с относительно малым количеством единичных сигналов на выходе и большим количеством входных сигналов, либо хорошо минимизирующиеся логические функции.

Первоначально цифровые устройства с памятью реализовывали либо на нескольких ПЛМ, либо добавляли внешние триггеры , затем стали включать их в состав программируемых логических устройств. По мере увеличения степени интеграции микросхем возникла необходимость объединять полученные сложные микросхемы на одном кристалле. В результате возникли сложные программируемые логические устройства (CPLD). В них появилась возможность программировать не только таблицу истинности комбинационного устройства, но и линии соединения входов и выходов ПЛД между собой. Таким образом можно считать CPLD дальнейшим развитием ПЛМ и ПЛД.

Точно так же развивались цифровые устройства на ПЗУ. Сначала к их выходам добавили триггер. Естественно предоставили возможность отключать его при необходимости. Затем несколько этих схем разместили на одном кристалле и предоставили возможность программировать соединения их входов и выходов между собой. Подобные устройства называются FPGA.

Узлы и устройства ЭВМ

Иерархия уровней элементов. Характеристики ИС. Виды цифровых устройств.

Элементы (в широком смысле) – наименьшие функциональные части, на которые разбивают цифровое устройство при логическом проектировании и технической реализации.

Иерархия уровней элементов:

1. Электронные компоненты (простейшие элементы) (элементы в узком смысле): резисторы, конденсаторы, диоды, транзисторы.

2. Логические и запоминающие элементы: коньюнкторы, дизьюнкторы, элементы Шеффера, элементы Пирса и др., различные виды триггеров.

3. Функциональные узлы или субсистемы: регистры, счетчики, дешифраторы, мультиплексоры и сумматоры.

4. Функциональные устройства: АЛУ, запоминающие устройства и др.

5. Вычислительная машина в целом: микроконтроллеры.

Каждый из уровней элементов выпускается в виде интегральных микросхем (ИС).

Каждый предшествующий уровень является основой для следующего.

Дата: 2019-02-25, просмотров: 501.