Физические форма представления информации в ЭВМ

Информация в ЭВМ кодируется, как правило, в двоичной или в двоично-десятичной системе счисления. Система счисления - это способ наименования и изображения чисел с помощью символов, имеющих определенные количественные значения.

В зависимости от способа изображения чисел системы счисления делятся на позиционные и непозиционные.

В позиционной системе счисления количественное значение каждой цифры зависит от ее места (позиции) в числе. В непозиционной системе счисления цифры не меняют своего количественного значения при изменении их расположения в числе.

Аналоговая информация характеризуется плавным изменением ее параметров. Основные параметры наиболее простых синусоидальных аналоговых сигналов могут непрерывно и плавно меняться.

Дискретная информация базируется на ряде фиксированных уровней представления заданных параметров, взятых в определенные промежутки времени. Если этих уровней много, можно говорить о цифровом представлении информации, то есть когда в определенные дискретные моменты они принимают конкретные дискретные значения. К счастью, аналоговую информацию легко преобразовать в цифровую. Это делают так называемые аналогоцифровые преобразователи (АЦП). Обратное преобразование обеспечивают цифроаналоговые преобразователи (ЦАП).

В качестве носителей аналоговой информации могут использоваться различные физические величины, принимающие различные значения на некотором интервале, например, электрический ток, радиоволна и т.д. При дискретизации, то есть при преобразовании непрерывных изображений и звука в набор дискретных значений в форме кодов, за основу берется какое-либо конкретное значение, а любые другие, отличающиеся от нормы, просто игнорируются.

Основные понятия математической логики

Математическая логика — раздел математики, изучающий доказательства и вопросы оснований математики.

Основным понятием математической логики является высказывание.

Высказывание — это повествовательное предложение, про которое всегда можно сказать истинное оно или ложное.

Истинные высказывания обозначаются — 1, а ложные — 0

Высказывания бывают просты и сложные. Сложные состоят из простых, соединенных знаками логических операций.

Высказывания обозначаются заглавными буквами латинского алфавита (простые): A,B,C,D…

Рассмотрим логические операции.

1. Инверсия

• соответствует частице НЕ

• обозначается А

• называется: отрицание

2. Конъюнкция

• соответствует союзу И

• обозначается &, ?

• называется: логическое умножение

3. Дизъюнкция

• соответствует союзу ИЛИ

• обозначается v

• называется: логическое сложение

Понятие о системе элементов

Анализ и синтез логических цепей производится на основе математического аппарата алгебры логики, или булевой алгебры. Переменные здесь могут принимать только одно из двух значений: 0 или 1. Над переменными могут производиться три основных действия: логическое сложение, логическое умножение и логическое отрицание, что соответствует логическим функциям ИЛИ, И, НЕ.

Логическое сложение (дизъюнкция) обозначается символом "+" или V (первая буква латинского слова vel-или). В качестве примера цепи, реализующей: функцию ИЛИ, можно привести параллельное соединение замыкающих контактов нескольких реле. Цепь, в которую входят эти контакты, будет замкнута, если сработает хотя бы одно реле рис. 2. Таким образом, логическая сумма равна единице тогда, когда равно единице одно или несколько слагаемых:

Логическое умножение (конъюнкция) обозначается точкой или символом ^ либо вообще в буквенных выражениях никак не обозначается. Функцию И реализуют, например, соединенные последовательно замыкающие контакты нескольких реле. Цепь в этом случае будет замкнута только тогда, когда сработают все реле рис. 3:

Логическое отрицание (инверсия) обозначается чертой над обозначением аргумента. Моделью ячейки, реализующей функцию НЕ, может служить размыкающий контакт реле. При срабатывании реле цепь, в которую входит такой контакт, будет размыкаться. Таким образом, инверсия единицы равна нулю, инверсия нуля - единице, а двойная инверсия не изменяет значения переменной: 0=1; 1=0; 0=0; 1=1.

Распределение линий шины.

Шина ВМ складывается из шин адреса, данных и управления.

Шина адреса. На шине адреса могут передаваться адреса ячеек памяти, номера регистров ЦП, адреса портов УВВ и т.д. Число сигнальных линий, выделенных для передачи адреса(ширина шины адреса), определяет максимально возможный размер адресного пространства. Это одно из базовых характеристик шины, поскольку от нее зависит потенциальная емкость адресуемой памяти и число обслуживаемых портов ввода-вывода.

Шина данных. Совокупность линий, служащих для передачи данных между модулями системы, называют шиной данных. Важнейшая характеристика шины - пропускная способность и ее ширина. Ширина шины данных - это количество бит, которое может быть передано по шине за одну транзакцию(цикл шины). Цикл шины следует отличать от периода тактовых импульсов. Одна транзакция на шине может занимать несколько тактовых импульсов. Ширина шины данных составляет 8, 16, 32, 64 или 128 бит. Ширина шины данных существенно влияет на производительность ВМ. Применение раздельных шин адреса и данных позволяет повысить эффективность использования шины, особенно в транзакциях записи, так как адрес ячейки памяти и записываемые данные можно передавать одновременно.

Шина управления. По ним передается управляющая информация и информация о состоянии участвующих в транзакции устройств. Сигнальные линии, входящие в шину управления, можно условно разделить на несколько групп.

Первая группа. Это такие линии, по которым передаются сигналы управления транзакциями, т.е. сигналы, определяющие:

· Тип выполняемой транзакции (чтение или запись)

· Количество байтов, передаваемых по шине данных

· Какой тип адреса выдан на шину адреса

· Какой протокол передачи должен быть применен(синхронный, асинхронный)

На перечисленные цели обычно отводится от 2 до 8 сигнальных линий.

Вторая группа. Сюда входят линии передачи информации о состоянии(статуса).

В эту группу входят от 1 до 4 линий, по которым ведомое устройство может информировать ведущего о своем состоянии или передать код возникшей ошибки.

Третья группа. Это линии арбитража. Арбитраж необходим для выбора одного из нескольких ведущих, одновременно претендующих на доступ к шине. Число линий арбитража может быть от 3 до 11.

Четвертая группа. Это линии прерывания. По ним передаются запросы на обслуживание, посылаемые от ведомых устройств к ведущему. Под запросы отводится от 1 до 2 линий.

Пятая группа. Сюда входят линии для организации последовательных локальных сетей. Наличие от 1 до 4 таких линий становится общепринятой практикой. Последовательная передача данных протекает значительно медленнее, чем параллельная и поэтому выгоднее строить последовательные сети, не загружая быстрые линии основных шин адреса и данных.

Имеется группа линий (от 2 до 6) для тактирования и синхронизации. При проектировании шины таким линиям уделяется особое внимание.

12. Понятие мультиплексированная шина.

Для экономии линий адреса и линий данных их объединяют. Так получается мультиплексируемая шина адреса /данных.Такая шина работает по принципу(адрес)(данные)(адрес)(…)

Рис8.

Структура мультиплексирования шин адреса и данных.

Структура мультиплексирования шин адреса и данных.

//Из Интернета//

Для снижения общего количества линий связи магистрали часто применяется мультиплексирование шин адреса и данных. То есть одни и те же линии связи используются в разные моменты времени для передачи как адреса, так и данных (в начале цикла — адрес, в конце цикла — данные). Для фиксации этих моментов (стробирования) служат специальные сигналы на шине управления. Понятно, что мультиплексированная шина адреса/данных обеспечивает меньшую скорость обмена, требует более длительного цикла обмена По типу шины адреса и шины данных все магистрали также делятся на мультиплексированные и немультиплексированные.

В некоторых мультиплексированных магистралях после одного кода адреса передается несколько кодов данных (массив данных). Это позволяет существенно повысить быстродействие магистрали. Иногда в магистралях применяется частичное мультиплексирование, то есть часть разрядов данных передается по немультиплексированным линиям, а другая часть — по мультиплексированным с адресом линиям

13. Структуры ВМ и ВС.

//из конспектов к 1 лекции//

/*ВМ - это комплекс технических и программных сред, предназначенных для автоматизации, подготовки данных и решения задач пользователя.

ВС - совокупность взаимосвязанных и взаимодействующих ЦП или ВМ, периферийного оборудования(принтеры, сканеры, плоттеры и т.д.) также предназначенные для подготовки данных и решения задач пользователя.

Структура ВМ - охватывает вопросы физического построения, состава устройств и связи между ними.

Архитектура - логическое построение ВМ, какой она представляется программисту(память, регистры, языки программирования, команды ЦП)

Рис.1 Уровни детализации ВМ:

A. Уровень «черного ящика»

Основы организации ВМ и ВС.

Компьютер состоит из таких компонентов как процессор, память основная и вспомогательная , устройства ввода/вывода. Достоинства и недостатки архитектуры ВМ и ВС зависят от способа соединения указанных компонентов. В самом общем подходе по организации ВМ и ВС можно говорить о двух основных типах структур ВМ и двух типах структур ВС.

Рис.3 структура ВМ на базе общей шины

В целом следует признать, что при сохранении фон-неймановской концепции последовательного выполнения команд программы шинная архитектура в чистом ее виде оказывается недостаточно эффективной. Более распространена архитектура с иерархией шин, где помимо магистральной шины имеется еще несколько дополнительных шин. Они могут обеспечивать непосредственную связь между устройствами с наиболее интенсивным обменом, например процессором и кэш-памятью. Другой вариант использования дополнительных шин – объединение однотипных устройств ввода/вывода с последующим выходом с дополнительной шины на магистральную. Все эти меры позволяют снизить нагрузку на общую шину и более эффективно расходовать ее пропускную способность.

Структура ВС(рис.4-5)

Структура системы — состав, порядок и принципы взаимодействия элементов системы, определяющие основные свойства системы. Если отдельные элементы системы разнесены по разным уровням и внутренние связи между элементами организованы только от вышестоящих к нижестоящим уровням и наоборот, то говорят об иерархической структуре системы. Чисто иерархические структуры встречаются практически редко, поэтому, несколько расширяя это понятие, под иерархической структурой обычно понимают и такие структуры, где среди прочих связей иерархические связи имеют главенствующее значение.

Архитектура системы — совокупность свойств системы, существенных для пользователя.

Понятие «вычислительная система» предполагает наличие множества процессоров или законченных вычислительных машин, при объединении которых используется один из двух подходов. В вычислительных системах с общей памятью (рис. 4) имеется общая основная память, совместно используемая всеми процессорами системы. Связь процессоров с памятью обеспечивается с помощью коммуникационной сети, чаще всего вырождающейся в общую шину. Таким образом, структура ВС с общей памятью аналогична рассмотренной выше архитектуре с общей шиной, в силу чего ей свойственны те же недостатки. Применительно к вычислительным системам данная схема имеет дополнительное достоинство: обмен информацией между процессорами не связан с дополнительными операциями и обеспечивается за счет доступа к общим областям памяти

|

Рис.4Структура ВС с общей памятью

Альтернативный вариант организации – распределенная система, где общая память вообще отсутствует, а каждый процессор обладает собственной локальной памятью

|

Рис.5 Структура распределенной ВС

(Рис5.). Часто такие системы объединяют отдельные ВМ. Обмен информацией между составляющими системы обеспечивается с помощью коммуникационной сети посредством обмена сообщениями. Подобное построение ВС снимает ограничения, свойственные для общей шины, но приводит к дополнительным издержкам на пересылку сообщений между процессорами или машинами.

14. Перспективы совершенствования ВМ и ВС. Принципы развития СБИС .

Совершенствование архитектуры вычислительных машин и систем началось момента появления первых ВМ и не прекращается по сей день. Каждое изменение в архитектуре направлено на абсолютное повышение производительности или, крайней мере, на более эффективное решение задач определенного класса. Эволюцию архитектур определяют самые различные факторы, главные из которых показаны рис. 6. Не умаляя роли ни одного из них, следует признать, что наиболее очевидные успехи в области средств вычислительной техники все же связаны технологическими достижениями.

С каждым новым технологическим успехом многие из архитектурных переходят на уровень практической реализации. Очевидно, что процесс будет продолжаться и в дальнейшем, однако возникает вопрос: «Насколько быстро?» Косвенный ответ можно получить, проанализировав тенденции совершенствования технологий, главным образом полупроводниковых.

Рис.6 Факторы,влияющие на развитие архитектуры ВС

Принципы развития СБИС.

Тенденция развития СБИС.

Основная борьба идет на размещение транзисторов, конденсаторов, резисторов на кристалле.

Есть два пути:

1) Увеличение площади кристалла

2) Уменьшение размеров соед. частей и элементов, транзисторов, конденсаторов и резисторов

В 1965 г.Мор высказал мысль -на кристалле удваивается размещаемые элементы через год. Через два года уточнил. Так Pentium 4 содержит 41 млн. транзисторов.

Кристалл для особых нужд выращивают в космосе в виде болванок, затем режут на диски толщиной 1 см, а из них вырезают прямоугольники. Это и есть кристалл.

15. Перспективы исследования в области архитектуры ЭВМ .

Основные направления исследований в области архитектуры ВМ и ВС можно условно разделить на две группы: эволюционные и революционные. К первой группе следует отнести исследования, целью которых является совершенствование методов реализации уже достаточно известных идей. Изыскания, условно названные революционными, направлены на создание совершенно новых архитектур, принципиально отличных от уже ставшей традиционной фон-неймановской архитектуры.

Большинство из исследований, относимых к эволюционным, связано с совершенствованием архитектуры микропроцессоров (МП). В принципе кардинально новых архитектурных подходов в микропроцессорах сравнительно мало. Основные идеи, лежащие в основе современных МП, были выдвинуты много лет тому назад, но из-за несовершенства технологии и высокой стоимости реализации нашли применение только в больших универсальных ВМ (мэйнфреймах) и суперЭВМ. Наиболее значимые из изменений в архитектуре МП связаны с повышением уровня параллелизма на уровне команд (возможности одновременного выполнения нескольких команд). Здесь в первую очередь следует упомянуть конвейеризацию, суперскалярную обработку и архитектуру с командными словами сверхбольшой длины (VLIW). После успешного переноса на МП глобальных архитектурных подходов «больших» систем основные усилия исследователей теперь направлены на частные архитектурные изменения.

Примерами таких эволюционных архитектурных изменений могут служить: усовершенствованные методы предсказания переходов в конвейере команд, повышение частоты успешных обращений к кэш-памяти за счет усложненных способов буферизации и т. п.

Наблюдаемые нами достижения в области вычислительных средств широкого применения пока обусловлены именно «эволюционными» исследованиями. Однако уже сейчас очевидно, что, оставаясь в рамках традиционных архитектур, мы довольно скоро натолкнемся на технологические ограничения. Один из путей преодоления технологического барьера лежит в области нетрадиционных подходов. Исследования, проводимые в этом направлении, по нашей классификации отнесены к «революционным». Справедливость такого утверждения подтверждается первыми образцами ВС с нетрадиционной архитектурой.

Оценивая перспективы эволюционного и революционного развития вычислительной техники, можно утверждать, что на ближайшее время наибольшего прогресса можно ожидать на пути использования идей параллелизма на всех его уровнях и создания эффективной иерархии запоминающих устройств.

Стековая и кэш память

Организация ассоциативной и стековой памяти

Ассоциативные запоминающие устройства

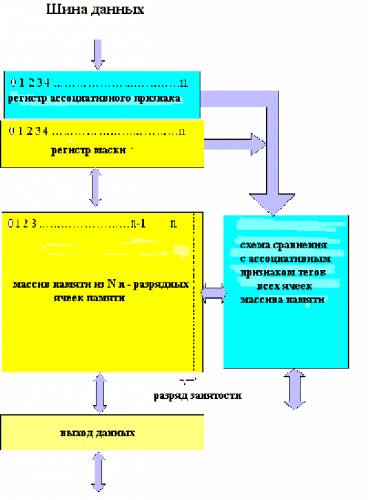

В ассоциативных запоминающих устройствах поиск информации производится по ассоциативному признаку, записанному в каждую ячейку памяти.

В регистр маски записывается слово, разрешающее запрос по всем или только некоторым разрядам ассоциативного признака, применение маски позволяет сократить или расширить область поиска.

Поиск информации производится параллельно по всем ячейкам путем сравнения запроса с ассоциативным признаком каждой ячейки.

Результат поиска формирует специальная комбинационная схема, вырабатывающая сигналы, оповещающие об отсутствии слов, удовлетворяющих условиям поиска, о наличии только одного слова, о наличии нескольких слов, имеющих такой ассоциативный признак.

После формирования и обработки оповещающих сигналов схемой управления производится считывание необходимой информации. При записи отыскивается свободная ячейка по значению разряда занятости, в первую найденную свободную ячейку записывается информация.

Проверка разряда занятости производится по установке n-го разряда (разряда занятости) маски. При использовании дополнительных комбинационных схем в ассоциативной памяти можно выполнять различные логические операции, определяя максимальное или минимальное число, количество слов, имеющих одинаковый ассоциативный признак и т.д. На рис.1 показана структура ассоциативной памяти. Ячейки памяти ассоциативного запоминающего устройства должны быть элементами статической памяти, в ассоциативной памяти обращение производится ко всем ячейкам одновременно и не должно прерываться циклами регенерации. Ассоциативная память наиболее быстродействующая, но очень дорогая, так как требует введения дополнительно схемы сравнения, позволяющей осуществить поиск, для каждой ячейки памяти. Поэтому такая память обычно не используется в чистом виде, а быстродействующие устройства памяти типа Кэш обычно выполняются как частично ассоциативные.

Рис.1. Организация ассоциативной памяти.

В микропроцессорах ассоциативная память (память с выборкой по содержанию ) используются в составе кэш-памяти для хранения адресной части команд и операндов исполняемой программы. При этом нет необходимости обращаться к ОЗУ за следующей командой или требуемым операндом, достаточно поместить в регистр ассоциативного признака необходимый адрес и, если искомая информация имеется в кэш памяти, то она сразу будет выдана. Обращение к оперативной памяти будет необходимо лишь при отсутствии требуемой информации в кэш. За счет такого использования кэш сокращается число обращений к ОЗУ, а это позволяет экономить время, так как обращение к кэш требует приблизительно в 10 раз меньше времени, чем обращение к ОЗУ.

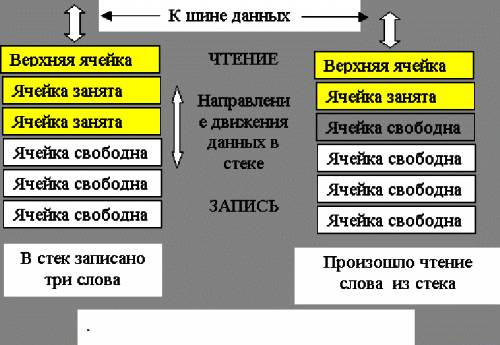

Стековая память

Рассмотрим организацию стековой памяти, как памяти, образованной из связанных между собой ячеек памяти, в которых информация при записи в стек нового слова смещается вниз (Рис.2). Обмен информацией осуществляется только через верхнюю ячейку памяти. При считывании слов из стека, слово может удаляться из стековой памяти или сдвигаться по кольцу, в зависимости от организации стека. Режим чтения –последним вошел, первым вышел- называютLIFO (Last In First Out).

Рис.2. Организация стековой памяти.

Аппаратная реализация такой памяти не всегда целесообразна и зачастую стековая память организуется в основной памяти компьютера программно, что позволяет изменять объем стека в зависимости от необходимости. При организации стека в основной памяти выделяется специальный адресный регистр –"указатель стека.”. В указателе стека находится адрес последнего записанного в стек слова. При записи слова в стек адрес вершины стека автоматически уменьшается, при чтении - автоматически увеличивается. Стековая память используется обычно для сохранения состояния текущей программы при обработке прерывания. После выполнения прерывающей программы состояние всех регистров, существовавшие в момент прерывания программы восстанавливается в последовательности, обратной последовательности записи. Можно сохранять в стеке и данные программы, это удобно тем, что при обращении к стеку не требуется указывать в программе адреса ячейки памяти, извлечение информации из стека так же происходит без указания адреса.

Характеристики процессоров

Первоначально основной характеристикой процессора была его тактовая частота, то есть количество машинных циклов, выполняемых процессором за секунду. Таким образом, производительность процессора напрямую зависит от тактовой частоты его работы.

Все предыдущие поколения микропроцессоров фирмы Intel маркировались в соответствии с тактовой частотой их работы. Например, маркировка Pentium 4 2,8 ГГц означала, что процессор был разработан фирмой Intel, отн приближаться к своему предельному значению, при котором транзисторы, находящиеся внутри микропроцессора, не успевают переключаться, и, как следствие, процессор работает со сбоями, что снижает его производительность.

С увеличением производительности процессоров на передний план выходят такие характеристики, как объём кэша, частота шины, а также ряд других параметров. Они в меньшей степени, чем тактовая частота, влияют на производительность, однако при постоянном значении тактовой частоты способны увеличить производительность микропроцессора.

В связи с тем, что эти параметры могут быть различными для процессоров одинаковой частоты, возникла необходимость в новой маркировке, которая отражала бы свойства каждого из процессоров наиболее полно.

Закон Амдала

Можно ли утверждать, что в ВМ из n-ЦП будет ускорение работать в n-раз? Оказывается, не будет.

Джин Амдал сформулировал закон в 1967 году, обнаружив простое по существу, но непреодолимое по содержанию ограничение на рост производительности при распараллеливании вычислений: «В случае, когда задача разделяется на несколько частей, суммарное время ее выполнения на параллельной системе не может быть меньше времени выполнения самого длинного фрагмента». Согласно этому закону, ускорение выполнения программы за счет распараллеливания её инструкций на множестве вычислителей ограничено временем, необходимым для выполнения её последовательных инструкций.

Амдал в 1967 году показал, что можно использовать max n=10 и при последующих увеличениях количества ЦП, ускорения не произойдет. Дело в том, что в любой программе будут 2 участка:

· последовательный участок, команды которого выполняются одним ЦП

· параллельный участок, команды которого могут выполняться несколькими ЦП

Он вывел формулу, отражающую показатель ускорения:

S=

Ts – время, затрачиваемое на программу одним ЦП

Tp – время для решения той же задачи на параллельной ВС (несколько ЦП)

f - доля команд, выполняемая последовательно

1-f - это доля команд, выполняемая параллельно

f*Ts - время выполнения последовательного участка программы

- время выполнения параллельного участка одним ЦП

- время выполнения параллельного участка одним ЦП

Tp = (f*Ts) +  - время выполнения всей программы одним ЦП

- время выполнения всей программы одним ЦП

S=  =

=  =

=

Если N велико, то limS= 1\f

Оказывается оптимальным ускорение будет тогда, когда f=0,1

Закон Амдала показывает, что прирост эффективности вычислений зависит от алгоритма задачи и ограничен сверху для любой задачи с f≠0 . Не для всякой задачи имеет смысл наращивание числа процессоров в вычислительной системе.

Более того, если учесть время, необходимое для передачи данных между узлами вычислительной системы, то зависимость времени вычислений от числа узлов будет иметь максимум. Это накладывает ограничение на масштабируемость вычислительной системы, то есть означает, что с определенного момента добавление новых узлов в систему будет увеличивать время расчёта задачи.

Конвейеризация вычислений

Важным элементом архитектуры, появившимся в i486, является конвейер – специальное устройство, реализующее обработку команд внутри процессора в несколько этапов. Вышеупомянутый конвейер имеет 5-ти ступенчатый конвейер. Соответствующие этапы включают:

- выборку команд из кэш-памяти или оперативной памяти;

- декодирование команды;

- генерацию адреса, в процессе которой определяются адреса операндов в памяти;

- выполнение операции с помощью АЛУ (арифметико-логического устройства);

- запись результаты ( адрес определяется конкретной машинной командой).

Каждому этапу соответствует своя схема в составе конвейера. Поэтому, когда после выборки команда поступает в блок декодирования, блок выборки оказывается свободным и может обрабатывать следующую команду. Таким образом, на конвейере могут находиться в разной стадии выполнения 5 команд, в результате чего возрастает скорость обработки отдельной команды.

Микропроцессоры, имеющие один конвейер называются скалярными, а более одного – суперскалярными. Микропроцессор Pentium имеет два конвейера, и поэтому может выполнять 2 команды за машинный такт.

Одной из наиболее важных прикладных характеристик ВМ является ее производительность. Повышение производительности - зачастую главное требование, стоящее перед

разработчиками ВТ. Можно выделить несколько основных путей решения этой задачи:

1. Совершенствование технологии производства ЭВМ («физический» путь) - повышение быстродействия логических элементов.

2. Распараллеливание вычислений.

3. Конвейеризация вычислений.

4. Специализация вычислений.

5. Аппаратная реализация сложных функций.

Параллелизмом).

MIMD - Multiple Instruction, Multiple Data – системы c множественным потоком команд и

множественным потоком данных; к подобному классу систем относится большинство параллельных многопроцессорных вычислительных систем.

Симметричные - Группа процессоров работает с общей ОП, при этом процессор имеет свой КЭШ, вычислительная система работает под управление одной ОС, процессоры обмениваются информацией через ОП, данная система обрабатывает все типы задач, использование общей ОП увеличивает производительность и скорость обработки данных, масштабируемость ограниченна и зависит от объема ОП.

Кластерные ВС - Кластеризация – технология, с помощью которой несколько серверов, сами являющиеся вычислительными системами, объединяются в единую систему более высокого ранга для повышения эффективности функционирования системы в целом.

Кластер — группа компьютеров, объединённых высокоскоростными каналами связи и представляющая с точки зрения пользователя единый аппаратный ресурс.

Один из первых архитекторов кластерной технологии Грегори Пфистер (Gregory F. Pfister) дал кластеру следующее определение: «Кластер — это разновидность параллельной или распределенной системы, которая: состоит из нескольких связанных между собой компьютеров;

используется как единый, унифицированный компьютерный ресурс». Иными словами, кластер компьютеров представляет собой несколько объединенных компьютеров, управляемых и используемых как единое целое. Они называются узлами и могут быть одно- или мультипроцессорными. В классической схеме при работе с приложениями все узлы разделяют внешнюю память на массиве жестких дисков, используя внутренние дисковые накопители для специальных функций (например, системных).Обычно различают следующие основные виды кластеров:

Кластеры высокой доступности(High-availability clusters, HA)

Кластеры распределения нагрузки (Load balancing clusters)

Кластеры повышенной производительности(High-performance clusters, HPC)

grid-системы

Системы с массовым параллелизмом – главные особенности – стандартные МП, физически распределенная память, сеть соединений с высокой пропускной способностью и малыми задержками, хорошая масштабируемость, асинхронная MIMD система с пересылкой сообщений, множество процессоров, имеющих отдельные адресные пространства. Так же для этих систем характерно наличие единого управляющего устройства, которое распределяет задания между множеством подчиненных ему устройств.

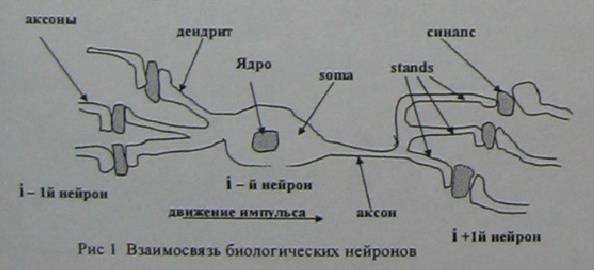

Биологический нейрон.

Элементом клеточной структуры мозга является нервная клетка - нейрон. Выделяют два вида отростков. Аксон — обычно длинный отросток, приспособленный для проведения возбуждения от тела нейрона. Дендриты — как правило, короткие и сильно разветвлённые отростки, служащие главным местом образования влияющих на нейрон возбуждающих и тормозных синапсов (разные нейроны имеют различное соотношение длины аксона и дендритов). Нейрон может иметь несколько дендритов и обычно только один аксон. Один нейрон может иметь связи с 20-ю тысячами других нейронов. Кора головного мозга человека содержит 10—20 миллиардов нейронов.

Нейрон в своем строении имеет много общих черт с другими клетками биоткани: тело нейрона окружено плазматической мембраной, внутри которой находится цитоплазма, ядро и другие составляющие клетки. Однако нервная клетка существенно отличается от иных по своему функциональному назначению. Нейрон выполняет прием, элементарное преобразование и дальнейшую передачу информации другим нейронам. Информация переносится в виде импульсов нервной активности, имеющих электрохимическую природу.

П.С. Это с тырнета. В хасановских бумажках не нашел ничего кроме картинки:

Перцептрон.

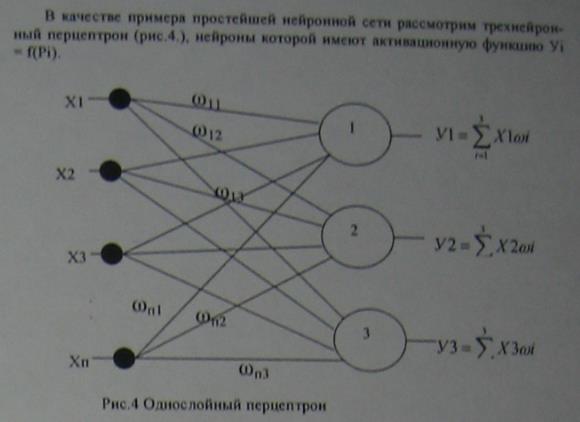

Перцептрон – это математическая и компьютерная модель восприятия информации мозгом (кибернетическая модель мозга), предложенная Фрэнком Розенблаттом в 1957 году и реализованная в виде электронной машины «Марк-1» в 1960 году. Перцептрон стал одной из первых моделей нейросетей, а «Марк-1» — первым в мире нейрокомпьютером. Несмотря на свою простоту, перцептрон способен обучаться и решать довольно сложные задачи. Основная математическая задача, с которой он справляется, — это линейное разделение любых нелинейных множеств, так называемое обеспечение линейной сепарабельности.

Перцептрон состоит из трёх типов элементов, а именно: поступающие от сенсоров сигналы передаются ассоциативным элементам, а затем реагирующим элементам. Таким образом, перцептроны позволяют создать набор «ассоциаций» между входными стимулами и необходимой реакцией на выходе. В биологическом плане это соответствует преобразованию, например, зрительной информации в физиологический ответ от двигательных нейронов. Согласно современной терминологии, перцептроны могут быть классифицированы как искусственные нейронные сети:

1. с одним скрытым слоем;

2. с пороговой передаточной функцией;

3. с прямым распространением сигнала.

Альтернатива из лекций – в 1958 году Ф. Розенблант предложил модель нейронной сети на основе микроэлектроники. Им было создано электронное устройство, названное Перцептроном. Простейший перцептрон – это обычная модель нейрона, реализованная на основе пороговых элементов, оперирующая двоичными числами. Аппаратная реализация оказалась чрезвычайно трудной изза высокой стоимости электронных элементов. Самые совершенные системы тогда содержали сотни нейтронов.

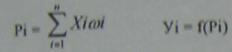

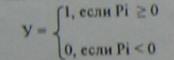

Pi – потенциал нейрона. Yi – сигнал пороговой функции нейрона.

Нелинейная функция активации перцептрона представляет собой дискретную функцию ступенчатого типа. Поэтому выходной сигнал будет принимать только два значения – 0 или 1 в соответствии с правилом

где Pi – выходной сигнал сумматора.

где Pi – выходной сигнал сумматора.

Нейрокомпьютеры.

Нейрокомпьютер — устройство переработки информации на основе принципов работы естественных нейронных систем. Эти принципы были формализованы, что позволило говорить о теории искусственных нейронных сетей. Проблематика же нейрокомпьютеров заключается в построении реальных физических устройств, что позволит не просто моделировать искусственные нейронные сети на обычном компьютере, но так изменить принципы работы компьютера, что станет возможным говорить о том, что они работают в соответствии с теорией искусственных нейронных сетей.

П.С. взято с тырнета. У Хасанова в бумажке пусто.

Физические форма представления информации в ЭВМ

Информация в ЭВМ кодируется, как правило, в двоичной или в двоично-десятичной системе счисления. Система счисления - это способ наименования и изображения чисел с помощью символов, имеющих определенные количественные значения.

В зависимости от способа изображения чисел системы счисления делятся на позиционные и непозиционные.

В позиционной системе счисления количественное значение каждой цифры зависит от ее места (позиции) в числе. В непозиционной системе счисления цифры не меняют своего количественного значения при изменении их расположения в числе.

Аналоговая информация характеризуется плавным изменением ее параметров. Основные параметры наиболее простых синусоидальных аналоговых сигналов могут непрерывно и плавно меняться.

Дискретная информация базируется на ряде фиксированных уровней представления заданных параметров, взятых в определенные промежутки времени. Если этих уровней много, можно говорить о цифровом представлении информации, то есть когда в определенные дискретные моменты они принимают конкретные дискретные значения. К счастью, аналоговую информацию легко преобразовать в цифровую. Это делают так называемые аналогоцифровые преобразователи (АЦП). Обратное преобразование обеспечивают цифроаналоговые преобразователи (ЦАП).

В качестве носителей аналоговой информации могут использоваться различные физические величины, принимающие различные значения на некотором интервале, например, электрический ток, радиоволна и т.д. При дискретизации, то есть при преобразовании непрерывных изображений и звука в набор дискретных значений в форме кодов, за основу берется какое-либо конкретное значение, а любые другие, отличающиеся от нормы, просто игнорируются.

Основные понятия математической логики

Математическая логика — раздел математики, изучающий доказательства и вопросы оснований математики.

Основным понятием математической логики является высказывание.

Высказывание — это повествовательное предложение, про которое всегда можно сказать истинное оно или ложное.

Истинные высказывания обозначаются — 1, а ложные — 0

Высказывания бывают просты и сложные. Сложные состоят из простых, соединенных знаками логических операций.

Высказывания обозначаются заглавными буквами латинского алфавита (простые): A,B,C,D…

Рассмотрим логические операции.

1. Инверсия

• соответствует частице НЕ

• обозначается А

• называется: отрицание

2. Конъюнкция

• соответствует союзу И

• обозначается &, ?

• называется: логическое умножение

3. Дизъюнкция

• соответствует союзу ИЛИ

• обозначается v

• называется: логическое сложение

Дата: 2019-12-10, просмотров: 402.