1.Назначение микросхем памяти и их разновидности.

Компактная микроэлектронная «память» широко применяется в современной электронной аппаратуре самого различного значения. Память определяют как функциональную часть ЭВМ, предназначенную для записи, хранения и выдачи команд и обрабатываемых данных. Комплекс технических средств, реализующих функцию памяти, называют запоминающим устройством (ЗУ).

Для обеспечения работы процессора (микропроцессора) необходимы программа, т.е. последовательность команд и данные, над которыми процессор производит предписываемые командами операции. Команда и данные поступают в основную память ЭВМ через устройство ввода, на выходе которого они получают цифровую форму представления, т.е. форму кодовых комбинаций (0 и 1). Основная память, как правило, состоит из ЗУ двух видов – оперативного (ОЗУ) и постоянного (ПЗУ).

ОЗУ предназначено для хранения переменной информации, оно допускает изменение своего содержимого в ходе выполнения процессором вычислительных операций с данными. Это значит, что процессор может выбрать (режим считывания) из ОЗУ код команды и данные и после обработки поместить в ОЗУ (режим записи) полученный результат. Причём возможно размещение в ОЗУ новых данных на местах прежних, которые этом случае перестают существовать. Таким образом, ОЗУ может работать в режимах записи, считывания и хранения информации.

ПЗУ содержит информацию, которая не должна изменятся в ходе выполнения процессором программы. Такую информацию составляют стандартные подпрограммы, табличные данные, коды физических констант и постоянных коэффициентов и т.п. И эта информация заносится в ПЗУ предварительно, например, путём пережигания легкоплавких перемычек в структуре ПЗУ, и в ходе работы процессора может только считываться. Таким образом, ПЗУ работает только в режимах хранения и считывания.

Функциональные возможности ОЗУ шире, чем ПЗУ: ОЗУ может работать в качестве ПЗУ, т.е. в режиме многократного считывания однократно записанной информации, а ПЗУ в качестве ОЗУ работать не может, т.к. не позволяет изменить однократно записанную в ней информацию. Далее коснёмся разновидности ПЗУ, которая допускает перепрограммирование, однако, и это ПЗУ не может заменить ОЗУ.

В свою очередь, ПЗУ обладает преимуществом перед ОЗУ в свойстве сохранять информацию при сбоях и отключении питания. Это свойство получило название энергозависимость. ОЗУ является энергозависимым, т.к. информация, записанная в ОЗУ, утрачивается при сбоях питания.

Для обеспечения надёжной работы ЭВМ при отказах питания нередко ПЗУ используют и в качестве памяти программ. В таком случае программа заносится в ПЗУ предварительно и уже не может быть заменена в данном ПЗУ другой программы. Очевидно, в использовании ПЗУ таким образом целесообразно прежде всего в специализированных автоматических устройствах, работающих по постоянной программе.

Запоминающее устройство, реализующее функции основной памяти, размещают рядом с процессором на одной плате, в одном блоке в зависимости от типа ЭВМ и такое ЗУ в этом смысле является внутренним. Быстродействие внутреннего ЗУ должно быть соизмеримо с быстродействием процессора. Практически это требование не всегда удаётся выполнить: по временным параметрам ОЗУ и ПЗУ отстают от процессора. По этому внутри ЭВМ размещают ещё и вспомогательную (буферную) память на быстродействующих регистрах, которые используются в качестве сверхоперативного ЗУ (СОЗУ) с небольшой информационной ёмкостью.

На ряду с внутренней памятью существует и внешняя память, реализуемая обычно на магнитных носителях: лентах или дисках.

Перейдём к вопросу о реализации внутренней и внешней памяти ЭВМ на основе микроэлектронной элементной базы. В современных вычислительных средствах и в электронной аппаратуре различного функционального назначения для построения ОЗУ и ПЗУ, а также регистровых ЗУ широко применяют полупроводниковые интегральные микросхемы. Микросхемы памяти изготавливают по полупроводниковой технологии на основе хранения с высокой степенью интеграции компонентов на кристалле, что определяет их принадлежность к большим интегральным схемам (БИС). Конструктивно БИС памяти представляет собой полупроводниковый кристалл с площадью в несколько десятков квадратных миллиметров, заключённый в корпус.

Для самой общей характеристики памяти принимают в расчёт информационную ёмкость, быстродействие, энергопотребление. Информационную ёмкость определяют числом единиц информации в битах и байтах, которые БИС памяти может хранить одновременно. Быстродействие характеризует временными параметрами, в частности временем цикла записи и считывания. Энергопотребление определяют произведением тока по потреблению и напряжения источников питания.

Для общего представления о микросхемах памяти как функциональных узлах электронной аппаратуры. Рассмотрим их наиболее характерные свойства, отражающие принцип построения и управления работы .

Рис.2. Микросхема памяти как функциональный узел: а – ОЗУ; б – ПЗУ.

Основной частью ОЗУ является массив элементов памяти, объединенных в матрицу накопителя. ЭП может хранить один бит (0 или 1) информации. Каждый ЭП имеет свой адрес. Для обращения к ЭП надо его «выбрать» с помощью кода адреса, сигналы которого подводят к соответствующим выводам микросхемы. ЗУ, ОЗУ или ПЗУ, которые допускают обращение по адресу к любому ЭП в произвольном порядке, называют запоминающим устройством с произвольной выборкой (ЗУПВ).

Разрядность кода адреса это «m», равная числу двоичных единиц в нём, определяет информационную ёмкость микросхема ОЗУ, т.е. число ЭП в матрице накопителя, т.е. информационная емкость 1024 бит.(В измерительной технике число 210=1024обозначают буквой К).

Для ввода и вывода информации служит вход и выход микросхемы. Для управления режимом микросхемы памяти необходим сигнал «Запись- считывание», значение 1 которого определяет режим записи бита информации в ЭП, 0 - режим считывания бита информации из ЭП. Такую организацию матрицы накопителя, при которой можно записывать или считывать один бит, называют одноразрядной.

Микросхемы ОЗУ по типу ЭП разделяют на статические и динамические. В статических ОЗУ в качестве ЭП применены статистические триггеры на биполярных или МДП – транзисторах (МДП – структура «металл – диэлектрик - полупроводник»). Как известно, статистический триггер способен сохранять свое состояние неограниченное время. Число состояний, в которых может находиться триггер, равно двум, что и позволяет использовать его для хранения двоичной единицы информации. В динамических ОЗУ ЭП выполнены на основе электрических конденсаторов, сформированных внутри полупроводникового кристалла. Такие ЭП не могут долго сохранять свое состояние, определяемое наличием или отсутствием эл. заряда и потому нуждаются в периодическом восстановлении (регенерации).Динамические ОЗУ отличаются от статистических ОЗУ большей информационной емкостью, что обусловлено меньшим числом компонентов в одном ЭП и, следовательно, более плотным их размещением в полупроводниковом кристалле, поэтому динамические ОЗУ сложнее в применении, поскольку нуждаются в организации принудительной регенерации, и в дополнительном оборудовании, и в усложнении устройств управления.

Микросхемы ПЗУ построены также по принципу матричной структуры накопителя (рис.2, б).Функции ЭП в микросхемах ПЗУ выполняют перемычки в виде проводников, диодов или транзисторов между шинами строк и столбцов в накопителе. В матрице наличие перемычки соответствует, например, 1 а ее отсутствие – 0. Микросхемы ПЗУ имеют словарную организацию и поэтому информация считывается в форме многоразрядного кода, т.е., словом. Совокупность ЭП в матрице накопителя, в которой размещается слово, называют ячейкой памяти (ЯП). Число ЭП в ЯП определяет ее разрядность n. Каждая ЯП имеет свой адрес и для обращения к определенной ЯП для считывания из нее информации необходимо к адресным выводам микросхемы подвести сигналы кода, соответствующего данной ячейки адреса. Число ячеек памяти равно 2m, а информационная емкость микросхемы – 2m*n бит.

Занесение информации в микросхемах ПЗУ, т.е. их программирование, осуществляют в основном двумя способами. Один способ заключается в формировании в накопителе перемычек в местах пересечения строк и столбцов матрицы через маску на заключительной технологической стадии изготовления микросхемы ПЗУ. Такие микросхемы ПЗУ называют масочными. Другой способ программирования микросхемы ПЗУ основан на пережигании легкоплавких перемычек в тех пересечениях шин строк и столбцов, куда должен быть записан 0 или 1, в зависимости от принятого кодирования. В исходном состоянии такая микросхема имеет в матрице перемычки во всех пересечениях строк и столбцов. Программирование осуществляет пользователь электрическими импульсами с помощью устройства доя программирования, называемого программатором.

Микросхемы ПЗУ, масочные (ПЗУМ) и программируемые (ППЗУ), допускают однократное программирование, поскольку оно осуществляется формированием или разрушением соединений в матрице. Один из вариантов реализации ПЗУ ориентирован на программирование заданных логических функций. Такие ПЗУ называют программируемыми логическими матрицами (ПЛМ).

Существует разновидность микросхем ПЗУ, допускающая неоднократное (сотни и тысячи циклов) программирование ( репрограммирование ) .ЭП в микросхемах репрограммируемых ПЗУ (РПЗУ) является МДП – транзистор, обладающий свойством переходить в состояние проводимости под воздействием импульса программирующего напряжения и сохранить это состояние длительное время (тысяча часов). Данный эффект обусловлен накоплением электрического заряда в под затворном диэлектрике. Если на транзистор не воздействовать импульсом программирующего напряжения, то он сохраняет закрытое для электрического тока состояние. Для стирания информации перед новым циклом программирования необходимо вытеснить накопленный под затвором заряд. В зависимости от способа выполнения этой операции микросхемы РПЗУ разделяют на два вида: со стиранием электрическим сигналом (РПЗУ - ЭС) и ультрафиолетовым светом (РПЗУ - УФ), которым полупроводниковый кристалл облучают через специальное окно в крышке корпуса. Микросхемы РПЗУ сохраняют информацию без питания, т.е. являются энергозависимыми.

Рис. 3.

В соответствии с принятой системой (ОСТ 11 073. 915 - 80) обозначение микросхемы содержит четыре обязательных элемента.

Первый элемент – цифра, указывающая группу микросхемы по конструктивно – технологическому признаку: 1, 5, 6, 7 – полупроводниковые, 2, 4, 8 – гибридные, 3 – прочие (пленочные, пьезокерамические). Второй элемент – две – три цифры, указывающие номер разработки данной серии. В сочетании указанные два элемента составляют номер серии, к которой принадлежит микросхема. Третий элемент – две буквы, обозначающие функциональную подгруппу и вид микросхемы: РУ – ОЗУ с управлением, РМ – матрицы ОЗУ, РЕ – масочные ПЗУ, РФ – репрограммируемое ПЗУ со стиранием информации ультрафиолетовым светом, РТ – программируемое ПЗУ, РР – репрограммируемое ПЗУ со стиранием информации электрическим сигналом, РЦ – ЗУ на ЦМД, ИР – регистры. Четвёртый элемент – порядковый номер разработки микросхемы в серии микросхем одного вида. Перед первым элементом для характеристики условий применения, материала и типа корпуса могут размещаться: К- общетехнического применения, Э – экспортное исполнение, Р – пластмассовый корпус типа 2, Е – металлополимерный корпус типа 2, М – керамический, металло- или стеклокерамический корпус типа 2, А – пластмассовый корпус типа 4, И – стеклокерамический корпус типа 4, Н – керамический кристаллоноситель, Б – бескорпусное исполнение. После четвёртого элемента может быть размещена дополнительная группа: А, Б, В и т.д., определяющее условие разбраковки микросхем по одному из функциональных параметров: быстродействию, потребляемому току и др.

2. Однократно программируемые ЗУ.

В настоящее время ППЗУ получили самое широкое распространение среди всех электрически программируемых устройств памяти. Принцип действия ячейки ППЗУ основан на физических процессах, позволяющих необратимо изменить электрическое сопротивление двухполюсника. По принципу действия различают два типа однократно программируемых запоминающих элементов (ЗЭ): резисторный и диодный, в которых программирование осуществляется соответственно пережиганием плавких перемычек и пробоем p-n переходов.

Бит информации, хранящийся в ЗЭ резисторного типа, определяется наличием или отсутствием плавкой перемычки. В режиме считывания на ЗЭ подают напряжение и хранимое значение бита определяют по значению тока, протекающего через перемычку. В состоянии после изготовления ЗЭ хранит 1 (сопротивление перемычки мало), а после пережигания плавкой перемычки – 0. в качестве плавких перемычек широко применяют тонкие плёнки из нихрома или поликристаллического кремния. Сопротивление перемычки составляет около 10 Ом. В результате программирования через перемычку пропускают импульс тока, плотностью около 107 А/см2, в результате чего она не обратимо разрушается. В следствии малых размеров перемычки и большой энергии, выделяемой при пережигании, физические процессы в плёнке достаточно сложны.

Работа ЗЭ диодного типа основана на необратимых явлениях, происходящих при пробое обратно смещенного p – n перехода. В исходном состоянии ЗЭ диодного типа хранит 0, а его обратное сопротивление очень велико. При программировании к диоду прикладывается запирающее напряжение повышенного уровня, под действием которого p – n переход пробивается, т.е. происходит короткое замыкание (состояние логического 0).

Рис. 5. запоминающие ячейки на основе диодного ЗЭ: а – на диодах шотки, б – на транзисторе.

В схеме ячейки на рис. 4, а в режиме считывания подается положительное напряжение на шину Х, а выходной сигнал снимается с нагрузки, включенной последовательно в шину Y. В режиме программирования(запись 0) на шину Х подается импульс более высокого напряжения, под действием которого пережигается перемычка и нарушается электрическое соединение между катодом диода и шиной Y. Обычно для пережигания нихромовых перемычек необходимо пропустить ток 50 – 100, а кремниевых - примерно 20 мА.

Вследствие того, что диод является пассивным элементом, для получения высокого быстродействия формирователи возбуждения выходных шин выборки строки должны иметь малое выходное сопротивление, т.к. в момент подачи напряжения на шину происходит зарядка паразитных емкостей матрицы входным током. Использование в качестве элементов развязки транзисторов, включенных по схеме с общим коллектором (рис. 4, б), позволяет существенно снизить ток выборки для шин Х, благодаря усилительным свойствам транзистора дешифратор при программировании может задавать в выбранную шину значительно меньший ток, чем необходимо для пережигания перемычек. Обычно запоминающие матрицы строят на основе n - p – n транзисторов, что позволяет достичь наивысшего быстродействия и наибольшей плотности упаковки на кристалле для биполярных транзисторов.

Ячейки памяти на основе диодного ЗЭ (рис. 5.) состоят из двух встречновключенных p – n переходов, при считывания состояния ЗЭ на шину Х подается положительное напряжение, а с нагрузки, подключенной к шине Y, снимается выходной сигнал. В исходном состоянии элемент хранит 0, а его сопротивление очень велико. Для записи 1 к встречновключенной паре p – n переходов прикладывается повышенное напряжение, при котором запертый переход пробивается и замыкается накоротко. Сравнительно перспективным считается выполнение ЗЭ на встречновключенных диодах Шотки (рис. 5, а), которые в настоящее время получают все большее распространение. В исходном

состоянии встречновключенные диоды не проводят ток (состояние логического 0),по при программировании вследствие пробоя происходит закорачивание обратно смещенного диода (состояние логической 1).

Встречно включенные переходы часто создаются на основе транзистора с отключенной базой (рис. 5,б). Эмиттер транзистора соединяются с разрядной шиной. В режиме программирования при подаче достаточного потенциала на эмиттер(при заземлении коллектора) происходит необратимый пробой эмиттерного перехода и транзистор превращается в диод, образованный переходом коллектор - база.

На основе рассмотренных эффектов запоминающих ячеек созданы микросхемы и блоки ППЗУ ёмкостью более 64 Кбит и временем выборки 15 – 100 нс со встроенными схемами обрамления.

У ППЗУ есть некоторый недостаток, который заключается в том, микросхемы невозможно подвергнуть полному контролю по записи на заводе изготовителе, поэтому процент выхода годных микросхем по результатам программирования составляет 50–70%.

3. КЭШ память.

КЭШ память располагают между основной памятью и процессором для улучшения эффективной скорости взаимодействия с памятью и увеличения быстродействия процессора. Обычно КЭШ память реализуют на полупроводниковых устройствах, быстродействие которых сравнимо с быстродействием процессора, тогда как основная память использует более дешёвые и медленно действующие устройства. Все данные хранятся в основной памяти. С помощью системы с КЭШ – памятью некоторые из этих данных копируются в неё. Когда процессору нужно считать или записать данные в память, то сначала он проверят их наличие в КЭШ – памяти. Если необходимые данные находятся там (КЭШ - попадание), то процессор может легко и быстро их использовать. В противном случае (КЭШ - промах) эти данные извлекаются из основной памяти и переписываются в КЭШ – память.

Для увеличения процента КЭШ 0 попаданий процессор использует блочную выборку. КЭШ – контроллер разбивает основную память на блоки (известные также как длина строки) длиной обычно в 2, 4, 8, или 16 байт. Размер блока является одним из наиболее важных параметров при проектировании системы с КЭШ – памятью. Если блок слишком мал, то уменьшается эффективность выборки из основной памяти и процент КЭШ – попаданий. Слишком большой блок уменьшает количество блоков, помещающихся в КЭШ – памяти.

Обычно 32 – разрядный процессор использует 2 или 4 слова на блок. В случае КЭШ – промаха КЭШ – контроллер пересылает весь, содержащий нужное слово, блок из основной памяти в КЭШ – память. Блочная выборка может принести данные, расположенные перед требуемым байтом (просмотр назад), расположенные после него (просмотр вперёд), или же как те, так и другие.

Работая с КЭШ – памятью, необходимо помнить, что одновременно могут существовать две копии одних и тех же данных: одна в КЭШ - , а другая в основной памяти. Если изменяется только одна из этих копий, то по одном и тому же адресу будет существовать два набора информации.

Регенерация информации в динамических ЗУ

Независимо от того, какова конкретная модификация динамической памяти, запоминающие конденсаторы ее запоминающих элементов разряжаются из-за наличия токов утечки. Постоянная разряда, как известно, зависит от емкости запоминающего конденсатора и сопротивления цепи тока утечки и может различаться для разных модификаций. Время, в течение которого информация сохраняется в элементе памяти, составляет до нескольких десятков миллисекунд.

Это приводит к необходимости периодического (с периодом не больше, чем время сохранения информации) восстановления зарядов емкостей. Такая процедура и получила название регенерации (refresh) динамической памяти. Выполняется она одновременно для целой строки матрицы (банка) элементов памяти, поскольку регенерировать информацию по элементам или по словам (по 8 байт) слишком долго.

Действительно, если даже считать, что регенерация выполняется одним длинным пакетным циклом, то для микросхем памяти PС2700, в которых на одну передачу данных приходится 3 нс (165 МГц × 2), при емкости 256 Мбит на поэлементную регенерацию всех элементов потребуется 3 × 10-9 × 228 = 0,8 с, а на регенерацию по словам, точнее, ячейкам, разрядность которых не может быть выше разрядности микросхемы (как правило, не более 16 бит), потребуется в 16 раз меньше времени, т.е. 50 мс. Учитывая, что для таких микросхем максимальный период регенерации TREF = 64 мс, поэлементная регенерация оказывается принципиально невозможной, а регенерация по словам будет занимать более 75 % времени работы памяти.

Количество же строк в одном банке в данной микросхеме составит 8192, а построчная регенерация в таком случае будет занимать всего 24,5 мкс или около 0,5 % времени.

Конечно, если ко всем строкам памяти за время, не превышающее TREF, были бы выполнены обращения, то обновлять информацию не было бы нужно, так как при обращении (не только записи, но и чтении) заряд на запоминающих емкостях полностью восстанавливается.

Распределить циклы регенерации строк по полному периоду регенерации можно различными способами. Рассмотренный выше вариант пакетной регенерации, при котором все циклы регенерации строк группируются в начале или в конце периода, хотя и может быть более экономичным по времени из-за отсутствия дополнительных переключений, не является достаточно удобным, так как блокирует работу памяти на относительно длительный интервал времени. Поэтому чаще применяют так называемую распределенную регенерацию (иногда используется термин “синхронная”), при которой циклы регенерации строк равномерно распределяются по периоду.

Длительность периода регенерации не обязательно устанавливается равной максимальному значению. Например, в ряде ПЭВМ для управления регенерацией часто используют сигналы одного из счетчиков (счетчик 1) системного таймера, на который поступают сигналы от кварцевого генератора (частотой 14.31818 МГц), установленного на системной плате. Этот счетчик вырабатывает импульсы примерно каждые 15 мкс, и эти импульсы могут использоваться для запуска регенерации. Однако для памяти большого объема такая частота оказывается недостаточной.

Возможны и более сложные схемы регенерации: пакетная с возможностью прерывания пакета или скрытая – во время свободных циклов памяти, если таковые имеются.

За последовательностью циклов регенерации строк следит контроллер памяти, который может организовывать очередь из этих циклов. Этот же контроллер может формировать адреса строк для регенерации, но часто эти адреса формируются внутренним счетчиком, имеющимся в самой микросхеме динамической памяти. Известна также квазистатическая память, в которой регенерация полностью контролируется внутренней логикой микросхемы и не требует никаких внешних сигналов.

Собственно циклы регенерации также могут различаться по порядку выполнения и запускающим их управляющим сигналам.

Наиболее распространенным вариантом является цикл, при котором изменяется порядок подачи адресных стробов. Если в обычном цикле чтения или записи сигнал строба адреса строки RAS# предшествует стробу адреса столбца CAS#, то рассматриваемый цикл регенерации запускается при одновременной подаче низких уровней обоих этих сигналов для синхронной памяти, а для асинхронной – спадающий фронт сигнала CAS# предшествует отрицательному фронту сигнала RAS#. Соответствующие временные диаграммы показаны на рис. 20. В обоих случаях этот способ регенерации называется CBR (CAS Before RAS), хотя в синхронной памяти он также называется командой автоматической регенерации (Auto Refresh Command).

Другим вариантом запуска регенерации является подача только одного сигнала RAS# без последующего CAS#. Такой вариант называется ROR (RAS Only Refresh), а адреса регенерируемых строк формируются контроллером памяти и подаются на адресные входы микросхемы

Стековая и кэш память

Организация ассоциативной и стековой памяти

Ассоциативные запоминающие устройства

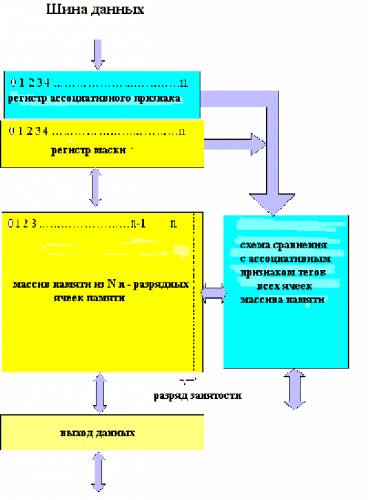

В ассоциативных запоминающих устройствах поиск информации производится по ассоциативному признаку, записанному в каждую ячейку памяти.

В регистр маски записывается слово, разрешающее запрос по всем или только некоторым разрядам ассоциативного признака, применение маски позволяет сократить или расширить область поиска.

Поиск информации производится параллельно по всем ячейкам путем сравнения запроса с ассоциативным признаком каждой ячейки.

Результат поиска формирует специальная комбинационная схема, вырабатывающая сигналы, оповещающие об отсутствии слов, удовлетворяющих условиям поиска, о наличии только одного слова, о наличии нескольких слов, имеющих такой ассоциативный признак.

После формирования и обработки оповещающих сигналов схемой управления производится считывание необходимой информации. При записи отыскивается свободная ячейка по значению разряда занятости, в первую найденную свободную ячейку записывается информация.

Проверка разряда занятости производится по установке n-го разряда (разряда занятости) маски. При использовании дополнительных комбинационных схем в ассоциативной памяти можно выполнять различные логические операции, определяя максимальное или минимальное число, количество слов, имеющих одинаковый ассоциативный признак и т.д. На рис.1 показана структура ассоциативной памяти. Ячейки памяти ассоциативного запоминающего устройства должны быть элементами статической памяти, в ассоциативной памяти обращение производится ко всем ячейкам одновременно и не должно прерываться циклами регенерации. Ассоциативная память наиболее быстродействующая, но очень дорогая, так как требует введения дополнительно схемы сравнения, позволяющей осуществить поиск, для каждой ячейки памяти. Поэтому такая память обычно не используется в чистом виде, а быстродействующие устройства памяти типа Кэш обычно выполняются как частично ассоциативные.

Рис.1. Организация ассоциативной памяти.

В микропроцессорах ассоциативная память (память с выборкой по содержанию ) используются в составе кэш-памяти для хранения адресной части команд и операндов исполняемой программы. При этом нет необходимости обращаться к ОЗУ за следующей командой или требуемым операндом, достаточно поместить в регистр ассоциативного признака необходимый адрес и, если искомая информация имеется в кэш памяти, то она сразу будет выдана. Обращение к оперативной памяти будет необходимо лишь при отсутствии требуемой информации в кэш. За счет такого использования кэш сокращается число обращений к ОЗУ, а это позволяет экономить время, так как обращение к кэш требует приблизительно в 10 раз меньше времени, чем обращение к ОЗУ.

Стековая память

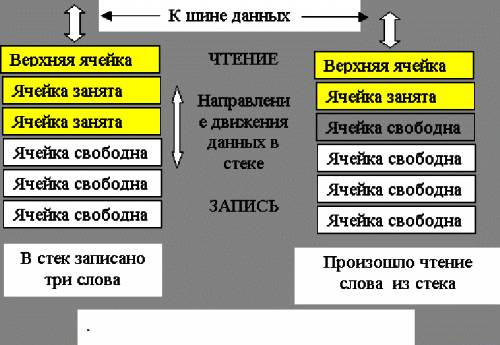

Рассмотрим организацию стековой памяти, как памяти, образованной из связанных между собой ячеек памяти, в которых информация при записи в стек нового слова смещается вниз (Рис.2). Обмен информацией осуществляется только через верхнюю ячейку памяти. При считывании слов из стека, слово может удаляться из стековой памяти или сдвигаться по кольцу, в зависимости от организации стека. Режим чтения –последним вошел, первым вышел- называютLIFO (Last In First Out).

Рис.2. Организация стековой памяти.

Аппаратная реализация такой памяти не всегда целесообразна и зачастую стековая память организуется в основной памяти компьютера программно, что позволяет изменять объем стека в зависимости от необходимости. При организации стека в основной памяти выделяется специальный адресный регистр –"указатель стека.”. В указателе стека находится адрес последнего записанного в стек слова. При записи слова в стек адрес вершины стека автоматически уменьшается, при чтении - автоматически увеличивается. Стековая память используется обычно для сохранения состояния текущей программы при обработке прерывания. После выполнения прерывающей программы состояние всех регистров, существовавшие в момент прерывания программы восстанавливается в последовательности, обратной последовательности записи. Можно сохранять в стеке и данные программы, это удобно тем, что при обращении к стеку не требуется указывать в программе адреса ячейки памяти, извлечение информации из стека так же происходит без указания адреса.

Дата: 2019-12-10, просмотров: 411.