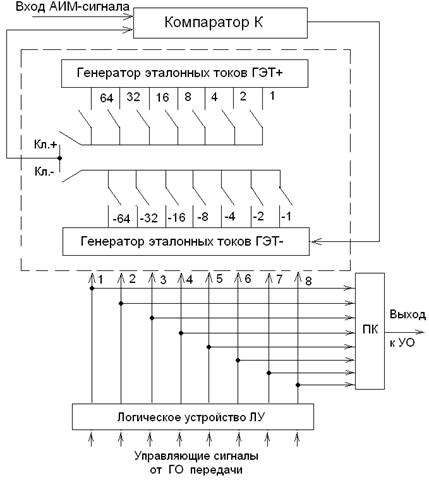

Кодирование осуществляется в два этапа:

1 этап – кодирование полярности. Результат кодирования записывается в первом разряде. Для этого в компаратор подается эталонный ток – 0 («земля»). Положительные значения кодируются символом «1», отрицательные – символ «0».

2 этап – кодирование амплитуды АИМ – сигнала. Результаты кодирования записываются в разряды 2…8. Для этого в компаратор последовательно подаются от большего к меньшему семь эталонных токов (64; 32; 16; 8; 4; 2; 1;).

Кодируемый отсчет подается на первый вход Вх.1 компаратора, цикл кодирования начинается с установки первого выхода ЛУ в состояние 1 или замыкания ключа Кл.1 Поскольку разность 105,3 - 64 >0, то в первом такте кодирования на выходе компаратора будет сформирован 0, состояние 1 выхода ЛУ сохранится и в состояние 1 переводится 2 выход ЛУ. В результате суммарное значение эталонных токов перед началом второго такта становится равным 96Δ. Несмотря на увеличение эталонного тока, неравенство IАИМ - IЭТ>0 сохраняется (105,3-96>0). Поэтому во втором такте на выходе компаратора опять будет сформирован 0, состояние 2 выхода ЛУ.

Рисунок 2- Структурная схема линейного кодера взвешивающего

типа для двухполярного сигнала

сохранится, а состояние 3 выхода ЛУ переводится в 1. В результате суммарное значение эталонных токов перед началом третьего такта становится равным 112 Δ. Это превышает значение амплитуды кодируемого отсчета, т.е. 105,3 - (64+32+16) < 0 и в третьем такте кодирования на выходе компаратора будет сформирована 1. При записи в ЛУ эта 1 изменит состояние 3 выхода с 1 на0, разомкнется ключ Кл.3 и отключит ток 16Δ, а выход 4 будет переведен в состояние 1 и т.д. Последовательность решений компаратора в процессе кодирования представлена комбинацией двоичных символов 0010110.

По окончании седьмого такта на выходе ЛУ будет сформирована комбинация 1101001, представляющая в параллельном 7-разрядном двоичном коде величину кодируемого отсчета -105,3Δ . Легко определить, что ошибка квантования в этом случае будет равна 0,3Δ. По мере формирования кодовой комбинации преобразователь кода преобразует ее в последовательность двоичных символов, представляющих собой выходной сигнал кодера. По окончании кодирования сигналы, поступающие от ГО, переводят узлы кодера в исходное состояние, подготавливая его к кодированию следующего отсчета.

Пример заполнения таблицы с результатами кодирования приведен в таблице 4.

Таблица 4

| Такты (раз-ряды) коди-рова-ния |

IЭТ |

IАИМ - IЭТ | Состоя-ние выхода компара- тора «0» или «1» | Выходы ЛУ | ||

| Состояние ключей ГЭТ «вкл» («выкл») | Запись решения | |||||

| 1 | 0 | -105,3 - 0 < 0 | 1 | Вкл Кл- | 0 | 1 этап |

| 2 | 64 | 105,3 - 64 >0 | 0 | Вкл | 1 | 2 – й этап

|

| 3 | 32 | 105,3 - (64+32) > 0 | 0 | Вкл | 1 | |

| 4 | 16 | 105,3 - (64+32+16) < 0 | 1 | Выкл | 0 | |

| 5 | 8 | 105,3 - (64+32+8) > 0 | 0 | Вкл | 1 | |

| 6 | 4 | 105,3 - (64+32+8+4) < 0 | 1 | Выкл | 0 | |

| 7 | 2 | 105,3 - (64+32+8+2) < 0 | 1 | Выкл | 0 | |

| 8 | 1 | 105,3 - (64+32+8+1) > 0 | 0 | Вкл | 1 | |

| SКВ = 105,3 (64+32+8+1) = 0,3 | ||||||

Задание №3

Осуществить процедуру декодирования сигналов в системе связи с ИКМ.

Порядок выполнения:

1. Вычертить схему декодера.

2. Изучить назначение отдельных узлов декодера.

3. Изучить принцип работы декодера.

4. Выполнить декодирование кодовой комбинации согласно варианту задания (исходные данные приведены в таблице 5).

Таблица 5

| Варианты | 1 | 2 | 3 | 4 | 5 |

| Кодовая комбинация | 01001111 | 10100111 | 10011011 | 01110101 | 10011101 |

| Варианты | 6 | 7 | 8 | 9 | 10 |

| Кодовая комбинация | 01010101 | 01001011 | 10110111 | 10101101 | 01011111 |

Методический материал и пример выполнения задания №3

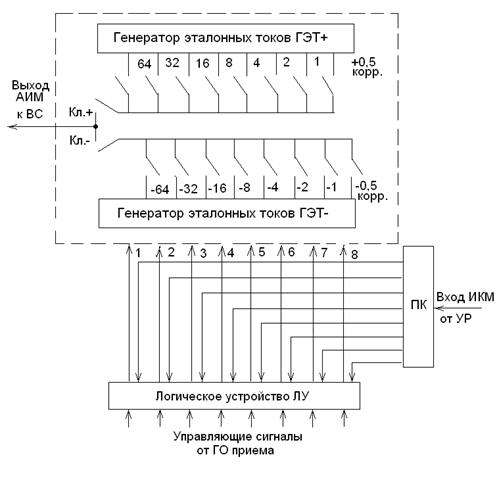

Структурная схема линейного декодера изображена на рисунке 3.

Рисунок 3 - Структурная схема линейного декодера

Преобразователь кода ПК – для преобразования последовательного кода в параллельный. В последовательном коде 8-разрядная кодовая комбинация из устройства разделения УР поступает в декодер, фиксируется на 1…8 выходах логического устройства в параллельном коде и хранится там до окончания операции декодирования.

Логическое устройство ЛУ – для управления замыканием ключей. Замыкаются ключи тех разрядов Кл. 1…Кл.7, где на выходе ЛУ имеется символ «1». Кроме того, замыкается Кл.8 – эталона коррекции.

Генераторы эталонных токов ГЭТ – для получения восьми эталонных токов (64D, 32D, 16D, 8D, 4D, 2D, 1D, 0,5D ) в ГЭТ «+» при декодировании положительных сигналов и восьми эталонных токов (-64D, -32D, -16D, -8D, -4D, -2D, -1D, -0,5D) в ГЭТ «-» при декодировании отрицательных сигналов. Восьмой эталонный ток, равный половине шага квантования D - является эталоном коррекции.

Генераторное оборудование ГО приема – для управления работой узлов декодера.

Дата: 2019-02-02, просмотров: 1010.