По результатам лабораторной работы оформить отчет, содержащий:

1. титульный лист;

2. цель работы;

3. электрическую принципиальную схему проведения лабораторной работы;

4. протокол информационного обмена и блок схему алгоритма решения поставленной задачи;

5. код программы с комментариями, реализующей поставленную задачу;

6. выводы.

4.4. Работа №4. Измерение основных электрических параметров аппаратуры систем управления с помощью AVR микроконтроллера.

Цель работы: изучение принципов измерения основных электрических параметров аппаратуры систем управления: статического сопротивления изоляции (Rиз.ст.), сопротивления нагрузки (Rнагр.), качества цепи заземления (Rкорп.) – на базе микроконтроллера ATmega32.

Функционирование модуля АЦП

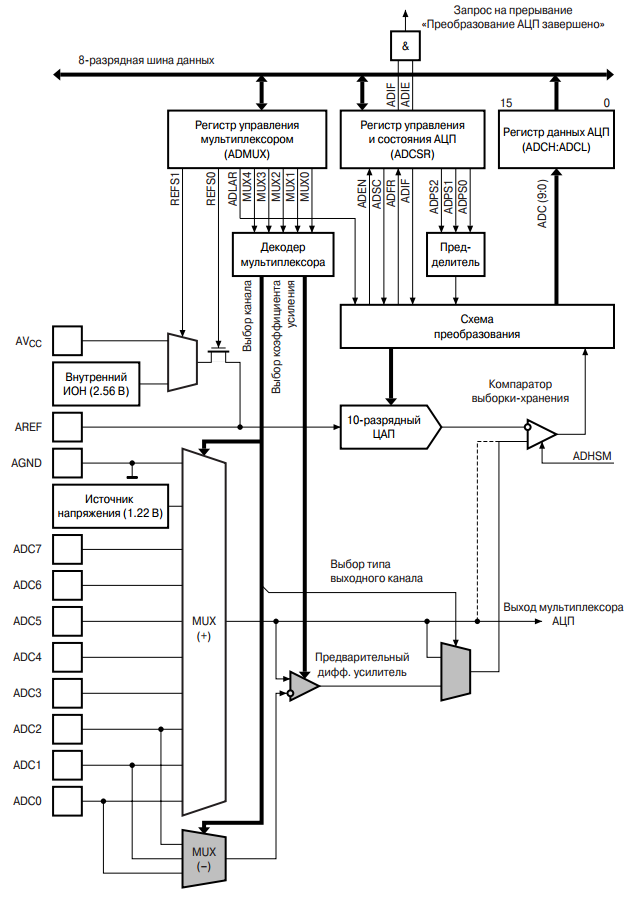

Структурная схема модуля АЦП МК ATmega32 приведена на рис. 4.22.

Рис. 4.22. Структурная схема модуля АЦП МК ATmega32

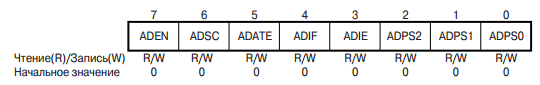

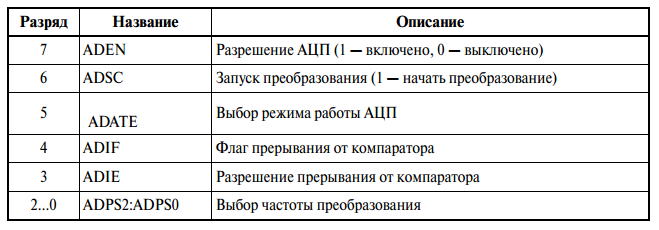

Формат регистров ADCSRA и ADMUX приведен на рис. 4.23 и 4.24, а краткое описание функций их разрядов представлено в таблицах 4.14 и 4.15, соответственно [2].

Рис. 4.23. Формат регистра ADCSRA

Таблица 4.14. Разряды регистра ADCSRA

Рис. 4.24. Формат регистра ADMUX

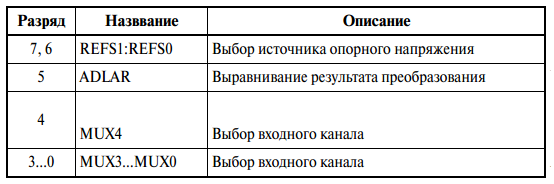

Таблица 4.15. Разряды регистра ADMUX

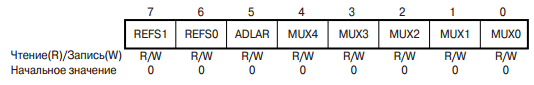

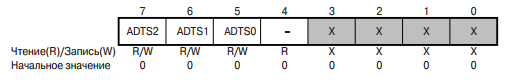

Формат регистра SFIOR приведен на рис. 4.25.

Рис. 4.25. Формат регистра SFIOR

Для разрешения работы АЦП необходимо записать лог. «1» в разряд ADEN регистра ADCSRA, а для выключения — лог. 0. Если АЦП будет выключено во время цикла преобразования, то преобразование завершено не будет (в регистре данных АЦП останется результат предыдущего преобразования).

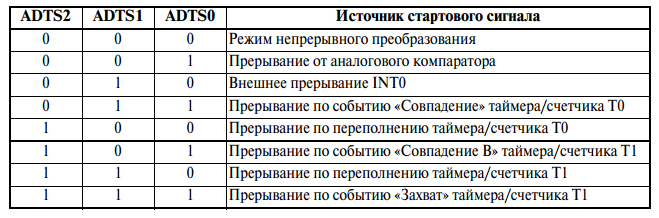

Запуск АЦП возможен не только по команде пользователя, но и по прерыванию от некоторых периферийных устройств, имеющихся в составе микроконтроллера. Для выбора режима работы в этих моделях используется разряд ADATE регистра ADCSRA и разряды ADTDS2…0 регистра SFIOR.

Если разряд ADATE сброшен в «0», АЦП работает в режиме одиночного преобразования. Если же разряд ADATE установлен в «1», функционирование АЦП определяется содержимым разрядов ADTS2…0 согласно в соответствии с таблицей 4.16.

Таблица 4.16. Источник сигнала для запуска преобразования

Запуск каждого преобразования в режиме одиночного преобразования, а также запуск первого преобразования в режиме непрерывного преобразования осуществляется установкой в «1» разряда ADSC регистра ADCSRA. Запуск преобразования по прерыванию осуществляется при установке в «1» флага выбранного прерывания. Разряд ADSC регистра ADCSRA при этом аппаратно устанавливается в «1». Запуск преобразования в этих режимах также может быть осуществлен установкой в «1» разряда ADSC регистра ADCSRA.

В режимах одиночного и непрерывного преобразований цикл преобразования начинается по первому нарастающему фронту тактового сигнала после установки разряда ADSC. Если используется запуск по прерыванию, то цикл преобразования начинается по первому нарастающему фронту тактового сигнала после установки флага выбранного прерывания. Причем при установке этого флага осуществляется сброс предделителя модуля АЦП. Тем самым обеспечивается фиксированная задержка между генерацией запроса на прерывание и началом цикла преобразования.

Длительность цикла составляет 13 тактов при использовании несимметричного входа и 13 либо 14 тактов при использовании дифференциального входа; выборка и запоминание входного сигнала осуществляется в течение первых 1,5 и 2,5 тактов соответственно. Через 13 (14) тактов преобразование завершается, разряд ADSC аппаратно сбрасывается в «0» (в режиме одиночного преобразования) и результат преобразования сохраняется в регистре данных АЦП. Одновременно устанавливается флаг прерывания ADIF регистра ADCSRA и генерируется запрос на прерывание. Как и флаги остальных прерываний, флаг ADIF сбрасывается аппаратно при запуске подпрограммы обработки прерывания от АЦП или программно, записью в него лог. «1». Разрешение прерывания осуществляется установкой в «1» разряда ADIE регистра ADCSRA при установленном флаге I регистра SREG.

Если АЦП работает в режиме непрерывного преобразования, новый цикл начнется сразу же после записи результата. В режиме одиночного преобразования новое преобразование может быть запущено сразу же после

сброса разряда ADSC (до сохранения результата текущего преобразования). Однако реально цикл преобразования начнется не ранее чем через один такт после окончания текущего преобразования.

При запуске первого преобразования после включения АЦП для выполнения преобразования потребуется 25 тактов, т. е. на 12 тактов больше, чем обычно. В течение этих 12 тактов выполняется «холостое» преобразование,

инициализирующее АЦП.

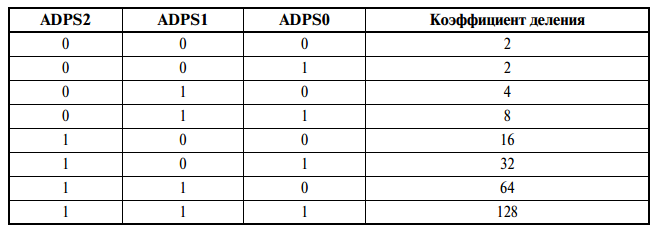

Для формирования тактовой частоты модуля АЦП в нем имеется отдельный предделитель. Коэффициент деления предделителя и, соответственно, длительность преобразования определяется состоянием разрядов ADPS2…ADPS0 регистра ADCSRA (см. таблицу 4.17).

Таблица 4.17. Задание коэффициента деления предделителя АЦП

Наибольшая точность преобразования достигается, если тактовая частота модуля АЦП находится в диапазоне 50…200 кГц. Соответственно коэффициент деления предделителя рекомендуется выбирать таким, чтобы тактовая частота модуля АЦП находилась в указанном диапазоне. Если же точности преобразования меньше 10 разрядов достаточно, можно использовать более высокую частоту, увеличивая тем самым частоту выборки.

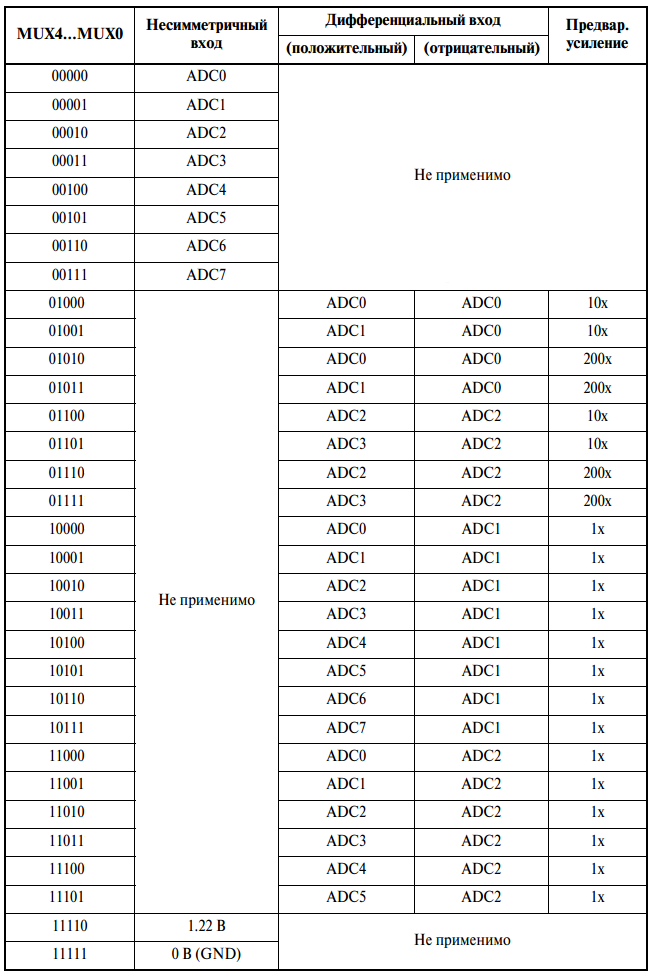

Выводы микроконтроллера, подключенные к входу АЦП, определяются состоянием разрядов MUX4…MUX0 регистра ADMUX в соответствии с таблицей 4.18.

Таблица 4.18. Управление входным мультиплексором АЦП

Следует отметить, что предварительный усилитель, используемый каналами с дифференциальным входом, имеет встроенную схему коррекции смещения. Оставшаяся после коррекции величина смещения может быть учтена программным способом. Для этого следует оба входа дифференциального усилителя подключить к одному и тому же выводу микроконтроллера, а затем вычитать полученное значение из результата последующих преобразований. Таким образом, ошибка смещения может быть

снижена до величины, меньшей 1 МЗР.

Состояние разрядов MUX2…MUX0 можно изменить в любой момент, однако, если это будет сделано во время цикла преобразования, смена канала произойдет только после завершения преобразования. Благодаря этому в режиме непрерывного преобразования можно легко осуществлять последовательное преобразование сигналов нескольких каналов.

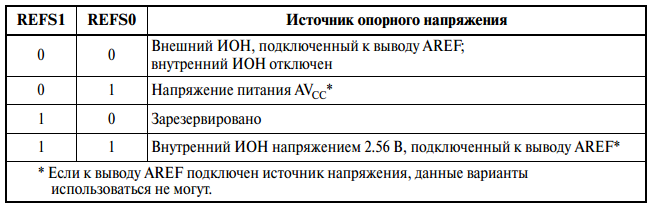

Модуль АЦП может использовать различные источники опорного напряжения (ИОН). Выбор конкретного источника опорного напряжения осуществляется с помощью разрядов REFS1:REFS0 регистра ADMUX в соответствии с таблицей 4.19.

Таблица 4.19. Выбор источника опорного напряжения АЦП

После завершения преобразования (при установке в «1» флага ADIF регистра ADCSRA) его результат сохраняется в регистре данных АЦП. Поскольку АЦП имеет 10 разрядов, этот регистр физически размещен в двух

регистрах ввода/вывода ADCH:ADCL, доступных только для чтения.

По умолчанию результат преобразования выравнивается вправо (старшие 6 разрядов регистра ADCH — незначащие). Однако он может выравниваться и влево (младшие 6 разрядов регистра ADCL — незначащие). Для управления выравниванием результата преобразования служит разряд ADLAR регистра ADMUX. Если этот разряд установлен в «1», результат преобразования выравнивается по левой границе 16-разрядного слова, если сброшен в «0» — по правой границе.

Обращение к регистрам ADCH и ADCL для получения результата преобразования должно выполняться в определенной последовательности: сначала необходимо прочитать регистр ADCL, а затем ADCH.

Для каналов с несимметричным входом результат преобразования определяется выражением ADC=1024*Vin/Vref, где Vin— значение входного

напряжения, а Vref— величина опорного напряжения.

Для каналов с дифференциальным входом результат преобразования определяется выражением ADC= 512*K*(Vpos–Vneg)/Vref, где Vpos – величина напряжения на положительном входе, Vneg – величина напряжения на отрицательном входе, а K— коэффициент усиления.

Результат преобразования представляется в этом случае в дополнительном коде, а его значение лежит в диапазоне $200 (–512)…$1FF (+512).

Дата: 2018-12-21, просмотров: 403.