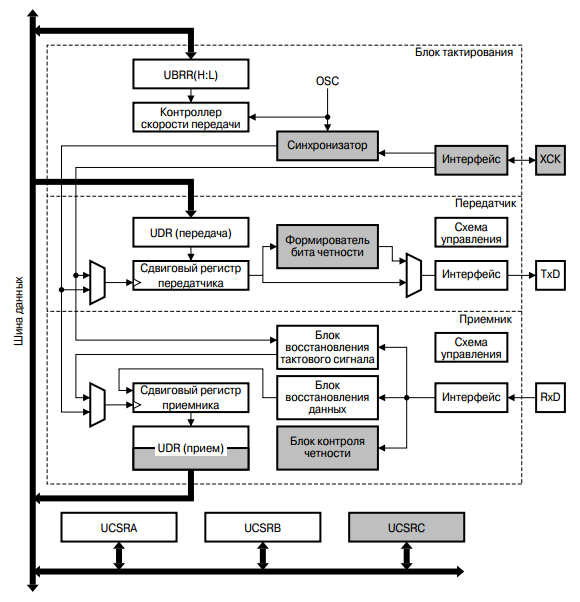

Упрощенная структурная схема модуля USART приведена на рис. 4.15.

Рис. 4.15. Структурная схема модуля USART

Модуль состоит из трех основных частей: блока тактирования, блока передатчика и блока приемника. Блок тактирования модулей USART включает в себя схему синхронизации, которая используется при работе в синхронном режиме и контроллер скорости передачи [2].

Блок передатчика включает одноуровневый буфер, сдвиговый регистр,

схему формирования бита четности и схему управления. Блок приемника, в свою очередь, включает схемы восстановления тактового сигнала и данных, схему контроля четности, двухуровневый буфер, сдвиговый регистр, а также схему управления.

Буферные регистры приемника и передатчика используют один адрес пространства ввода/вывода и обозначаются как регистр данных UDR (Universal Data Register). В этом регистре хранятся младшие 8 разрядов принимаемых и передаваемых данных. При чтении выполняется обращение к буферному регистру UDR приемника, при записи — к буферному регистру передатчика.

В модулях USART буфер приемника является двухуровневым (FIFO-буфер), изменение состояния которого происходит при любом обращении к регистру UDR. В связи с этим не следует использовать регистр UDR в качестве операндов команд типа «чтение/модификация/запись».

Для управления модулями USART используются три регистра: UCSRA, UCSRB и UCSRC.

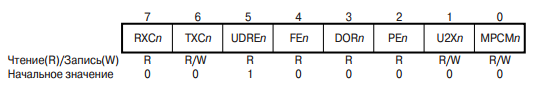

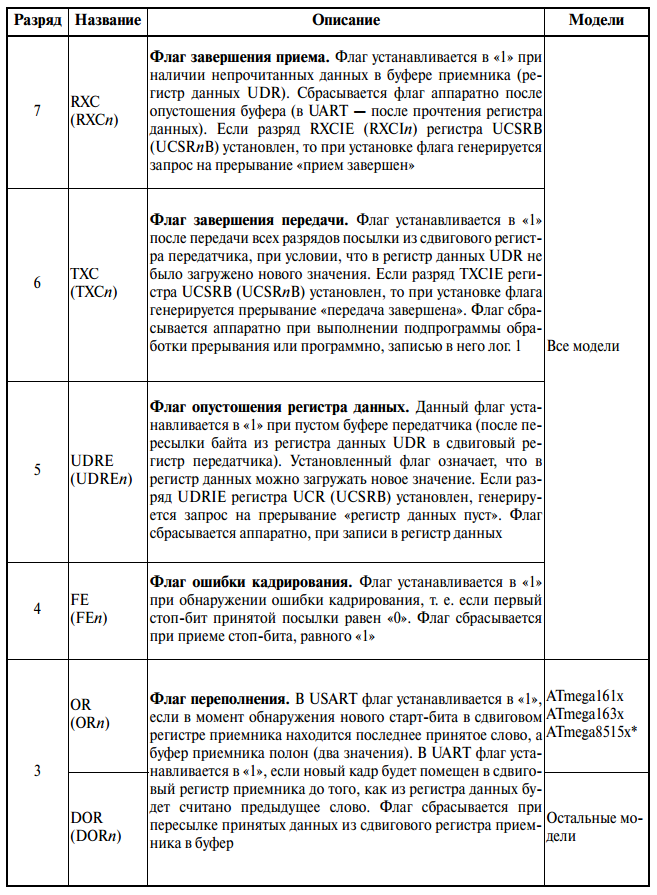

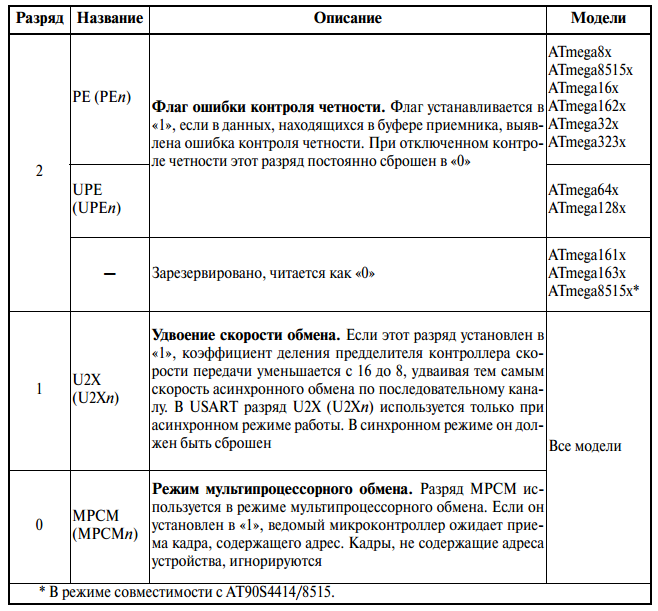

Формат регистров UCSRA, UCSRB и UCSRC приведен на рис. 4.16, 4.17, 4.18, а значение разрядов этих регистров описано в таблицах 4.9, 4.10, 4.11, соответственно.

Рис. 4.16. Формат регистра UCSRA

Таблица 4.9. Разряды регистра UCSRA

Продолжение таблицы 4.9

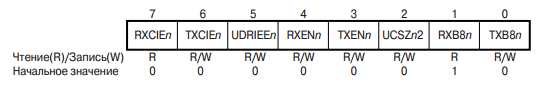

Рис. 4.17. Формат регистра UCSRB

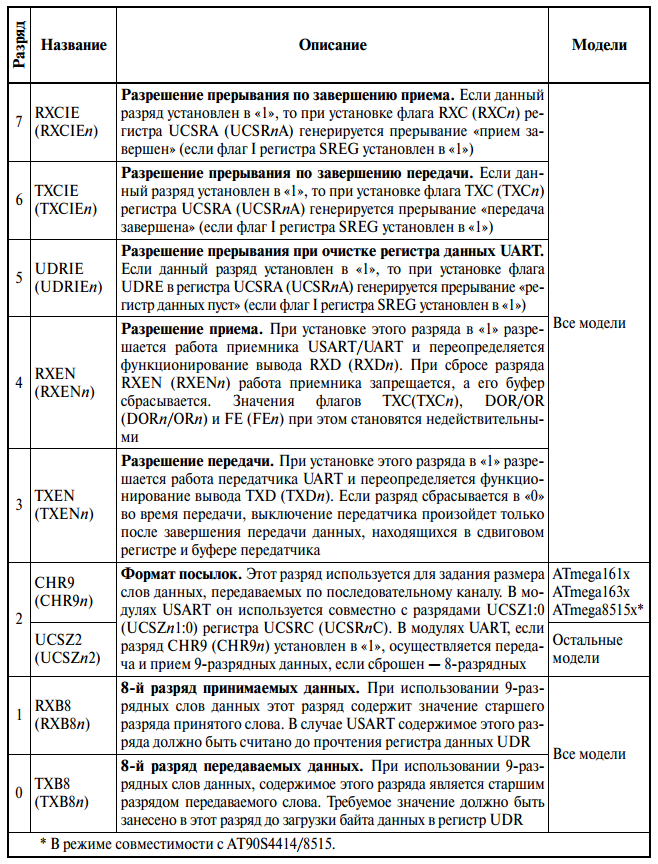

Таблица 4.10. Разряды регистра UCSRB

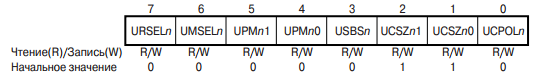

Рис. 4.18. Формат регистра UCSRC

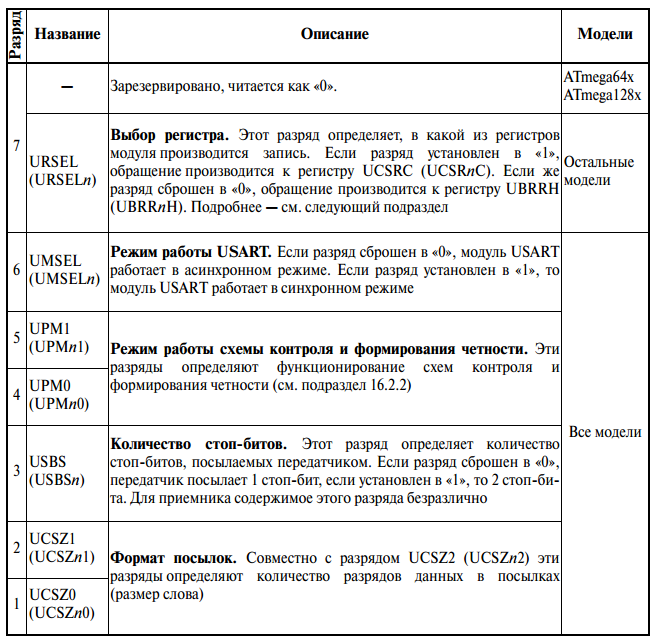

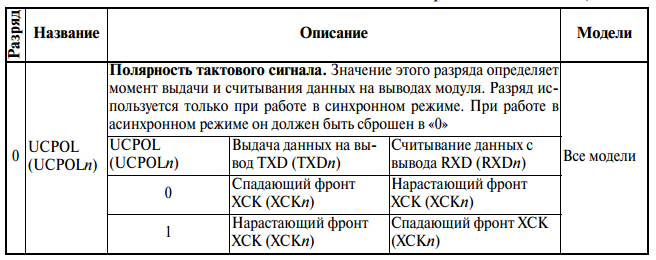

Таблица 4.11. Разряды регистра UCSRC

Продолжение таблицы 4.11

В асинхронном режиме, а также в синхронном режиме при работе в качестве ведущего, скорость приема и передачи данных задается контроллером скорости передачи, функционирующим как делитель системного тактового сигнала с программируемым коэффициентом деления. Коэффициент определяется содержимым регистра контроллера скорости передачи UBRR (см. рис. 4.15). В блок приемника сформированный сигнал поступает сразу, а в блок передатчика — через дополнительный делитель, коэффициент деления которого (2, 8 или 16) зависит от режима работы модуля USART.

Регистр UBRR является 12-разрядным и физически размещается в двух

регистрах ввода/вывода (UBRR:H и UBRR:L).

Регистр UBRRH размещается по тому же адресу, что и регистр управления UCSRC. Поэтому при обращении по этим адресам необходимо выполнить ряд действий для выбора конкретного регистра.

В частности, при записи регистр определяется состоянием старшего разряда записываемого значения URSEL. Если этот разряд сброшен в «0», изменяется содержимое регистра UBRR:H. Если же старший разряд значения установлен в «1», изменяется содержимое регистра управления UCSRC.

Для выбора регистра при чтении используется временная последовательность. При первом обращении по указанным адресам возвращается значение регистра UBRR:H. При повторном обращении по этим адресам в следующем машинном цикле возвращается значение регистра UCSRC.

При работе в асинхронном режиме скорость обмена определяется не только содержимым регистра UBRR, но и состоянием разряда U2X регистра UCSRA.

Если этот разряд установлен в «1», коэффициент деления предделителя уменьшается в два раза, а скорость обмена соответственно удваивается. При работе в синхронном режиме этот разряд должен быть сброшен.

Итак, скорость обмена определяется следующими формулами:

· асинхронный режим (обычный, U2Xn= «0»)

BAUD = fCK/16(UBRR + 1);

· асинхронный режим (ускоренный, U2Xn= «1»)

BAUD = fCK/8(UBRR + 1);

· синхронный режим ведущего

BAUD = fCK/2(UBRR + 1),

где

BAUD – скорость передачи в бодах,

fCK – тактовая частота микроконтроллера,

UBRR – содержимое регистра контроллера скорости передачи (0…4095).

При UBRR = 0 отклонение скорости обмена равно 0. Рекомендуется использовать значения регистра UBRR, при которых получаемая скорость передачи отличается от требуемого значения меньше чем на 0.5%. Значения, дающие большее отклонение также можно использовать, однако следует иметь в виду, что при этом снижается помехозащищенность линии передачи.

Формат кадра

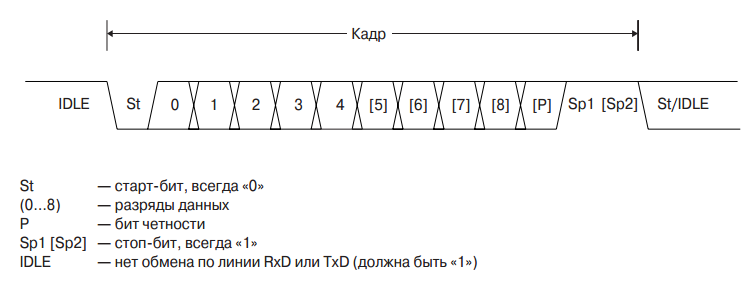

Под кадром в данном случае понимается совокупность одного слова данных и сопутствующей информации (рис. 4.19). Кадр начинается со старт-бита, за которым следует младший разряд слова данных. После старшего разряда слова данных следует один или два стоп-бита. Если включена схема формирования бита четности, он включается между старшим разрядом слова данных и первым стоп-битом.

Рис. 4.19. Формат кадра

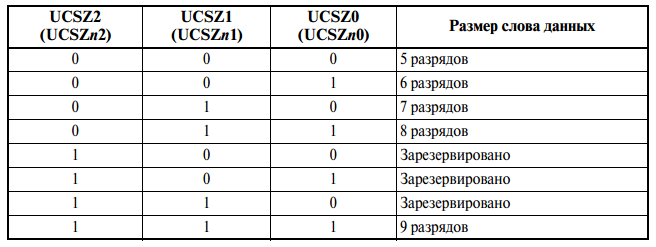

Формат кадра определяется несколькими разрядами регистров UCSRB и UCSRC. Размер слова данных в USART определяется разрядами UCSZ2…UCSZ0 в соответствии с таблицей 4.12.

Таблица 4.12. Определение размера слова данных в модуле USART

Выбор количества стоп-битов в модулях USART осуществляется с помощью разряда USBS регистра UCSRC. Если этот разряд сброшен в «0», блок передатчика формирует 1 стоп-бит в конце посылки. В противном случае, если разряд установлен в «1», блок передатчика формирует 2 стоп-бита.

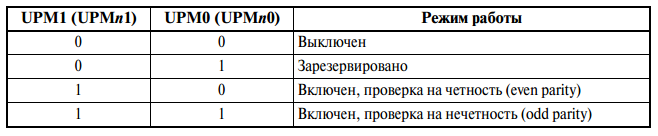

Разряды UPM1:UPM0 регистра UCSRС определяют функционирование схемы контроля четности модулей USART в соответствии с таблицей 4.13.

Таблица 4.13. Управление контролем четности

Значение бита четности получается путем выполнения операции «Исключающее ИЛИ» над всеми разрядами передаваемого слова данных. Если

используется проверка на нечетность (odd parity), полученный результат инвертируется.

Если контроль четности включен, бит четности вставляется передатчиком между старшим разрядом передаваемых данных и первым стоп-битом.

Передача данных

Работа передатчика разрешается установкой в «1» разряда TXEN регистра UCSRB. При установке разряда вывод TXD подключается к передатчику USART и начинает функционировать как выход независимо от установок регистров управления портом.

Передача инициируется записью передаваемых данных в буферный регистр передатчика — регистр данных UDR. После этого данные пересылаются из регистра UDR в сдвиговый регистр передатчика. Одновременно, если используются 9-разрядные данные, значение разряда TXB8 регистра UCSRB копируется в 9-й разряд сдвигового регистра.

При этом возможны два варианта:

· запись в регистр UDR осуществляется в тот момент, когда передатчик находится в состоянии ожидания (предыдущие данные уже переданы). В этом случае данные пересылаются в сдвиговый регистр сразу же после записи в регистр UDR;

· запись в регистр UDR осуществляется во время передачи. В этом случае данные пересылаются в сдвиговый регистр после передачи последнего стоп-бита текущего кадра.

9-й разряд данных должен быть загружен в разряд TXB8 до записи младшего байта слова в регистр данных.

После пересылки слова данных в сдвиговый регистр, флаг UDRE регистра UCSRA устанавливается в «1», что означает готовность передатчика к получению нового слова данных. В этом состоянии флаг остается до следующей записи в буфер. Одновременно с пересылкой в регистре формируется служебная информация — старт-бит, возможный бит четности, а также один или два стоп-бита.

После загрузки сдвигового регистра его содержимое начинает сдвигаться

вправо и поступать на вывод TXD. Скорость сдвига определяется настройками контроллера тактовых сигналов.

Если во время передачи в регистр UDR было записано новое слово данных, то после передачи последнего стоп-бита оно пересылается в сдвиговый регистр. Если же к моменту окончания передачи кадра такой записи выполнено не было, устанавливается флаг прерывания «Передача завершена» TXC регистра UCSRA. Сброс флага осуществляется аппаратно при входе в подпрограмму обработки соответствующего прерывания или программно, записью в этот разряд лог «1».

Выключение передатчика осуществляется сбросом разряда TXEN регистра UCSRB. Если в момент выполнения этой команды осуществлялась передача, сброс разряда произойдет только после завершения текущей и отложенной передач, т.е. после очистки сдвигового и буферного регистров передатчика. При выключенном передатчике вывод TXD может использоваться как контакт ввода/вывода общего назначения.

Прием данных

Работа приемника разрешается установкой разряда RXEN регистра UCSRB. При установке разряда вывод RXD подключается к приемнику USART и начинает функционировать как вход независимо от установок регистров управления портом.

Прием данных начинается сразу же после обнаружения приемником корректного старт-бита. Каждый разряд содержимого кадра затем считывается с частотой, определяемой установками контроллера скорости передачи. Считанные разряды данных последовательно помещаются в сдвиговый регистр приемника до обнаружения первого стоп-бита кадра. После этого содержимое сдвигового регистра пересылается в буфер приемника, из которого принятое значение может быть получено путем чтения регистра данных модуля. При использовании 9-разрядных слов данных значение старшего разряда может быть определено по состоянию флага RX8 регистра UCSRB. Причем содержимое старшего разряда данных должно быть считано до обращения к регистру данных. Это связано с тем, что флаг RX8 отображает значение старшего разряда слова данных кадра, находящегося на верхнем уровне буфера приемника, состояние которого при чтении регистра данных изменится.

Если во время приема кадра была включена схема контроля четности, она вычисляет бит четности для всех разрядов принятого слова данных и сравнивает его с принятым битом четности. Результат проверки запоминается в буфере приемника вместе с принятым словом данных и стоп-битами. Наличие или отсутствие ошибки контроля четности может быть определено по состоянию флага UPE. Этот флаг устанавливается в «1», если следующее слово, которое может быть прочитано из буфера, имеет ошибку контроля четности. При выключенном контроле четности флаг UPE всегда читается как «0».

Блок приемника модуля USART имеет еще два флага, показывающих состояние обмена: флаг ошибки кадрирования FE и флаг переполнения DOR. Флаг FE устанавливается в «1», если значение первого стоп-бита принятого кадра не соответствует требуемому, т.е. равно «0».

Флаг DOR индицирует потерю данных из-за переполнения буфера приемника. Флаг устанавливается в «1» в случае приема старт-бита нового кадра при заполненных буфере и сдвиговом регистре приемника. Установленный флаг DOR означает, что между прошлым байтом, считанным из регистра UDR, и байтом, считанным в данный момент, произошла потеря одного или нескольких кадров.

В модулях USART все флаги ошибок буферизуются вместе со словом данных, т. е. соответствующие разряды регистра UCSRA относятся к кадру, слово данных которого будет прочитано при следующем обращении к регистру данных UDR. Поэтому состояние этих флагов должно быть считано перед обращением к регистру данных. Кроме того, для совместимости с будущими устройствами рекомендуется при записи в регистр UCSRA сбрасывать соответствующие этим флагам разряды записываемого значения в «0».

Для индикации состояния приемника в модуле USART используется флаг прерывания «Прием завершен» RXC регистра UCSRA. Этот флаг устанавливается в «1» при наличии в буфере приемника непрочитанных данных. Этот флаг сбрасывается при опустошении буфера (после считывания всех находящихся в нем данных).

Выключение приемника осуществляется сбросом разряда RXEN регистра UCSRB. В отличие от передатчика приемник выключается сразу же после сброса разряда, т.е. кадр, принимаемый в этот момент, теряется. Кроме того, при выключении приемника очищается его буфер, т.е. теряются также все непрочитанные данные. При выключенном приемнике вывод RXD может использоваться как контакт ввода/вывода общего назначения.

Старт-бит нового кадра может передаваться сразу же после последней выборки, используемой для определения значения разряда.

Порядок выполнения работы

1. Собрать схему стенда УМС-1 в соответствии с рисунком 3.1.

2. Разработать протокол информационного обмена Модуля МК с Блоком системным по последовательному интерфейсу RS-232 в составе УМС-1 в соответствии с вариантом задания (см. подраздел 4.3.6).

Функциональная схема подключения МК к COM-порту Блока системного приведена на рис.4.20.

Структура информационного обмена приведена на рис. 4.21.

Рис. 4.20. Подключение МК к COM-порту

Рис. 4.21. Структура информационного обмена

3. Включить Персональный компьютер.

4. Включить Источник питания.

5. Включить Модуль МК.

6. В соответствии с разделом 2 в ИСР CodeVisionAVR на базе проекта Lab_03 написать программу, реализующую обмен по требуемому протоколу (см. п.2), и скомпилировать ее.

7. Загрузить полученную прошивку в микроконтроллер УМС-1, как показано в разделе 3.

8. Запротоколировать полученные результаты.

9. Выключить Модуль МК.

10. Выключить Источник питания.

11. Завершить работу Персонального компьютера.

Варианты заданий

| Вариант | ||

Настройки модуля USART

Размер слова данных: 8 бит

Стоп-бит: 1

1) Управляющий пакет содержит 1 слово данных.

Управляющий пакет формируется Блоком системным с использованием терминала среды разработки и отладки ПО CodeVisionAVR (см. раздел 2).

Модуль МК должен обеспечивать прием и обработку управляющего пакета, а также вывод его на ЖК-индикатор.

2) Информационный пакет должен формироваться Модулем МК без задержки в ответ на принятый управляющий пакет.

Информационный пакет должен содержать 3 слова данных:

1 слово данных – текущее число (например: 0x01);

2 слово данных – текущий месяц (например: 0х01);

3 слово данных – текущий год (например: 0x0F).

Прием информационного пакета осуществляется Блоком системным с использованием терминала среды разработки и отладки ПО CodeVisionAVR (см. раздел 2).

Кадры, составляющие информационный пакет, должны выдаваться Модулем МК подряд без задержки.

Дата: 2018-12-21, просмотров: 580.