МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ

УЧРЕЖДЕНИЕ ВЫСШЕГО ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ

МОСКОВСКИЙ АВИАЦИОННЫЙ ИНСТИТУТ

(НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ УНИВЕРСИТЕТ)

«МАИ»

Кафедра 314Б

А.В. Вилесов, Е.И. Гуревич, В.И. Саусин

УЧЕБНОЕ ПОСОБИЕ

по курсу

«Программные и аппаратные средства систем управления и автоматизированного контроля летательными аппаратами»

Зав. кафедрой 314Б

В.М. Медведев

Москва

2015

ОГЛАВЛЕНИЕ

1. Общие сведения о микроконтроллерахAVR.. 3

2. Интегрированная среда разработки CodeVisionAVR. Разработка и компиляция программы. 6

3. Загрузка программы в микроконтроллер ATmega32 УМС-1. Работа с программным обеспечением PonyProg2000. 13

4. Лабораторный практикум. 17

4.1. Работа №1. AVR микроконтроллер в разработках технических систем. 17

4.2. Работа №2. Изучение последовательного периферийного интерфейса SPI МК AVR и вывод информации на ЖК-дисплей. 29

4.3. Работа №3. Разработка протокола информационного обмена AVR МК по последовательному интерфейсу RS-232. 45

4.4. Работа №4. Измерение основных электрических параметров аппаратуры систем управления с помощью AVR микроконтроллера. 63

4.5. Работа №5. Измерение токов и напряжений с помощью AVR микроконтроллера и датчиков на основе эффекта Холла. 77

5. Литература. 85

Общие сведения о микроконтроллерахAVR

Однокристальные микроконтроллеры (МК) – отдельный класс микропроцессорных систем.

Микроконтроллер включает в себя ЦП, ОЗУ, ПЗУ, тактовый генератор, порты ввода/вывода, таймеры-счётчики, преобразователи АЦП, интерфейсы обмена (SPI, UART).

В связи с ростом технологических возможностей производства и, как следствие, возможности расширения периферии, микроконтроллер (МК) вытеснил в разработках ранее использовавшиеся однокристальные микро-ЭВМ.

Лабораторный практикум

4.1. Работа №1. AVR микроконтроллер в разработках технических систем.

Цель работы: изучение архитектуры и системы команд микроконтроллера (МК) ATmega32 и приобретение навыков работы в интегрированной среде разработки программного обеспечения CodeVisionAVR.

Микроконтроллеры AVR семейства Mega являются 8-разрядными микроконтроллерами, предназначенными для встраиваемых приложений. Они изготавливаются по малопотребляющей КМОП-технологии, которая в сочетании с усовершенствованной RISC-архитектурой позволяет достичь наилучшего соотношения быстродействие/энергопотребление. Рассматриваемые микроконтроллеры являются наиболее развитыми представителями микроконтроллеров AVR.

Основы языка Си

Для выполнения лабораторной работы №1 необходимо ознакомиться со следующими пунктами главы 3 [3]:

- вводные понятия;

- структура программы на Си;

- типы данных, переменные, константы;

- операторы ветвления;

- циклические конструкции;

- директивы препроцессора.

Порядок выполнения работы

1. Собрать схему стенда УМС-1 в соответствии с рис. 3.1.

2. Включить Персональный компьютер.

3. Включить Источник питания.

4. Включить Модуль МК.

5. В соответствии с разделом 2 в ИСР CodeVisionAVR на базе проекта Lab_01 написать программу, зажигающую светодиодный индикатор «PC4».

Функциональная схема подключения светодиодного индикатора «PC4», звукоизлучателя HA1 и кнопок «Кн.1», «Кн.2» в УМС-1 приведена на рисунке 4.3.

Рис. 4.3.

6. На основе п.5 написать программу мигания светодиодного индикатора «PC4».

7. На основе п.6 написать программу мигания светодиодного индикатора «PИ0» при нажатии кнопки «Кн.1».

8. Разработать алгоритм управления светодиодным индикатором «PC4» и звуковым сигналом в зависимости от сочетания нажатий кнопок «Кн.1», «Кн.2» в соответствии с вариантом задания (см. подраздел 4.1.4).

9. Написать программу, реализующую требуемый алгоритм (см. п.8), и скомпилировать ее.

Необходимые функции:

delay_us(x) – функция, реализующая задержку на x мкс

delay_ms(x) - функция, реализующая задержку на x мс

10. Загрузить полученную прошивку в микроконтроллер УМС-1, как показано в разделе 3.

11. Запротоколировать полученные результаты.

12. Выключить Модуль МК.

13. Выключить Источник питания.

14. Завершить работу Персонального компьютера.

Варианты заданий управления светодиодным индикатором и звуковым сигналом в зависимости от сочетания нажатий кнопок

| Вариант | Сочетание кнопок | Характеристики светодиодной индикации (« PC 4») (рис. 4.4) | Характеристики звукового сигнала ( PB 1) (Рис. 4.5) |

| 1 | КН1 | tсв = 0,5 с. tвыкл = 1 с. | - |

| КН2 | tсв = 1 с. tвыкл = 0,5 с. | tзв = 1 с. fзв = 4 кГц | |

| 2 | КН2 | tсв = 2 с. tвыкл = 1 с. | - |

| КН1 | tсв = 1 с. tвыкл = 2 с. | tзв = 1 с. fзв = 6 кГц | |

| 3 | КН1 + КН2 | tсв = 3 с. tвыкл = 1 с. | - |

| КН2 | tсв = 1 с. tвыкл = 3 с. | tзв = 1 с. fзв = 8 кГц | |

| 4 | КН1 + КН2 | tсв = 4 с. tвыкл = 1 с. | - |

| КН1 | tсв = 1 с. tвыкл = 4 с. | tзв = 1 с. fзв = 10 кГц | |

| 5 | КН1 | tсв = 5 с. tвыкл = 1 с. | tзв = 1 с. fзв = 12 кГц |

| КН1 + КН2 | tсв = 1 с. tвыкл = 5 с. | - |

Рис. 4.4. Временная диаграмма светодиодной индикации («PC4»)

Рис. 4.5. Пример временной диаграммы звукового сигнала (PB1), f = 1кГц

Функционирование модуля SPI

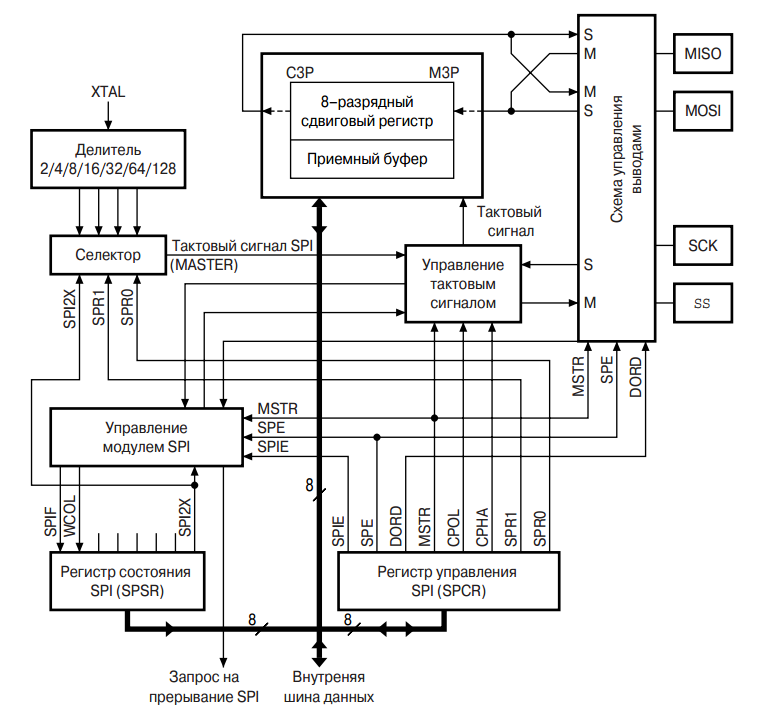

Модуль SPI использует четыре вывода микроконтроллера. Как и для большинства прочих периферийных устройств, эти выводы являются линиями портов ввода/вывода общего назначения [2]. Структурная схема модуля SPI приведена на рис. 4.6.

Рис. 4.6. Структурная схема модуля SPI

В микроконтроллере ATmega32 выводы, используемые модулем SPI, приведены в таблице 4.2.

Таблица 4.2. Выводы, используемые МК ATmega32

| Сигнал | Вывод | Назначение |

| SCK | PB7 | Выход (master)/вход (slave) тактового сигнала |

| MISO | PB6 | Вход (master)/выход (slave) данных |

| MOSI | PB5 | Выход (master)/вход (slave) данных |

| SS | PB4 | Выбор ведомого устройства |

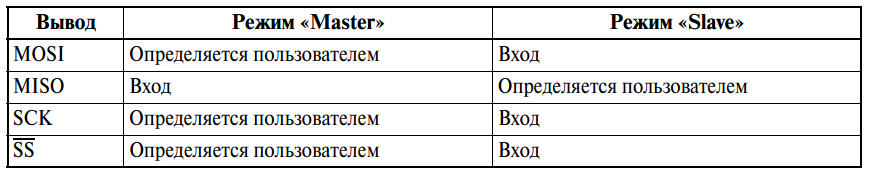

При включенном модуле SPI режим работы указанных выводов (направление передачи данных) переопределяется согласно таблице 4.3. Направление передачи данных определяется состоянием соответствующего разряда регистра DDRB.

Таблица 4.3. Переназначение режима работы выводов модуля SPI

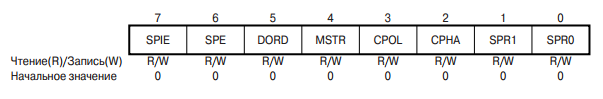

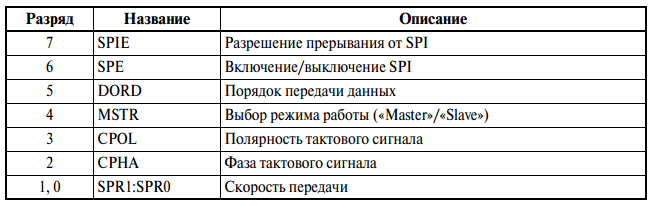

Для управления модулем SPI предназначен регистр управления SPCR. Формат этого регистра приведен на рис. 4.7, а краткое описание функций разрядов регистра приведено в таблице 4.4.

Рис. 4.7. Формат регистра SPCR

Таблица 4.4. Разряды регистра SPCR

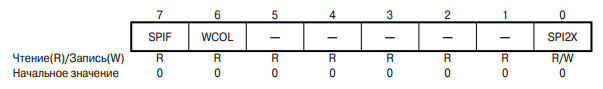

Контроль состояния модуля, а также дополнительное управление скоростью обмена осуществляется с помощью регистра состояния SPSR. Формат этого регистра приведен на рис. 4.8, а назначение его разрядов описано в таблице 4.5.

Рис. 4.8. Формат регистра SPSR

Таблица 4.5. Разряды регистра SPSR

Передаваемые данные записываются, а принимаемые — считываются из

регистра данных SPDR. Запись в этот регистр инициирует начало передачи, а при его чтении считывается содержимое буфера сдвигового регистра. Другими словами, регистр данных служит буфером между регистровым файлом микроконтроллера и сдвиговым регистром модуля SPI.

Соединение двух микроконтроллеров (ведущий—ведомый) по интерфейсу SPI показано на рис. 4.9. Вывод SCK ведущего микроконтроллера является выходом тактового сигнала, а ведомого микроконтроллера — входом.

Рис. 4.9. Соединение микроконтроллеров по интерфейсу SPI

Перед выполнением обмена необходимо разрешить работу модуля SPI. Для этого следует установить в «1» разряд SPE регистра SPCR. Режим работы определяется состоянием разряда MSTR этого регистра: если разряд установлен в «1», микроконтроллер работает в режиме «Master», если сброшен в «0» — в режиме «Slave».

Передача данных осуществляется следующим образом. При записи в регистр данных SPI ведущего микроконтроллера запускается генератор тактового сигнала модуля SPI и данные начинают поразрядно выдаваться на вывод MOSI и, соответственно, поступать на вывод MOSI ведомого микроконтроллера. Порядок передачи разрядов данных определяется состоянием разряда DORD регистра SPCR. Если разряд установлен в «1», первым передается младший разряд байта, если же сброшен в «0» — старший

разряд. После выдачи последнего разряда текущего байта генератор тактового сигнала останавливается с одновременной установкой в «1» флага «Конец передачи» (SPIF). Если прерывания от модуля SPI разрешены (флаг SPIE регистра SPCR установлен в «1»), генерируется запрос на прерывание. После этого ведущий микроконтроллер может начать передачу следующего байта либо, подав на вход SS ведомого микроконтроллера напряжение ВЫСОКОГО уровня, перевести последний в состояние ожидания.

Одновременно с передачей данных от ведущего к ведомому происходит

передача и в обратном направлении при условии, что на входе SS ведомого присутствует напряжение НИЗКОГО уровня. Таким образом, в каждом цикле сдвига происходит обмен данными между устройствами. Аналогично в конце каждого цикла флаг SPIF устанавливается в «1» как в ведущем микроконтроллере, так и в ведомом. Принятые байты сохраняются в приемных

буферах для дальнейшего использования.

В модуле реализована одинарная буферизация при передаче и двойная при приеме. Это означает, что готовый для передачи байт данных не может быть записан в регистр данных SPI до окончания предыдущего цикла обмена. При попытке изменить содержимое регистра данных во время передачи устанавливается в «1» флаг WCOL регистра SPSR. Сбрасывается этот флаг после чтения регистра SPSR с последующим обращением к регистру данных SPI.

Соответственно, при приеме данных принятый байт должен быть прочитан из регистра данных SPI до того, как в сдвиговый регистр поступит последний разряд следующего байта. В противном случае первый байт будет потерян.

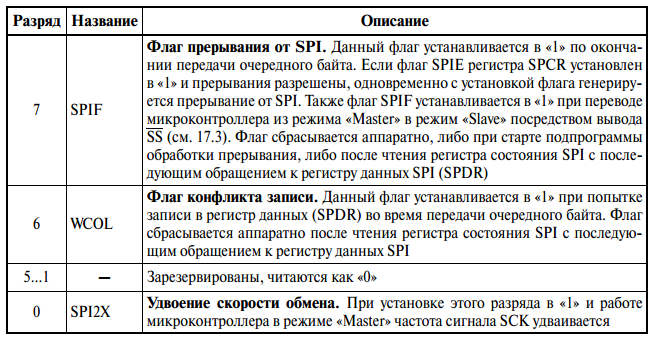

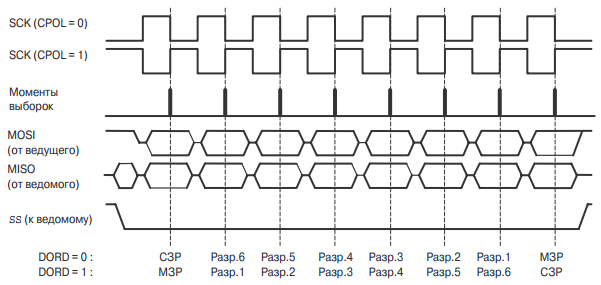

Спецификация интерфейса SPI предусматривает 4 режима передачи данных. Эти режимы различаются соответствием между фазой (момент считывания сигнала) тактового сигнала SCK, его полярностью и передаваемыми данными. Всего существует 4 таких комбинации, определяемых состоянием разрядов CPHA и CPOL регистра SPCR (см. таблицу 4.6).

Таблица 4.6. Задание режима передачи данных

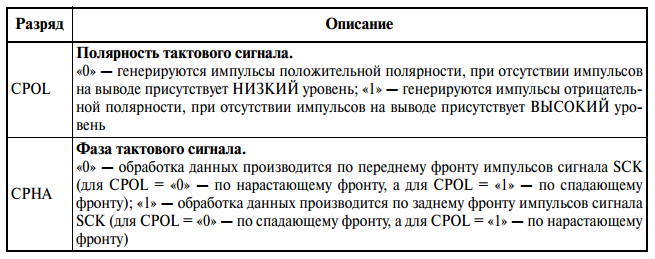

Соответствующие этим режимам форматы обмена данными через SPI приведены на рис. 4.10 и рис. 4.11 (передача ведется от старшего разряда

к младшему).

Рис. 4.10. Передача данных при CPHA = «0»

Рис. 4.11. Передача данных при CPHA = «1»

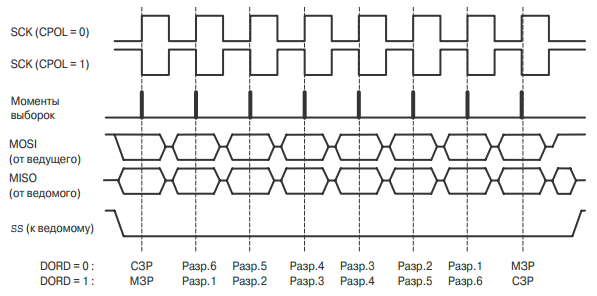

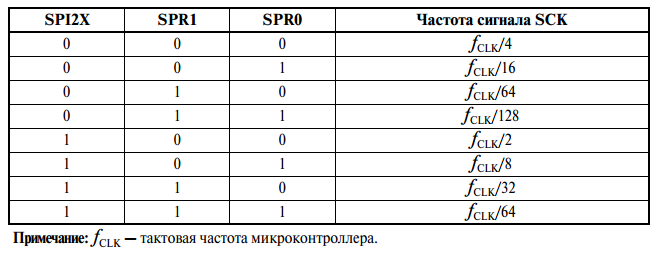

Частота тактового сигнала SCK и, соответственно, скорость передачи данных по интерфейсу определяется состоянием разрядов SPR1:SPR0 регистра SPCR и разряда SPI2X регистра SPSR ведущего микроконтроллера (см. таблицу 4.7).

Таблица 4.7. Задание частоты тактового сигнала SCK

Примечание: Функционирование микроконтроллера в режиме «Slave» гарантируется только на частотах, меньших или равных fCLK/4.

Вывод SS предназначен для выбора активного ведомого устройства и в режиме «Slave» всегда является входом. При подаче на него напряжения НИЗКОГО уровня модуль SPI активируется и вывод MOSI переключается в режим вывода данных (если это задано пользователем). Остальные выводы модуля SPI являются в этом режиме входами. А при подаче на вывод SS напряжения ВЫСОКОГО уровня все выводы модуля SPI переключаются в режим ввода данных. При этом модуль переходит в неактивное состояние и прием данных не производится. Как правило, в этом состоянии программа изменяет содержимое регистра данных.

Следует помнить, что каждый раз, когда на вывод SS подается напряжение ВЫСОКОГО уровня, происходит сброс модуля SPI. Соответственно, если изменение состояния этого вывода произойдет во время передачи данных – обмен прекратится, а передаваемый и принимаемый байты будут потеряны.

Если же микроконтроллер находится в режиме «Master» (разряд MSTR

регистра SPCR установлен в «1»), направление передачи данных через вывод

SS определяется пользователем. Если вывод сконфигурирован как выход, он работает как линия вывода общего назначения и не влияет на работу модуля SPI. В этом случае он используется для управления выводом SS микроконтроллера, работающего в режиме «Slave».

Если же вывод сконфигурирован как вход, то для обеспечения нормальной работы модуля SPI на него должно быть подано напряжение ВЫСОКОГО уровня. Подача на этот вход напряжения НИЗКОГО уровня от какой-либо внешней схемы будет воспринята модулем SPI как выбор данного микроконтроллера в качестве ведомого, и соответственно, начало передачи ему данных. Во избежание конфликта на шине – модуль SPI в таких случаях выполняет следующие действия:

1. Флаг MSTR регистра SPCR сбрасывается, и микроконтроллер переключается в режим «Slave». Как следствие, выводы MOSI и SCK начинают функционировать как входы.

2. Устанавливается флаг SPIF регистра SPSR, генерируя запрос на прерывание от SPI. Если прерывания от SPI разрешены и флаг I регистра SREG установлен в «1», происходит запуск подпрограммы обработки прерывания.

Таким образом, если ведущий микроконтроллер использует передачу данных, управляемую прерыванием и существует вероятность подачи на вход SS напряжения НИЗКОГО уровня, в подпрограмме обработки прерывания от SPI обязательно должна осуществляться проверка состояния флага MSTR. При обнаружении сброса этого флага он должен быть программно установлен обратно в «1» для обратного перевода микроконтроллера в режим «Master».

На рис. 4.12. и 4.13 рассмотрены регистры для управления модулем последовательного периферийного интерфейса SPI.

Рис. 4.12. Регистр управления SPI

Рис. 4.13. Регистр состояния (сверху), регистр данных (снизу) SPI

Таблица 4.7. Задание частоты тактового сигнала SCK

Основы языка Си

Для выполнения лабораторной работы №2 необходимо ознакомиться со следующими пунктами главы 3 [3]:

- функции;

- указатели и адреса переменных;

- массивы и строки;

- стандартные функции ввода вывода.

Порядок выполнения работы

1. Собрать схему стенда УМС-1 в соответствии с рисунком 3.1.

2. Разработать алгоритмы инициализации модуля SPI микроконтроллера и вывода информации на ЖК-индикатор в соответствии с вариантом задания (см. подраздел 4.2.5).

Функциональная схема подключения ЖКИ в УМС-1 приведена на рис.4.14.

Рис. 4.14. Функциональная схема подключения ЖКИ

3. Включить Персональный компьютер.

4. Включить Источник питания.

5. Включить Модуль МК.

6. В соответствии с разделом 2 в ИСР CodeVisionAVR на базе проекта Lab_02 написать программу, реализующую требуемый алгоритм (см. п.2), и скомпилировать ее.

7. Загрузить полученную прошивку в микроконтроллер УМС-1, как показано в разделе 3.

8. Запротоколировать полученные результаты.

9. Выключить Модуль МК.

10. Выключить Источник питания.

11. Завершить работу Персонального компьютера.

Варианты заданий

| Вариант | ||

Настройки модуля SPI

Порядок передачи данных –

со старшего разряда

Полярность тактового сигнала – низкий уровень

Фаза тактового сигнала –

задний фронт

Формат кадра

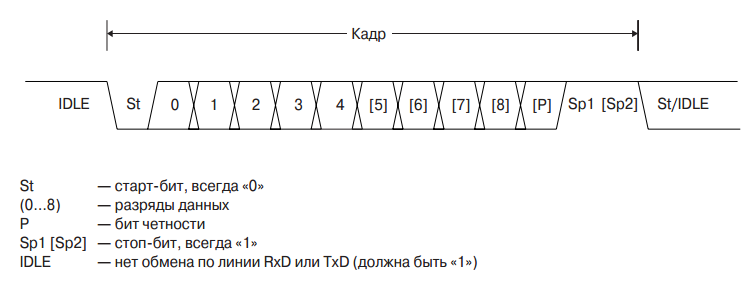

Под кадром в данном случае понимается совокупность одного слова данных и сопутствующей информации (рис. 4.19). Кадр начинается со старт-бита, за которым следует младший разряд слова данных. После старшего разряда слова данных следует один или два стоп-бита. Если включена схема формирования бита четности, он включается между старшим разрядом слова данных и первым стоп-битом.

Рис. 4.19. Формат кадра

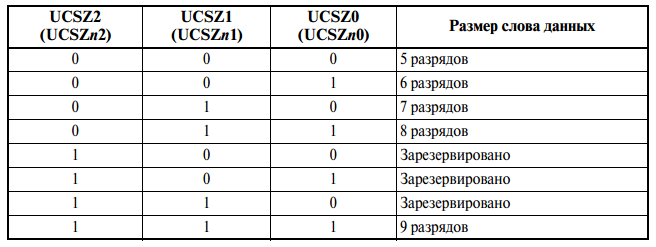

Формат кадра определяется несколькими разрядами регистров UCSRB и UCSRC. Размер слова данных в USART определяется разрядами UCSZ2…UCSZ0 в соответствии с таблицей 4.12.

Таблица 4.12. Определение размера слова данных в модуле USART

Выбор количества стоп-битов в модулях USART осуществляется с помощью разряда USBS регистра UCSRC. Если этот разряд сброшен в «0», блок передатчика формирует 1 стоп-бит в конце посылки. В противном случае, если разряд установлен в «1», блок передатчика формирует 2 стоп-бита.

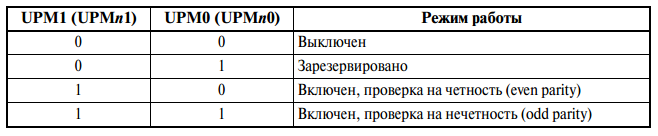

Разряды UPM1:UPM0 регистра UCSRС определяют функционирование схемы контроля четности модулей USART в соответствии с таблицей 4.13.

Таблица 4.13. Управление контролем четности

Значение бита четности получается путем выполнения операции «Исключающее ИЛИ» над всеми разрядами передаваемого слова данных. Если

используется проверка на нечетность (odd parity), полученный результат инвертируется.

Если контроль четности включен, бит четности вставляется передатчиком между старшим разрядом передаваемых данных и первым стоп-битом.

Передача данных

Работа передатчика разрешается установкой в «1» разряда TXEN регистра UCSRB. При установке разряда вывод TXD подключается к передатчику USART и начинает функционировать как выход независимо от установок регистров управления портом.

Передача инициируется записью передаваемых данных в буферный регистр передатчика — регистр данных UDR. После этого данные пересылаются из регистра UDR в сдвиговый регистр передатчика. Одновременно, если используются 9-разрядные данные, значение разряда TXB8 регистра UCSRB копируется в 9-й разряд сдвигового регистра.

При этом возможны два варианта:

· запись в регистр UDR осуществляется в тот момент, когда передатчик находится в состоянии ожидания (предыдущие данные уже переданы). В этом случае данные пересылаются в сдвиговый регистр сразу же после записи в регистр UDR;

· запись в регистр UDR осуществляется во время передачи. В этом случае данные пересылаются в сдвиговый регистр после передачи последнего стоп-бита текущего кадра.

9-й разряд данных должен быть загружен в разряд TXB8 до записи младшего байта слова в регистр данных.

После пересылки слова данных в сдвиговый регистр, флаг UDRE регистра UCSRA устанавливается в «1», что означает готовность передатчика к получению нового слова данных. В этом состоянии флаг остается до следующей записи в буфер. Одновременно с пересылкой в регистре формируется служебная информация — старт-бит, возможный бит четности, а также один или два стоп-бита.

После загрузки сдвигового регистра его содержимое начинает сдвигаться

вправо и поступать на вывод TXD. Скорость сдвига определяется настройками контроллера тактовых сигналов.

Если во время передачи в регистр UDR было записано новое слово данных, то после передачи последнего стоп-бита оно пересылается в сдвиговый регистр. Если же к моменту окончания передачи кадра такой записи выполнено не было, устанавливается флаг прерывания «Передача завершена» TXC регистра UCSRA. Сброс флага осуществляется аппаратно при входе в подпрограмму обработки соответствующего прерывания или программно, записью в этот разряд лог «1».

Выключение передатчика осуществляется сбросом разряда TXEN регистра UCSRB. Если в момент выполнения этой команды осуществлялась передача, сброс разряда произойдет только после завершения текущей и отложенной передач, т.е. после очистки сдвигового и буферного регистров передатчика. При выключенном передатчике вывод TXD может использоваться как контакт ввода/вывода общего назначения.

Прием данных

Работа приемника разрешается установкой разряда RXEN регистра UCSRB. При установке разряда вывод RXD подключается к приемнику USART и начинает функционировать как вход независимо от установок регистров управления портом.

Прием данных начинается сразу же после обнаружения приемником корректного старт-бита. Каждый разряд содержимого кадра затем считывается с частотой, определяемой установками контроллера скорости передачи. Считанные разряды данных последовательно помещаются в сдвиговый регистр приемника до обнаружения первого стоп-бита кадра. После этого содержимое сдвигового регистра пересылается в буфер приемника, из которого принятое значение может быть получено путем чтения регистра данных модуля. При использовании 9-разрядных слов данных значение старшего разряда может быть определено по состоянию флага RX8 регистра UCSRB. Причем содержимое старшего разряда данных должно быть считано до обращения к регистру данных. Это связано с тем, что флаг RX8 отображает значение старшего разряда слова данных кадра, находящегося на верхнем уровне буфера приемника, состояние которого при чтении регистра данных изменится.

Если во время приема кадра была включена схема контроля четности, она вычисляет бит четности для всех разрядов принятого слова данных и сравнивает его с принятым битом четности. Результат проверки запоминается в буфере приемника вместе с принятым словом данных и стоп-битами. Наличие или отсутствие ошибки контроля четности может быть определено по состоянию флага UPE. Этот флаг устанавливается в «1», если следующее слово, которое может быть прочитано из буфера, имеет ошибку контроля четности. При выключенном контроле четности флаг UPE всегда читается как «0».

Блок приемника модуля USART имеет еще два флага, показывающих состояние обмена: флаг ошибки кадрирования FE и флаг переполнения DOR. Флаг FE устанавливается в «1», если значение первого стоп-бита принятого кадра не соответствует требуемому, т.е. равно «0».

Флаг DOR индицирует потерю данных из-за переполнения буфера приемника. Флаг устанавливается в «1» в случае приема старт-бита нового кадра при заполненных буфере и сдвиговом регистре приемника. Установленный флаг DOR означает, что между прошлым байтом, считанным из регистра UDR, и байтом, считанным в данный момент, произошла потеря одного или нескольких кадров.

В модулях USART все флаги ошибок буферизуются вместе со словом данных, т. е. соответствующие разряды регистра UCSRA относятся к кадру, слово данных которого будет прочитано при следующем обращении к регистру данных UDR. Поэтому состояние этих флагов должно быть считано перед обращением к регистру данных. Кроме того, для совместимости с будущими устройствами рекомендуется при записи в регистр UCSRA сбрасывать соответствующие этим флагам разряды записываемого значения в «0».

Для индикации состояния приемника в модуле USART используется флаг прерывания «Прием завершен» RXC регистра UCSRA. Этот флаг устанавливается в «1» при наличии в буфере приемника непрочитанных данных. Этот флаг сбрасывается при опустошении буфера (после считывания всех находящихся в нем данных).

Выключение приемника осуществляется сбросом разряда RXEN регистра UCSRB. В отличие от передатчика приемник выключается сразу же после сброса разряда, т.е. кадр, принимаемый в этот момент, теряется. Кроме того, при выключении приемника очищается его буфер, т.е. теряются также все непрочитанные данные. При выключенном приемнике вывод RXD может использоваться как контакт ввода/вывода общего назначения.

Старт-бит нового кадра может передаваться сразу же после последней выборки, используемой для определения значения разряда.

Порядок выполнения работы

1. Собрать схему стенда УМС-1 в соответствии с рисунком 3.1.

2. Разработать протокол информационного обмена Модуля МК с Блоком системным по последовательному интерфейсу RS-232 в составе УМС-1 в соответствии с вариантом задания (см. подраздел 4.3.6).

Функциональная схема подключения МК к COM-порту Блока системного приведена на рис.4.20.

Структура информационного обмена приведена на рис. 4.21.

Рис. 4.20. Подключение МК к COM-порту

Рис. 4.21. Структура информационного обмена

3. Включить Персональный компьютер.

4. Включить Источник питания.

5. Включить Модуль МК.

6. В соответствии с разделом 2 в ИСР CodeVisionAVR на базе проекта Lab_03 написать программу, реализующую обмен по требуемому протоколу (см. п.2), и скомпилировать ее.

7. Загрузить полученную прошивку в микроконтроллер УМС-1, как показано в разделе 3.

8. Запротоколировать полученные результаты.

9. Выключить Модуль МК.

10. Выключить Источник питания.

11. Завершить работу Персонального компьютера.

Варианты заданий

| Вариант | ||

Настройки модуля USART

Размер слова данных: 8 бит

Стоп-бит: 1

1) Управляющий пакет содержит 1 слово данных.

Управляющий пакет формируется Блоком системным с использованием терминала среды разработки и отладки ПО CodeVisionAVR (см. раздел 2).

Модуль МК должен обеспечивать прием и обработку управляющего пакета, а также вывод его на ЖК-индикатор.

2) Информационный пакет должен формироваться Модулем МК без задержки в ответ на принятый управляющий пакет.

Информационный пакет должен содержать 3 слова данных:

1 слово данных – текущее число (например: 0x01);

2 слово данных – текущий месяц (например: 0х01);

3 слово данных – текущий год (например: 0x0F).

Прием информационного пакета осуществляется Блоком системным с использованием терминала среды разработки и отладки ПО CodeVisionAVR (см. раздел 2).

Кадры, составляющие информационный пакет, должны выдаваться Модулем МК подряд без задержки.

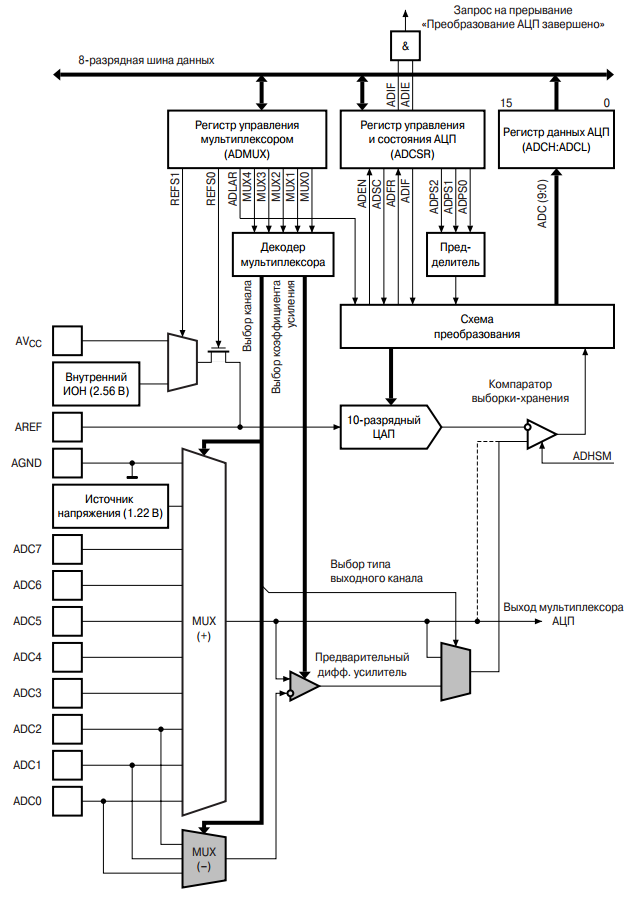

Функционирование модуля АЦП

Структурная схема модуля АЦП МК ATmega32 приведена на рис. 4.22.

Рис. 4.22. Структурная схема модуля АЦП МК ATmega32

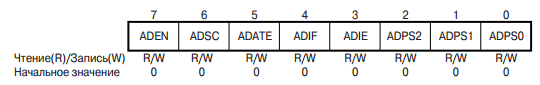

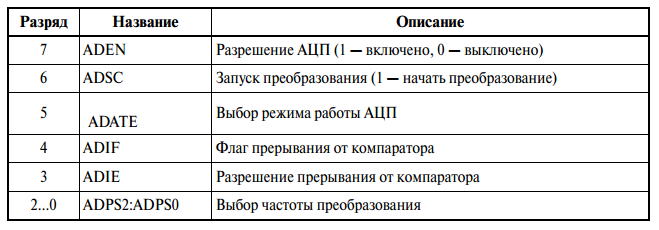

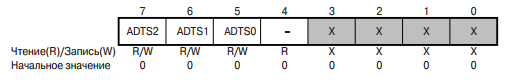

Формат регистров ADCSRA и ADMUX приведен на рис. 4.23 и 4.24, а краткое описание функций их разрядов представлено в таблицах 4.14 и 4.15, соответственно [2].

Рис. 4.23. Формат регистра ADCSRA

Таблица 4.14. Разряды регистра ADCSRA

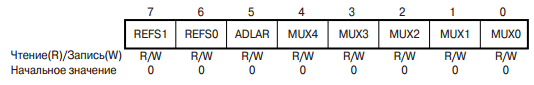

Рис. 4.24. Формат регистра ADMUX

Таблица 4.15. Разряды регистра ADMUX

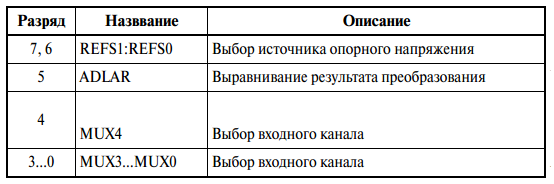

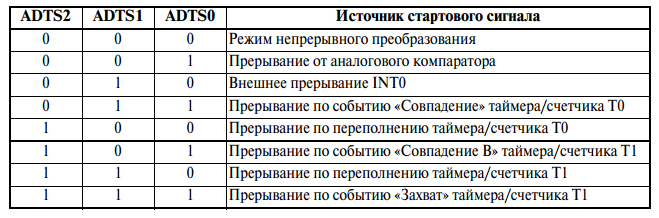

Формат регистра SFIOR приведен на рис. 4.25.

Рис. 4.25. Формат регистра SFIOR

Для разрешения работы АЦП необходимо записать лог. «1» в разряд ADEN регистра ADCSRA, а для выключения — лог. 0. Если АЦП будет выключено во время цикла преобразования, то преобразование завершено не будет (в регистре данных АЦП останется результат предыдущего преобразования).

Запуск АЦП возможен не только по команде пользователя, но и по прерыванию от некоторых периферийных устройств, имеющихся в составе микроконтроллера. Для выбора режима работы в этих моделях используется разряд ADATE регистра ADCSRA и разряды ADTDS2…0 регистра SFIOR.

Если разряд ADATE сброшен в «0», АЦП работает в режиме одиночного преобразования. Если же разряд ADATE установлен в «1», функционирование АЦП определяется содержимым разрядов ADTS2…0 согласно в соответствии с таблицей 4.16.

Таблица 4.16. Источник сигнала для запуска преобразования

Запуск каждого преобразования в режиме одиночного преобразования, а также запуск первого преобразования в режиме непрерывного преобразования осуществляется установкой в «1» разряда ADSC регистра ADCSRA. Запуск преобразования по прерыванию осуществляется при установке в «1» флага выбранного прерывания. Разряд ADSC регистра ADCSRA при этом аппаратно устанавливается в «1». Запуск преобразования в этих режимах также может быть осуществлен установкой в «1» разряда ADSC регистра ADCSRA.

В режимах одиночного и непрерывного преобразований цикл преобразования начинается по первому нарастающему фронту тактового сигнала после установки разряда ADSC. Если используется запуск по прерыванию, то цикл преобразования начинается по первому нарастающему фронту тактового сигнала после установки флага выбранного прерывания. Причем при установке этого флага осуществляется сброс предделителя модуля АЦП. Тем самым обеспечивается фиксированная задержка между генерацией запроса на прерывание и началом цикла преобразования.

Длительность цикла составляет 13 тактов при использовании несимметричного входа и 13 либо 14 тактов при использовании дифференциального входа; выборка и запоминание входного сигнала осуществляется в течение первых 1,5 и 2,5 тактов соответственно. Через 13 (14) тактов преобразование завершается, разряд ADSC аппаратно сбрасывается в «0» (в режиме одиночного преобразования) и результат преобразования сохраняется в регистре данных АЦП. Одновременно устанавливается флаг прерывания ADIF регистра ADCSRA и генерируется запрос на прерывание. Как и флаги остальных прерываний, флаг ADIF сбрасывается аппаратно при запуске подпрограммы обработки прерывания от АЦП или программно, записью в него лог. «1». Разрешение прерывания осуществляется установкой в «1» разряда ADIE регистра ADCSRA при установленном флаге I регистра SREG.

Если АЦП работает в режиме непрерывного преобразования, новый цикл начнется сразу же после записи результата. В режиме одиночного преобразования новое преобразование может быть запущено сразу же после

сброса разряда ADSC (до сохранения результата текущего преобразования). Однако реально цикл преобразования начнется не ранее чем через один такт после окончания текущего преобразования.

При запуске первого преобразования после включения АЦП для выполнения преобразования потребуется 25 тактов, т. е. на 12 тактов больше, чем обычно. В течение этих 12 тактов выполняется «холостое» преобразование,

инициализирующее АЦП.

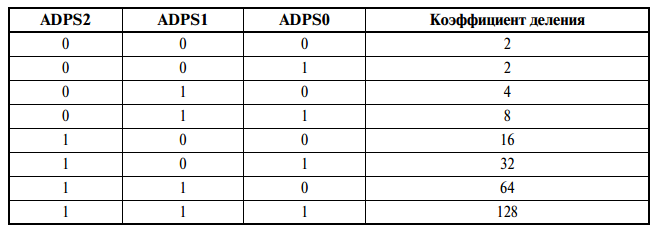

Для формирования тактовой частоты модуля АЦП в нем имеется отдельный предделитель. Коэффициент деления предделителя и, соответственно, длительность преобразования определяется состоянием разрядов ADPS2…ADPS0 регистра ADCSRA (см. таблицу 4.17).

Таблица 4.17. Задание коэффициента деления предделителя АЦП

Наибольшая точность преобразования достигается, если тактовая частота модуля АЦП находится в диапазоне 50…200 кГц. Соответственно коэффициент деления предделителя рекомендуется выбирать таким, чтобы тактовая частота модуля АЦП находилась в указанном диапазоне. Если же точности преобразования меньше 10 разрядов достаточно, можно использовать более высокую частоту, увеличивая тем самым частоту выборки.

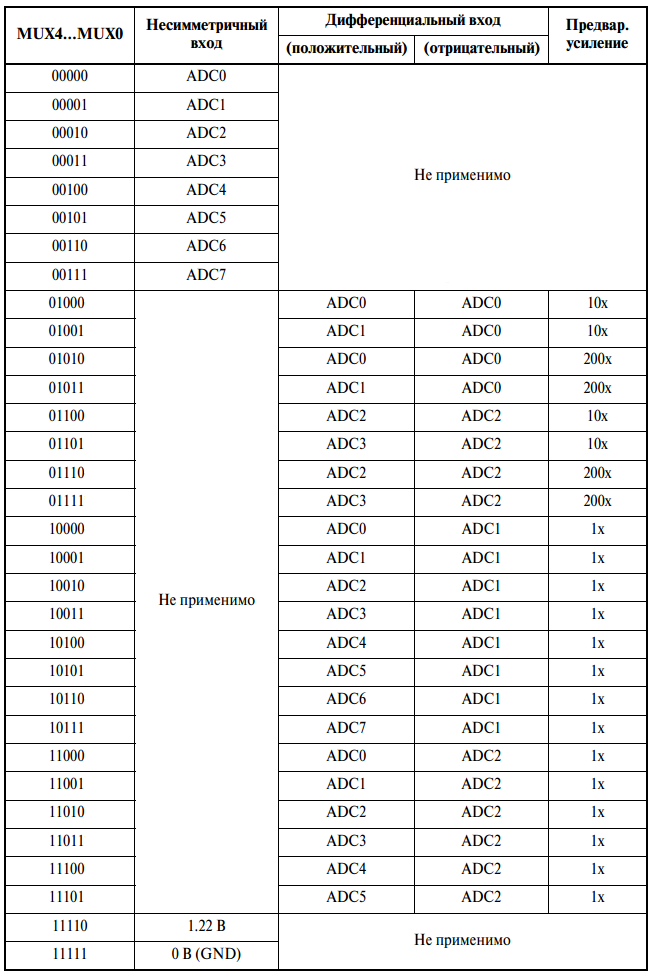

Выводы микроконтроллера, подключенные к входу АЦП, определяются состоянием разрядов MUX4…MUX0 регистра ADMUX в соответствии с таблицей 4.18.

Таблица 4.18. Управление входным мультиплексором АЦП

Следует отметить, что предварительный усилитель, используемый каналами с дифференциальным входом, имеет встроенную схему коррекции смещения. Оставшаяся после коррекции величина смещения может быть учтена программным способом. Для этого следует оба входа дифференциального усилителя подключить к одному и тому же выводу микроконтроллера, а затем вычитать полученное значение из результата последующих преобразований. Таким образом, ошибка смещения может быть

снижена до величины, меньшей 1 МЗР.

Состояние разрядов MUX2…MUX0 можно изменить в любой момент, однако, если это будет сделано во время цикла преобразования, смена канала произойдет только после завершения преобразования. Благодаря этому в режиме непрерывного преобразования можно легко осуществлять последовательное преобразование сигналов нескольких каналов.

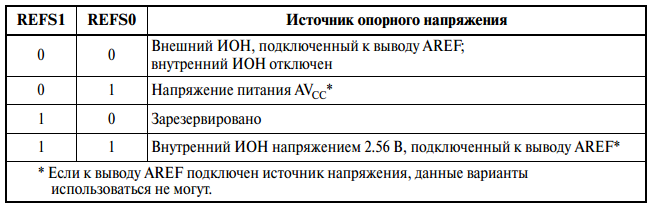

Модуль АЦП может использовать различные источники опорного напряжения (ИОН). Выбор конкретного источника опорного напряжения осуществляется с помощью разрядов REFS1:REFS0 регистра ADMUX в соответствии с таблицей 4.19.

Таблица 4.19. Выбор источника опорного напряжения АЦП

После завершения преобразования (при установке в «1» флага ADIF регистра ADCSRA) его результат сохраняется в регистре данных АЦП. Поскольку АЦП имеет 10 разрядов, этот регистр физически размещен в двух

регистрах ввода/вывода ADCH:ADCL, доступных только для чтения.

По умолчанию результат преобразования выравнивается вправо (старшие 6 разрядов регистра ADCH — незначащие). Однако он может выравниваться и влево (младшие 6 разрядов регистра ADCL — незначащие). Для управления выравниванием результата преобразования служит разряд ADLAR регистра ADMUX. Если этот разряд установлен в «1», результат преобразования выравнивается по левой границе 16-разрядного слова, если сброшен в «0» — по правой границе.

Обращение к регистрам ADCH и ADCL для получения результата преобразования должно выполняться в определенной последовательности: сначала необходимо прочитать регистр ADCL, а затем ADCH.

Для каналов с несимметричным входом результат преобразования определяется выражением ADC=1024*Vin/Vref, где Vin— значение входного

напряжения, а Vref— величина опорного напряжения.

Для каналов с дифференциальным входом результат преобразования определяется выражением ADC= 512*K*(Vpos–Vneg)/Vref, где Vpos – величина напряжения на положительном входе, Vneg – величина напряжения на отрицательном входе, а K— коэффициент усиления.

Результат преобразования представляется в этом случае в дополнительном коде, а его значение лежит в диапазоне $200 (–512)…$1FF (+512).

Сопротивление нагрузки

Сопротивление нагрузки (Rнагр) – сопротивление, измеряемое между цепями питания «+БС» и «Общ БС» бортовой сети (БС) аппаратуры систем управления.

Схема измерения Rнагр приведена на рис. 4.26.

Рис. 4.26. Схема измерения Rнагр

Расчет Rнагр осуществляется по формуле:

,

где

R 1 = 49,9 Ом – эталонное сопротивление схемы измерения Rнагр,

E = 5В – напряжение питания схемы измерения Rнагр.

Порядок выполнения работы

1. Собрать схему стенда УМС-1 в соответствии с рисунком 3.1.

2. Разработать алгоритм измерения статических параметров (Rиз.ст., Rнагр., Rкорп.) с выводом результатов на ЖК-индикатор в соответствии с вариантом задания (см. подраздел 4.4.4).

Функциональная схема измерения статических параметров в УМС-1 приведена на рис.4.29.

Рис. 4.29. Функциональная схема измерения статических параметров

3. Подключить измеряемые Rиз.ст., Rнагр., Rкорп. к Модулю МК в соответствии с рис.4.29

4. Включить Персональный компьютер.

5. Включить Источник питания.

6. Включить Модуль МК.

7. В соответствии с разделом 2 в ИСР CodeVisionAVR на базе проекта Lab_04 написать программу, реализующую требуемый алгоритм (см. п.2), и скомпилировать ее.

8. Загрузить полученную прошивку в микроконтроллер УМС-1, как показано в разделе 3.

9. Запротоколировать полученные результаты.

10. Выключить Модуль МК.

11. Выключить Источник питания.

12. Завершить работу Персонального компьютера.

Варианты заданий

Вариант

Действие

1

Последовательное измерение Rиз.ст., Rнагр., Rкорп. и вывод результатов на ЖКИ

Циклическое измерение Rиз.ст., Rнагр. и цикл. вывод результатов на ЖКИ

2

Циклическое измерение Rиз.ст., Rкорп. и цикл. вывод результатов на ЖКИ

3

Циклическое измерение Rнагр., Rкорп. и цикл. вывод результатов на ЖКИ

4

Циклическое измерение Rиз.ст. и цикл. вывод результатов на ЖКИ

5

Циклическое измерение Rнагр. и цикл. вывод результатов на ЖКИ

1) Повторное нажатие КН2 должно останавливать циклическое измерение.

Измерение напряжения

Датчики измерения постоянного и переменного напряжения (преобразователи измерительные) предназначены для измерения постоянного и переменного напряжения в широком диапазоне. Датчики напряжения обеспечивают гальваническую развязку от измеряемой цепи.

Схема измерения напряжения бортовой сети Uбс объекта контроля с использованием датчика напряжения (ДН) приведена на рис. 4.33.

Рис. 4.33. Схема измерения напряжения Uпит

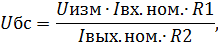

Расчет Uбс осуществляется по формуле:

где

R 1 = 2,55 кОм – токозадающий резистор,

R2 = 75 Ом – сопротивление нагрузки датчика напряжения,

Iвх.ном. = 0,01 А – номинальный входной ток датчика напряжения,

Iвых.ном. = 0,04 А – номинальный выходной ток датчика напряжения.

Измерение тока

Датчики тока предназначены для измерения постоянного или переменного токов с гальванической развязкой силовой цепи и цепей контроля.

Схема измерения тока потребления I объекта контроля с использованием датчика тока (ДТ) приведена на рис. 4.34.

Рис. 4.34. Схема измерения тока потребления I

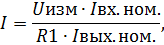

Расчет I осуществляется по формуле:

где

R1 = 50,5 Ом – сопротивление нагрузки датчика тока,

Iвх.ном. = 100 А – номинальный входной ток датчика,

Iвых.ном. = 0,05 А – номинальный выходной ток датчика.

Для измерения малых токов (I < 0,1 А) целесообразно использовать закон полного тока:

Порядок выполнения работы

1. Собрать схему стенда УМС-1 в соответствии с рисунком 3.1.

2. Разработать алгоритм измерения напряжения Uбс бортовой сети и тока потребления I объекта контроля с выводом результатов на ЖК-индикатор в соответствии с вариантом задания (см. подраздел 4.5.4).

При циклическом измерении напряжения Uбс – непрерывно обновлять результат измерения на ЖКИ.

В случае попадания результата измерения напряжения Uбс в заданный диапазон:

- сформировать информационный пакет;

- вывести сообщение на ЖК-индикатор с указанием диапазона;

- остановить циклические измерения

- вернуть МК в режим ожидания управляющего пакета.

Функциональная схема измерения напряжения и тока в УМС-1 приведена на рис.4.35.

Рис. 4.35. Функциональная схема измерения напряжения и тока

3. Подключить жгут К3-ДН к Модулю МК в соответствии с рис.4.35

4. Включить Персональный компьютер.

5. Включить Источник питания.

6. Включить Модуль МК.

7. В соответствии с разделом 2 в ИСР CodeVisionAVR на базе проекта Lab_05 написать программу, реализующую требуемый алгоритм (см. п.2), и скомпилировать ее.

8. Загрузить полученную прошивку в микроконтроллер УМС-1, как показано в разделе 3.

9. Запротоколировать полученные результаты.

10. Выключить Модуль МК.

11. Выключить Источник питания.

12. Завершить работу Персонального компьютера.

Варианты заданий

| Вариант | Управляющий пакет 1) (1 слово данных) | Информационный пакет 2) (1 слово данных) | Диапазон напряжений |

| 1 | 0x01 – однократное измерение тока I 0xA0 – циклическое измерение напряжения Uбс | Результат измерения тока | 5 < Uбс < 15 |

| 2 | 0x02 – однократное измерение тока I 0xB0 – циклическое измерение напряжения Uбс | 15 < Uбс < 25 | |

| 3 | 0x03 – однократное измерение тока I 0xC0 – циклическое измерение напряжения Uбс | 25 < Uбс < 30 | |

| 4 | 0x04 – однократное измерение тока I 0xD0 – циклическое измерение напряжения Uбс | 5 < Uбс < 15 | |

| 5 | 0x05 – однократное измерение тока I 0xE0 – циклическое измерение напряжения Uбс | 15 < Uбс < 25 |

1) Управляющий пакет содержит 1 слово данных.

Управляющий пакет формируется Блоком системным с использованием терминала среды разработки и отладки ПО CodeVisionAVR (см. раздел 2).

Модуль МК должен обеспечивать прием и обработку управляющего пакета, а также вывод его на ЖК-индикатор.

2) Информационный пакет должен формироваться Модулем МК только в случае попадания результата измерения напряжения Uбс в заданный диапазон.

Информационный пакет должен содержать 1 слово данных – целую часть результата измерения напряжения Uбс.

После передачи информационного пакета циклические измерения должны быть остановлены.

Прием информационного пакета осуществляется Блоком системным с использованием терминала среды разработки и отладки ПО CodeVisionAVR (см. раздел 2).

Литература

1. Лебедев М.Б. CodeVisionAVR: пособие для начинающих. – М.: Додэка-XXI, 2008. – 592 с.

2. Евстифеев А.В. Микроконтроллеры AVR семейств Tiny и Mega фирмы

ATMEL. – М.: Додэка-XXI, 2008. – 560 с.

3. Шпак Ю.А. Программирование на языке C для AVR и PIC микроконтроллеров. – К.: МК-Пресс, 2006. – 400 с.

4. Гуревич Е.И., Вилесов А.В. Расчет и оптимизация параметров измерительных узлов автоматизированных систем контроля // Вестник ЮУрГУ. – 2012. – №3(262). – С. 27-33.

МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ

УЧРЕЖДЕНИЕ ВЫСШЕГО ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ

МОСКОВСКИЙ АВИАЦИОННЫЙ ИНСТИТУТ

(НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ УНИВЕРСИТЕТ)

«МАИ»

Кафедра 314Б

А.В. Вилесов, Е.И. Гуревич, В.И. Саусин

УЧЕБНОЕ ПОСОБИЕ

по курсу

«Программные и аппаратные средства систем управления и автоматизированного контроля летательными аппаратами»

Зав. кафедрой 314Б

В.М. Медведев

Москва

2015

ОГЛАВЛЕНИЕ

1. Общие сведения о микроконтроллерахAVR.. 3

2. Интегрированная среда разработки CodeVisionAVR. Разработка и компиляция программы. 6

3. Загрузка программы в микроконтроллер ATmega32 УМС-1. Работа с программным обеспечением PonyProg2000. 13

4. Лабораторный практикум. 17

4.1. Работа №1. AVR микроконтроллер в разработках технических систем. 17

4.2. Работа №2. Изучение последовательного периферийного интерфейса SPI МК AVR и вывод информации на ЖК-дисплей. 29

4.3. Работа №3. Разработка протокола информационного обмена AVR МК по последовательному интерфейсу RS-232. 45

4.4. Работа №4. Измерение основных электрических параметров аппаратуры систем управления с помощью AVR микроконтроллера. 63

4.5. Работа №5. Измерение токов и напряжений с помощью AVR микроконтроллера и датчиков на основе эффекта Холла. 77

5. Литература. 85

Дата: 2018-12-21, просмотров: 516.