По результатам лабораторной работы оформить отчет, содержащий:

1. титульный лист;

2. цель работы;

3. электрическую принципиальную схему проведения лабораторной работы;

4. блок схему алгоритма решения поставленной задачи;

5. код программы с комментариями, реализующей поставленную задачу;

6. выводы.

4.2. Работа №2. Изучение последовательного периферийного интерфейса SPI МК AVR и вывод информации на ЖК-дисплей.

Цель работы: освоение методов обмена по последовательному периферийному интерфейсу SPI МК ATmega32 и приобретение навыков работы c жидкокристаллическим алфавитно-цифровым дисплеем.

Последовательный периферийный интерфейс – SPI (Serial Peripheral Interface), реализованный во всех микроконтроллерах семейства Mega, позволяет осуществлять высокоскоростной обмен данными между микроконтроллером и различными периферийными устройствами, такими, как другие микроконтроллеры, цифровые потенциометры, ЦАП/АЦП, FLASH-ПЗУ и др.

Кроме того, через интерфейс SPI может быть осуществлено программирование микроконтроллера (т.н. режим последовательного программирования).

Функционирование модуля SPI

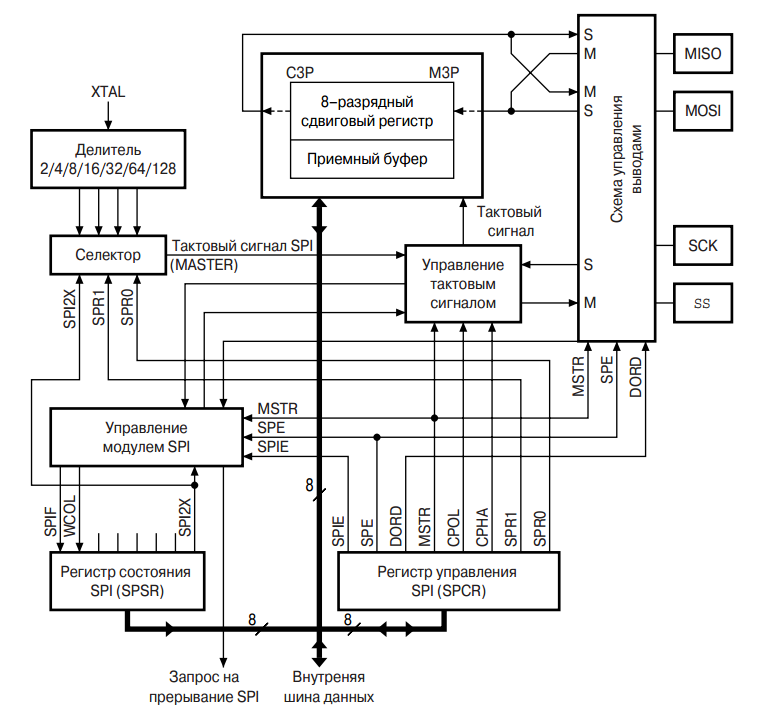

Модуль SPI использует четыре вывода микроконтроллера. Как и для большинства прочих периферийных устройств, эти выводы являются линиями портов ввода/вывода общего назначения [2]. Структурная схема модуля SPI приведена на рис. 4.6.

Рис. 4.6. Структурная схема модуля SPI

В микроконтроллере ATmega32 выводы, используемые модулем SPI, приведены в таблице 4.2.

Таблица 4.2. Выводы, используемые МК ATmega32

| Сигнал | Вывод | Назначение |

| SCK | PB7 | Выход (master)/вход (slave) тактового сигнала |

| MISO | PB6 | Вход (master)/выход (slave) данных |

| MOSI | PB5 | Выход (master)/вход (slave) данных |

| SS | PB4 | Выбор ведомого устройства |

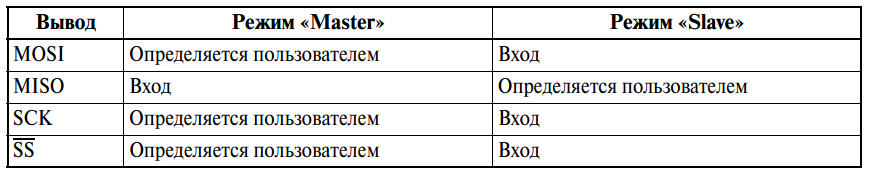

При включенном модуле SPI режим работы указанных выводов (направление передачи данных) переопределяется согласно таблице 4.3. Направление передачи данных определяется состоянием соответствующего разряда регистра DDRB.

Таблица 4.3. Переназначение режима работы выводов модуля SPI

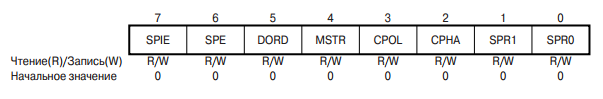

Для управления модулем SPI предназначен регистр управления SPCR. Формат этого регистра приведен на рис. 4.7, а краткое описание функций разрядов регистра приведено в таблице 4.4.

Рис. 4.7. Формат регистра SPCR

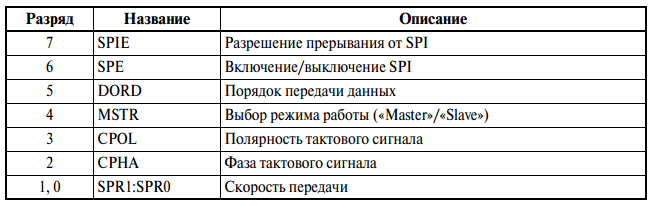

Таблица 4.4. Разряды регистра SPCR

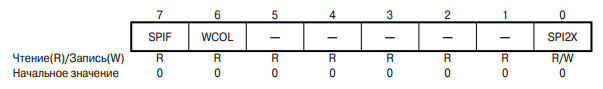

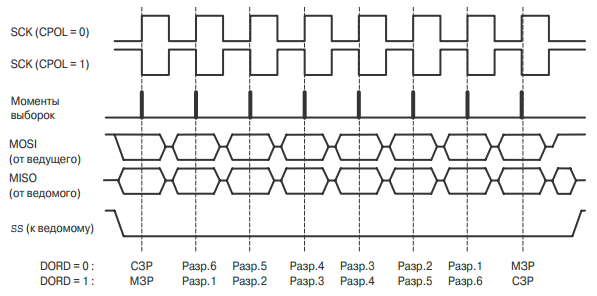

Контроль состояния модуля, а также дополнительное управление скоростью обмена осуществляется с помощью регистра состояния SPSR. Формат этого регистра приведен на рис. 4.8, а назначение его разрядов описано в таблице 4.5.

Рис. 4.8. Формат регистра SPSR

Таблица 4.5. Разряды регистра SPSR

Передаваемые данные записываются, а принимаемые — считываются из

регистра данных SPDR. Запись в этот регистр инициирует начало передачи, а при его чтении считывается содержимое буфера сдвигового регистра. Другими словами, регистр данных служит буфером между регистровым файлом микроконтроллера и сдвиговым регистром модуля SPI.

Соединение двух микроконтроллеров (ведущий—ведомый) по интерфейсу SPI показано на рис. 4.9. Вывод SCK ведущего микроконтроллера является выходом тактового сигнала, а ведомого микроконтроллера — входом.

Рис. 4.9. Соединение микроконтроллеров по интерфейсу SPI

Перед выполнением обмена необходимо разрешить работу модуля SPI. Для этого следует установить в «1» разряд SPE регистра SPCR. Режим работы определяется состоянием разряда MSTR этого регистра: если разряд установлен в «1», микроконтроллер работает в режиме «Master», если сброшен в «0» — в режиме «Slave».

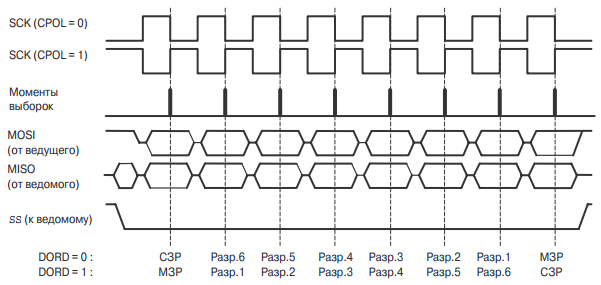

Передача данных осуществляется следующим образом. При записи в регистр данных SPI ведущего микроконтроллера запускается генератор тактового сигнала модуля SPI и данные начинают поразрядно выдаваться на вывод MOSI и, соответственно, поступать на вывод MOSI ведомого микроконтроллера. Порядок передачи разрядов данных определяется состоянием разряда DORD регистра SPCR. Если разряд установлен в «1», первым передается младший разряд байта, если же сброшен в «0» — старший

разряд. После выдачи последнего разряда текущего байта генератор тактового сигнала останавливается с одновременной установкой в «1» флага «Конец передачи» (SPIF). Если прерывания от модуля SPI разрешены (флаг SPIE регистра SPCR установлен в «1»), генерируется запрос на прерывание. После этого ведущий микроконтроллер может начать передачу следующего байта либо, подав на вход SS ведомого микроконтроллера напряжение ВЫСОКОГО уровня, перевести последний в состояние ожидания.

Одновременно с передачей данных от ведущего к ведомому происходит

передача и в обратном направлении при условии, что на входе SS ведомого присутствует напряжение НИЗКОГО уровня. Таким образом, в каждом цикле сдвига происходит обмен данными между устройствами. Аналогично в конце каждого цикла флаг SPIF устанавливается в «1» как в ведущем микроконтроллере, так и в ведомом. Принятые байты сохраняются в приемных

буферах для дальнейшего использования.

В модуле реализована одинарная буферизация при передаче и двойная при приеме. Это означает, что готовый для передачи байт данных не может быть записан в регистр данных SPI до окончания предыдущего цикла обмена. При попытке изменить содержимое регистра данных во время передачи устанавливается в «1» флаг WCOL регистра SPSR. Сбрасывается этот флаг после чтения регистра SPSR с последующим обращением к регистру данных SPI.

Соответственно, при приеме данных принятый байт должен быть прочитан из регистра данных SPI до того, как в сдвиговый регистр поступит последний разряд следующего байта. В противном случае первый байт будет потерян.

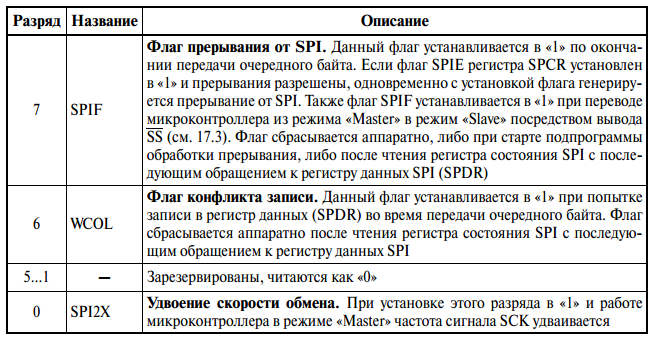

Спецификация интерфейса SPI предусматривает 4 режима передачи данных. Эти режимы различаются соответствием между фазой (момент считывания сигнала) тактового сигнала SCK, его полярностью и передаваемыми данными. Всего существует 4 таких комбинации, определяемых состоянием разрядов CPHA и CPOL регистра SPCR (см. таблицу 4.6).

Таблица 4.6. Задание режима передачи данных

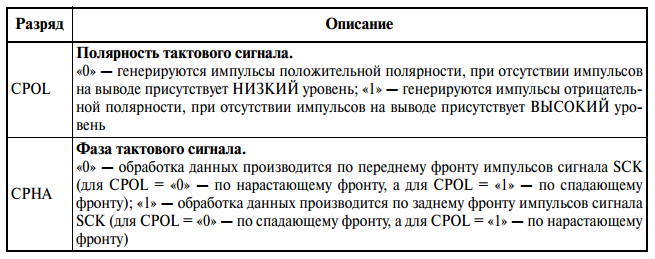

Соответствующие этим режимам форматы обмена данными через SPI приведены на рис. 4.10 и рис. 4.11 (передача ведется от старшего разряда

к младшему).

Рис. 4.10. Передача данных при CPHA = «0»

Рис. 4.11. Передача данных при CPHA = «1»

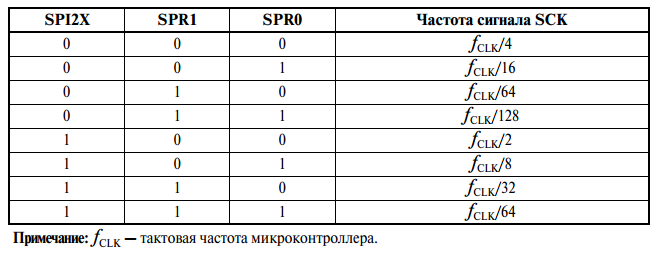

Частота тактового сигнала SCK и, соответственно, скорость передачи данных по интерфейсу определяется состоянием разрядов SPR1:SPR0 регистра SPCR и разряда SPI2X регистра SPSR ведущего микроконтроллера (см. таблицу 4.7).

Таблица 4.7. Задание частоты тактового сигнала SCK

Примечание: Функционирование микроконтроллера в режиме «Slave» гарантируется только на частотах, меньших или равных fCLK/4.

Вывод SS предназначен для выбора активного ведомого устройства и в режиме «Slave» всегда является входом. При подаче на него напряжения НИЗКОГО уровня модуль SPI активируется и вывод MOSI переключается в режим вывода данных (если это задано пользователем). Остальные выводы модуля SPI являются в этом режиме входами. А при подаче на вывод SS напряжения ВЫСОКОГО уровня все выводы модуля SPI переключаются в режим ввода данных. При этом модуль переходит в неактивное состояние и прием данных не производится. Как правило, в этом состоянии программа изменяет содержимое регистра данных.

Следует помнить, что каждый раз, когда на вывод SS подается напряжение ВЫСОКОГО уровня, происходит сброс модуля SPI. Соответственно, если изменение состояния этого вывода произойдет во время передачи данных – обмен прекратится, а передаваемый и принимаемый байты будут потеряны.

Если же микроконтроллер находится в режиме «Master» (разряд MSTR

регистра SPCR установлен в «1»), направление передачи данных через вывод

SS определяется пользователем. Если вывод сконфигурирован как выход, он работает как линия вывода общего назначения и не влияет на работу модуля SPI. В этом случае он используется для управления выводом SS микроконтроллера, работающего в режиме «Slave».

Если же вывод сконфигурирован как вход, то для обеспечения нормальной работы модуля SPI на него должно быть подано напряжение ВЫСОКОГО уровня. Подача на этот вход напряжения НИЗКОГО уровня от какой-либо внешней схемы будет воспринята модулем SPI как выбор данного микроконтроллера в качестве ведомого, и соответственно, начало передачи ему данных. Во избежание конфликта на шине – модуль SPI в таких случаях выполняет следующие действия:

1. Флаг MSTR регистра SPCR сбрасывается, и микроконтроллер переключается в режим «Slave». Как следствие, выводы MOSI и SCK начинают функционировать как входы.

2. Устанавливается флаг SPIF регистра SPSR, генерируя запрос на прерывание от SPI. Если прерывания от SPI разрешены и флаг I регистра SREG установлен в «1», происходит запуск подпрограммы обработки прерывания.

Таким образом, если ведущий микроконтроллер использует передачу данных, управляемую прерыванием и существует вероятность подачи на вход SS напряжения НИЗКОГО уровня, в подпрограмме обработки прерывания от SPI обязательно должна осуществляться проверка состояния флага MSTR. При обнаружении сброса этого флага он должен быть программно установлен обратно в «1» для обратного перевода микроконтроллера в режим «Master».

На рис. 4.12. и 4.13 рассмотрены регистры для управления модулем последовательного периферийного интерфейса SPI.

Рис. 4.12. Регистр управления SPI

Рис. 4.13. Регистр состояния (сверху), регистр данных (снизу) SPI

Таблица 4.7. Задание частоты тактового сигнала SCK

Основы языка Си

Для выполнения лабораторной работы №2 необходимо ознакомиться со следующими пунктами главы 3 [3]:

- функции;

- указатели и адреса переменных;

- массивы и строки;

- стандартные функции ввода вывода.

Дата: 2018-12-21, просмотров: 459.