Основу кодирующих и декодирующих устройств циклических кодов составляют регистры сдвига с обратными связями, позволяющие осуществлять как умножение, так и деление многочленов с приведением коэффициентов по модулю два. Такие регистры также называют многотактными линейными переключательными схемами и линейными кодовыми фильтрами Хаффмена. Они состоят из ячеек памяти, сумматоров по модулю два и устройств умножения на коэффициенты многочленов множителя или делителя. В случае двоичных кодов для умножения на коэффициент, равный 1, требуется только наличие связи в схеме. Если коэффициент равен 0, то связь отсутствует. Сдвиг информации в регистре осуществляется импульсами, поступающими с генератора продвигающих импульсов, который на схеме, как правило, не указывается. На вход устройств поступают только коэффициенты многочленов, причем начиная с коэффициента при переменной в старшей степени.

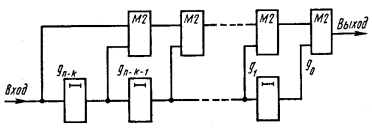

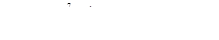

Рис. 4.9.

На рис. 4.9 представлена схема, выполняющая умножение произвольного (например, информационного) многочлена

a ( x ) = a 0 + a 1 x + … + ak -1 xk -1

на некоторый фиксированный (например, образующий) многочлен

g(x) = g0 + g1x + … + gn-kxn-k.

Произведение этих многочленов равно

a(x)g(x)=a0g0 + (a0g1 + a1g0)x + … +(ak-2gn-k + ak-1gn-k-1)xn-2 +ak-1gn-kxn-1

Предполагаем, что первоначально ячейки памяти находятся в нулевом состоянии и что за коэффициентами множимого следует n - k нулей.

На первом такте на вход схемы поступает первый коэффициент а k -1 многочлена а(х) и на выходе появляется первый коэффициент произведения, равный

ak -1 gn - k

На следующем такте на выход поступит сумма

ak-2gn-k + ak-1gn-k-1 ,

т.е. второй коэффициент произведения, и т. д. На n-м такте все ячейки, кроме последней, будут в нулевом состоянии и на выходе получим последний коэффициент а0 g 0

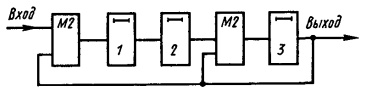

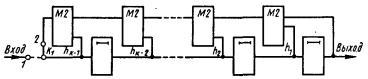

Используется также схема умножения многочленов при поступлении множимого младшим разрядом вперед (рис. 4.10).

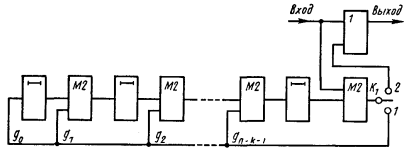

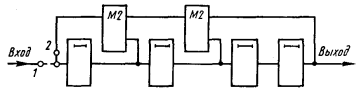

На рис. 4.11 представлена схема, выполняющая деление произвольного многочлена, например

a(x)xm = a0 + a1x + … + an-1xn-1

на некоторый фиксированный (например, образующий) многочлен

g(x) = g0 + g1x + … + gn-kxn-k

Обратные связи регистра соответствуют виду многочлена g ( x ). Количество включаемых в него сумматоров равно числу отличных от нуля коэффициентов g ( x ), уменьшенному на единицу. Это объясняется тем, что сумматор сложения коэффициентов старших разрядов многочленов делимого и делителя в регистр не включается, так как результат сложения заранее известен (он равен 0).

Рис. 4.10.

Рис. 4.11.

За первые n - k тактов коэффициенты многочлена-делимого заполняют регистр, причем коэффициент при х в старшей степени достигает крайней правой ячейки. На следующем такте «единица» делимого, выходящая из крайней ячейки регистра, по цепи обратной связи подается к сумматорам по модулю два, что равносильно вычитанию многочлена-делителя из многочлена-делимого. Если в результате предыдущей операции коэффициент при старшей степени х у остатка оказался равным нулю, то на следующем такте делитель не вычитается. Коэффициенты делимого только сдвигаются вперед по регистру на один разряд, что находится в полном соответствии с тем, как это делается при делении многочленов столбиком.

Деление заканчивается с приходом последнего символа многочлена-делимого. При этом разность будет иметь более низкую степень, чем делитель. Эта разность и есть остаток.

Отметим, что если в качестве многочлена-делителя выбран простой многочлен степени m = n -k, то, продолжая делить образовавшийся остаток при отключенном входе, будем получать в регистре по одному разу каждое из ненулевых m-разрядных двоичных чисел. Затем эта последовательность чисел повторяется.

Пример 37. Рассмотрим процесс деления многочлена а(х)хт =(x3+1)x3 на образующий многочлен g(x) = х3+ х2+1. Схема для этого случая представлена на рис. 4.12, где 1, 2, 3-ячейки регистра. Работа схемы поясняется табл. 4.16.

Рис. 4.12.

Вычисление остатка начинается с четвертого такта и заканчивается после седьмого такта. Последующие сдвиги приводят к образованию в регистре последовательности из семи различных ненулевых трехразрядных чисел. В дальнейшем эта последовательность чисел повторяется.

Рассмотренные выше схемы умножения и деления многочленов непосредственно в том виде, в каком они представлены на рис. 4.10, 4.11, в качестве кодирующих устройств циклических кодов на практике не применяются: первая - из-за того, что образующаяся кодовая комбинация в явном виде не содержит информационных символов, а вторая - из-за того, что между информационными и проверочными символами образуется разрыв в n - k разрядов.

Кодирующие устройства

Все известные кодирующие устройства для любых типов циклических кодов, выполненные на регистрах сдвига, можно свести к двум типам схем согласно рассмотренным ранее методам кодирования.

Таблица 4.16.

| Номер такта | Вход | Состояние ячеек регистра | Номер такта | Вход | Состояние ячеек регистра | ||||

| 1 | 2 | 3 | 1 | 2 | 3 | ||||

| 1 2 3 4 5 6 7 | 1 0 0 1 0 0 0 | 1 0 0 0 1 1 1 | 0 1 0 0 0 1 1 | 0 0 1 1 1 1 0 | 8 9 10 11 12 13 14 | - - - - - - - | 0 1 0 0 1 1 1 | 1 0 1 0 0 1 1 | 1 0 0 1 1 1 0 |

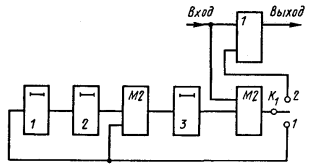

Схемы первого типа вычисляют значения проверочных символов путем непосредственного деления многочлена а(х)хт на образующий многочлен g ( x ). Это делается с помощью регистра сдвига, содержащего n - k разрядов (рис. 4.13).

Рис. 4.13.

Схема отличается от ранее рассмотренной тем, что коэффициенты кодируемого многочлена участвуют в обратной связи не через n - k сдвигов, а сразу с первого такта. Это позволяет устранить разрыв между информационными и проверочными символами.

В исходном состоянии ключ К1 находится в положении 1. Информационные символы одновременно поступают как в линию связи, так и в регистр сдвига, где за k тактов образуется остаток. Затем ключ K 1 переходит в положение 2 и остаток поступает в линию связи.

Пример 38. Рассмотрим процесс деления многочлена а(х)хт = (х3 + 1)x3 на многочлен g(x) = x3 + х2+ 1 за k тактов.

Схема кодирующего устройства для заданного g(x) приведена на рис. 4.14. Процесс формирования кодовой комбинации шаг за шагом представлен в табл. 4.17, где черточками отмечены освобождающиеся ячейки, занимаемые новыми информационными символами.

С помощью схем второго типа вычисляют значения проверочных символов как линейную комбинацию информационных символов, т. е. они построены на использовании основного свойства систематических кодов. Кодирующее устройство строится на основе k-разрядного регистра сдвига (рис. 4.15).

Рис. 4.14.

Таблица 4.17.

| Номер такта | Вход | Состояние ячеек регистра | Выход | ||

| 1 | 2 | 3 | |||

| 1 2 3 4 5 6 7 | 1 0 0 1 0 0 0 | 1 1 1 1 - - - | 0 1 1 1 1 - - | 1 1 0 0 1 1 - | 1 01 001 1001 01001 101001 1101001 |

Выходы ячеек памяти подключаются к сумматору в цепи обратной связи в соответствии с видом генераторного многочлена

h ( x ) = ( xn + 1)/ g ( x ) = h 0 + h 1 x + … + hkxk

В исходном положении ключ К1 находится в положении 1. За первые k тактов поступающие на вход информационные символы заполняют все ячейки регистра. После этого ключ переводят в положение 2. На каждом из последующих тактов один из информационных символов выдается в канал связи и одновременно формируется проверочный символ, который записывается в последнюю ячейку регистра. Через n - k тактов процесс формирования проверочных символов заканчивается и ключ K1 снова переводится в положение 1.

В течение последующих k тактов содержимое регистра выдается в канал связи с одновременным заполнением ячеек новой последовательности информационных символов.

Пример 39. Рассмотрим процесс формирования кодовой комбинации с использованием генераторного многочлена для случая g(x) = x3 + x2 + 1 и а(x) = x3 + 1.

Определяем генераторный многочлен:

Рис. 4.15.

Рис. 4.16.

Соответствующая h ( x ) схема кодирующего устройства приведена на рис. 4.16. Формирование кодовой комбинации поясняется табл. 4.18. Оно начинается после заполнения регистра информационными символами.

Декодирующие устройства

Декодирование комбинаций циклического кода можно проводить различными методами. Существуют методы, основанные на использовании рекуррентных соотношений, на мажоритарном принципе, на вычислении остатка от деления принятой комбинации на образующий многочлен кода и др. Целесообразность применения каждого из них зависит от конкретных характеристик используемого кода.

Рассмотрим сначала устройства декодирования, в которых для обнаружения и исправления ошибок производится деление произвольного многочлена f ( x ), соответствующего принятой комбинации, на образующий многочлен кода g 0 ( x ). В этом случае при декодировании могут использоваться те же регистры сдвига, что и при кодировании.

Таблица 4.18.

| Номер такта | Состояние ячеек регистра | Выход | |||

| 1 | 2 | 3 | 4 | ||

| 1 2 3 4 5 6 7 | 1 0 1 1 - - - | 0 1 0 1 1 - - - | 0 0 1 0 1 1 - - | 1 0 0 1 0 1 1 - | 1 01 001 1001 01001 101001 1101001 |

Рис. 4.17.

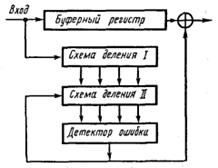

Декодирующие устройства для кодов, обнаруживающих ошибки, по существу ничем не отличаются от схем кодирующих устройств. В них добавляется лишь буферный регистр для хранения принятого сообщения на время проведения операции деления. Если остатка не обнаружено (случай отсутствия ошибки), то информация с буферного регистра считывается в дешифратор сообщения. Если остаток обнаружен (случай наличия ошибки), то информация в буферном регистре уничтожается и на передающую сторону посылается импульс запроса повторной передачи.

В случае исправления ошибок схема несколько усложняется. Информацию о разрядах, в которых произошла ошибка, несет, как и ранее, остаток. Схема декодирующего устройства представлена на рис. 4.17.

Символы подлежащей декодированию кодовой комбинации, возможно, содержащей ошибку, последовательно, начиная со старшего разряда, вводятся в n-разрядный буферный регистр сдвига и одновременно в схему деления, где за n тактов определяется остаток, который в случае непрерывной передачи сразу же переписывается в регистр второй аналогичной схемы деления.

Начиная с (n + 1)-го такта в буферный регистр и первую схему деления начинают поступать символы следующей кодовой комбинации. Одновременно на каждом такте буферный регистр покидает один символ, а в регистре второй схемы деления появляется новый остаток (синдром). Детектор ошибок, контролирующий состояния ячеек этого регистра, представляет собой комбинаторно-логическую схему, построенную с таким расчетом, чтобы она отмечала все те синдромы («выделенные синдромы»), которые появляются в схеме деления, когда каждый из ошибочных символов занимает крайнюю правую ячейку в буферном регистре. При последующем сдвиге детектор формирует сигнал «1», который, воздействуя на сумматор коррекции, исправляет искаженный символ.

Одновременно по цепи обратной связи с выхода детектора подается сигнал «1» на входной сумматор регистра второй схемы деления. Этот сигнал изменяет выделенный синдром так, чтобы он снова соответствовал более простому типу ошибки, которую еще подлежит исправить. Продолжая сдвиги, обнаружим и другие выделенные синдромы. После исправления последней ошибки все ячейки декодирующего регистра должны оказаться в нулевом состоянии. Если в результате автономных сдвигов состояние регистра не окажется нулевым, это означает, что произошла неисправимая ошибка.

Для декодирования кодовых комбинаций, разнесенных во времени, достаточно одной схемы деления, осуществляющей декодирование за 2n тактов.

Сложность детектора ошибок зависит от числа выделенных синдромом. Простейшие детекторы получаются при реализации кодов, рассчитанных на исправление единичных ошибок.

Выделенный синдром появляется в схеме деления раньше всего в случае, когда ошибка имеет место в старшем разряде кодовой комбинации, так как он первым достигает крайней правой ячейки буферного регистра. Поскольку неискаженная кодовая комбинация делится на g 0 ( x ) без остатка, то для определения выделенного синдрома достаточно разделить на g 0 ( x ) вектор ошибки с единицей в старшем разряде. Остаток, получающийся на n -м такте, и является искомым выделенным синдромом.

В зависимости от номера искаженного разряда после первых тактов будем получать различные остатки (опознаватели соответствующих векторов ошибок). Вследствие этого выделенный синдром будет появляться в регистре схемы деления через различное число последующих тактов, обеспечивая исправление искаженного символа.

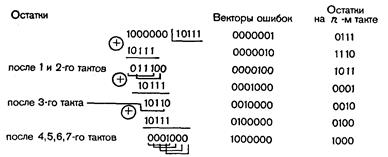

В качестве схем деления в декодирующем устройстве могут быть использованы как схемы, определяющие остаток за n тактов (см. рис. 4.11), так и схемы, определяющие остаток за k тактов (рис. 4.13). При использовании схемы деления за k тактов векторам одиночных ошибок ξ (х) будут соответствовать другие остатки на n-м такте, являющиеся результатом деления на образующий многочлен кода векторов ξ(х)хт, а на ξ(x). Поэтому выделенные синдромы, а следовательно, и детекторы ошибок для указанных схем будут различны.

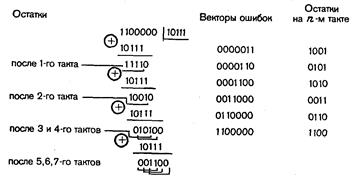

Пример 40. Рассмотрим процесс исправления единичной ошибки при использовании кода (7,4) с образующим многочленом g(x) = х3 + х2 + 1 и применении в декодирующем устройстве схем деления за n и k тактов.

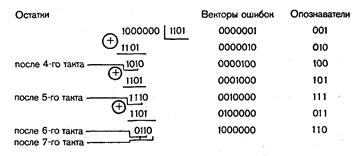

Определим опознаватели ошибок и выделенный синдром для случая использования схемы деления за n тактов:

Детектор ошибки, обеспечивающий формирование на выходе сигнала только в случае появления в схеме деления остатка 110, можно реализовать посредством двух логических элементов НЕ и одного логического элемента ИЛИ-НЕ.

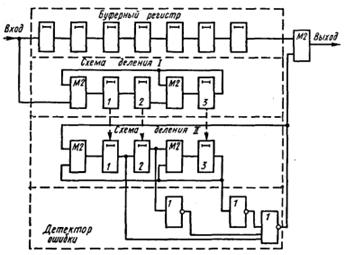

На рис. 4.18 приведена схема соответствующего декодирующего устройства. В табл. 4.19 представлен процесс исправления ошибки для случая, когда кодовая комбинация 1001011 (см. табл. 4.18) поступила на вход декодирующего устройства с искаженным символом в 4-м разряде (1000011).

После n (в данном случае 7) тактов в схему деления II переписывается опознаватель ошибки 101.

Рис. 4.18.

Таблица 4.19.

| Номер такта | Вход | Состояние ячеек схем деления | Выход после коррекции | ||

| 1 | 2 | 3 | |||

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 | 1 0 0 0 0 1 1 0 0 0 0 0 0 0 | 1 0 0 1 1 0 1 1 1 0 0 0 0 0 | 0 1 0 0 1 1 0 1 1 1 0 0 0 0 | 0 0 1 1 1 0 1 1 0 1 0 0 0 0 | Переписывается в схему деления II 1 01 001 1001 01001 101001 1101001 |

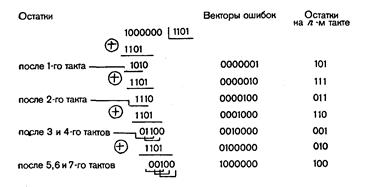

На каждом последующем такте на выходе буферного регистра появляется неискаженный символ корректируемой кодовой комбинации, а в схеме деления II новый остаток. Выделенный синдром появится в схеме деления на 10-м такте, когда искаженный символ займет крайнюю правую ячейку регистра. На следующем такте он попадет в корректирующий сумматор и будет там исправлен импульсом, поступающим с выхода детектора ошибки. Этот же импульс по цепи обратной связи приводит ячейки схемы деления II в нулевое состояние (корректирует выделенный синдром). При использовании схемы деления за k тактов соответствие между векторами ошибок и остатками на n-м такте иное.

Рис. 4.19.

Таблица 4.20.

| Номер такта | Вход | Состояние ячеек схем деления | Выход после коррекции | ||

| 1 | 2 | 3 | |||

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 | 1 0 0 0 0 1 1 0 0 0 0 0 0 0 | 1 1 1 0 1 1 0 1 0 0 0 0 0 0 | 0 1 1 1 0 1 1 0 1 0 0 0 0 0 | 1 1 0 1 0 1 1 0 0 1 0 0 0 | Переписывается в схему деления II 1 01 001 1001 01001 101001 1101001 |

Детектор для выделенного синдрома 100 можно построить из одного логического элемента НЕ и одного элемента ИЛИ-НЕ.

На рис. 4.19 представлена схема декодирующего устройства для этого случая. Табл. 4.20 позволяет проследить по тактам процесс исправления ошибки в кодовой комбинации 1000011 (искажен символ в 4-м разряде).

Сравнение показывает, что использование в декодирующем устройстве схемы деления за k тактов предпочтительнее, так как выделенный синдром в этом случае при любом объеме кода содержит единицу в старшем и нули во всех остальных разрядах, что приводит к более простому детектору ошибки.

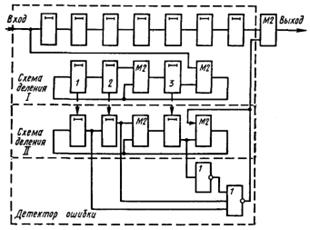

Пример 41. Рассмотрим более сложный случай исправления одиночных и двойных смежных ошибок. Для этой цели может использоваться циклический код (7,3) с образующим многочленом g(x) = (х + 1)(x3 + x2+1).

Ориентируясь на схему деления за k тактов, найдем выделенный синдром для двойных смежных ошибок:

Для одиночных ошибок соответственно получим

Детектор ошибок в этом случае должен формировать сигнал коррекции при появлении каждого выделенного синдрома. Схема декодирующего устройства представлена на рис. 4.20.

Процесс исправления кодовой комбинации 1000010 с искаженными символами в 4-м и 5-м разрядах поясняется табл. 4.21.

На 9-м такте в схеме деления II появляется первый выделенный синдром 1100. На следующем такте на выходе аналогично обозначенного элемента ИЛИ-НЕ детектора ошибок формируется импульс коррекции, который исправляет 5-й разряд кодовой комбинации и одновременно по цепи обратной связи изменяет остаток в схеме деления II, приводя его в соответствие выделенному синдрому еще не исправленной одиночной ошибки в 4-м разряде (1000). На 11-м такте импульс коррекции формирует элемент ИЛИ-НЕ детектора ошибок, соответствующий указанному выделенному синдрому. Этим импульсом обеспечивается исправление 4-го разряда кодовой комбинации и получение нулевого остатка в схеме деления II.

Рис. 4.20.

Таблица 4.21.

| Номер такта | Вход | Состояние ячеек схем деления | Выход после коррекции | |||

| 1 | 2 | 3 | 4 | |||

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 | 1 0 0 0 1 0 0 0 0 0 0 0 0 0 | 1 0 1 1 1 0 1 0 0 0 0 0 0 0 | 1 1 1 0 0 1 1 1 0 0 0 0 0 0 | 1 1 0 0 1 0 0 1 1 0 0 0 0 0 | 0 1 1 0 0 1 0 0 1 1 0 0 0 0 | Переписывается в схему деления II 1 01 101 1101 11101 011101 0011101 |

Список литературы

2. Дмитриев В.И. Прикладная теория информации. Учебник для студентов ВУЗов по специальности «Автоматизированные системы обработки информации и управления». – М.: Высшая школа, 1989 – 320 с.

Дата: 2019-07-30, просмотров: 407.