Адаптер послідовного інтерфейсу слугує для обміну інформацією у послідовному коді у двох режимах: асинхронному та синхронному.

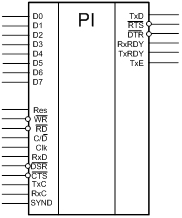

Умовно графічне зображення адаптеру наведено на Рис.16

Рис.16 - Адаптер послідовного інтерфейсу i8254

Електричні параметри i8251:

1. Напруга живлення - 5 В

2. Вихідна напруга:

високого рівня - 2,4 В

низькі рівні - 0,45 В

3. Вихідний струм високого рівня - 1 мА

4. Вихідний струм низького рівня - 5 мА

5. Вхідний струм високого рівня - 30 мкА

6. Вхідний струм низького рівня - 30 мкА

Програмування адаптеру послідовного інтерфейсу Intel 8251

Завдання: Запрограмувати адаптер i8251 для роботи у асинхронному режимі на випадок:

кількість стоп-біт: 2

кількість інформаційних біт: 8

контроль парності

коеф. ділення частоти синхронізації: 16

кількість посилок: 48

Програма:

Спочатку сформуємо слово приказу - 11011110 #DEH

Початковий адрес у пам’яті #100Н

Кінцевий адрес у пам’яті #130Н

Адреса адаптеру #E000H

i8251: ; оголошення констант

. equadr1 = 0xE001; адреса А0=1

. equadr2 = 0xE000; адреса адаптеру

. equmask1 = 0x01; відокремлення TxRDY

. equmask2 = 0x02; відокремлення RxRDY

. equmask3 = 0b00111000; виявлення помилок

ldiR0, 0xDE; слово приказу

stsadr1, R0; програмув. на асинхр. режим

m1: ldiR0, 0x01; завантаження РПД=1

stsadr1, R0; слово команда, дозвіл

; передачі

m2: ldsR0, adr1; читання слова-стану

andiR0, mask1; маскування біта TxRDY

breqm2

ldiR31, 0x01; поч. адреса для видачі 100H потрапляє у

; старший байт Z (ZH=R31)

ldiR2, 0x30; 48 посилок

m3: ; програмув. передачі

ld R3, Z+; передача із слідуючої комірки у РОН

stsadr2, R3; видача байту інформації

decR2; декримент лічильника

cpiR2, 0

brnem3

RET

m4: ldiR0, 0x04; завантаження РПД=1

stsadr1, R0; слово команда, дозвіл

; прийому

m5: ldsR0, adr1; читання слова-стану

andiR0, mask2; маскування біта RxRDY

breqm5

ldsR0, adr1; читання слова-стану

andiR0, mask3; перевірка на факт помилки

brneerror

ldiR30, 0x31; поч. адреса для прийому 131H

; потрапляє побайтово до молодшого та

; старшого байтів рег. Z (ZL=R30)

ldiR31, 0x01; (ZH=R31)

ldiR2, 0x30; 48 посилок

m6: ; програмув. прийому

ldsR3, adr2; прийом байту інформації

stZ+, R3; прийом у слідуючу комірку РОН

decR2; декримент лічильника

cpiR2, 0

brnem6

RET

Розрахунок електричних навантажень на лінії мікросхем

Проведемо розрахунок навантажувальних характеристик для виходів мікроконтролера для шини даних, адреси і керування.

Навантаження на шину даних мікроконтролера визначається по формулі:

IвихDL =IвхСKI + IвхPIТ + IвхOZU + IвхPZU + IвхACP = 0,03 + 0,03 + 1,6 + 0,25 + 0,1 = = 2,01 мА;

IвихDH = IвхCKI + IвхPIТ + IвхOZU + IвхPZU +IвхACP = 0,03 + 0,03 + 0,1 + 0,04 + 0,1 = = 0,3 мА;

СD = СCKI + СPIТ + СOZU + СPZU + СACP = 5 + 5 + 25 + 35 + 6 = 76 пФ.

Так як навантаження на шину даних не перевищує 40 мА, то використання додаткового шиного формувача не потрібне. Використаний буферний регістр відповідає поставленим вимогам.

Навантаження на шину адреси мікроконтролера визначається по формулі:

IвихАL =IвхСKI + IвхPIТ + IвхOZU + IвхPZU = 0,03 + 0,03 + 1,6 + 0,50 = 2,16 мА;

IвихАH = IвхCKI + IвхPIТ + IвхOZU + IвхPZU = 0,03 + 0,03 + 0,1 + 0,08 = 0,24 мА;

СА = СCKI + СPIТ + СOZU + СPZU = 5 + 5 + 25 + 30 = 65 пФ.

Так як навантаження на шину адреси не перевищує 40 мА, то використання додаткового шиного формувача не потрібне. Використаний буферний регістр відповідає поставленим вимогам.

Навантаження на шину керування мікроконтролера визначається по формулі:

IвихСL =IвхСKI + IвхPIТ + IвхOZU + IвхPZU = 0,03 + 0,03 + 1,6 + 0,25 = 1,94 мА;

IвихСH = IвхCKI + IвхPIТ + IвхOZU + IвхPZU = 0,03 + 0,03 + 0,1 + 0,04 = 0,23 мА;

СС = СCKI + СPIТ + СOZU + СPZU = 5 + 5 + 25 + 25 = 60 пФ.

Отримані при розрахунку значення струмув та ємностей не перевищують граничні значення.

Висновки

В ході виконання курсової роботи була розроблена повна принципова схема мікропроцесорної системи. Були розглянуті різні варіанти структурної та принципової схем. Згідно із завданням складена програма ініціалізації окремих блоків. Обрані та розраховані необхідні у системі елементи. Була розглянута видача і запис інформації в пам’ять, АЦП, керування системою за допомогою клавіатури та індикації.

Виконання курсової дозволить у подальшому без труднощів розробляти подібні та ще більш складні процесорні системи.

Дата: 2019-07-31, просмотров: 347.