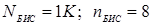

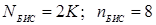

Ісходні дані:

Кількість комірок зовнішнього ОЗП NОЗУ - 2К×8

Вхідні струми:

при логічному 0, IIL - 1,6 мА

при логічній 1, IIH - 0,1 мА

Вхідна ємкість логічних схем навантаження, СI - 5 пФ

Монтажні ємкості усіх ланцюгів (См = 20 пФ).

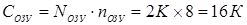

Згідно завдання кількість комірок ОЗП складає NОЗУ.

Розрядність ОЗП nОЗУ повинна відповідати розрядності обробки даних ЦП.

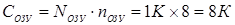

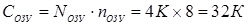

Інформаційна ємкість СОЗУ визначається по формулі:

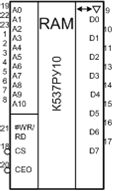

У якості мікросхеми ОЗП виберемо К537РУ10.

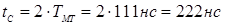

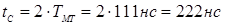

Необхідна швидкодія ОЗП визначається по тимчасовим діаграмам ЦП. Для МК ATmega128 тривалість циклу запису (зчитування) tС равно 2ТМТ, де ТМТ - тривалість машинного такту.

При частоті кварцевого резонатора fтг = 9 МГц тривалість tС дорівнює:

Тривалість циклу мікросхеми пам’яті tcy повинна задовольняти нерівності:

Мікросхему ОЗП виберемо К537РУ10, тому що вона ідеально підходить і не створює збитковості для даного випадку. Для цієї мікросхеми пам’яті ємкість 2К, а розрядність слова 8 біт:

.

.

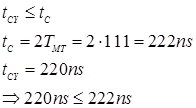

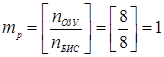

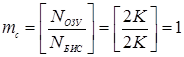

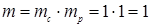

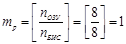

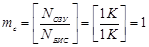

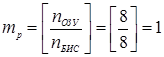

Розрахуємо число ВІС ОЗП в ряду матриці:

де nБИС - розрядність обраної мікросхеми пам’яті.

Визначимо число розрядів стовбців матриці:

де NБИС - кількість комірок обраної мікросхеми пам’яті.

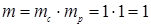

Загальна кількість ВІС ОЗП дорівнює:

Таким чином, кількість корпусів ОЗП дорівнює 1.

Визначимо струмове IDL и IDH і ємкістне СD навантаження для схем вводу інформації в ОЗП по формулам:

IDL = mc * IIDL = 1 * 1,6 = 1,6 мА

IDH = mc * IIDH = 1 * 0,1 = 0,1 мА

CD = mc * CID + Cm = 1 * 5 + 20 = 25 пФ

де IIDL, IIDH - вхідні струми логічного 0 і логічної 1 по інформаційним ланцюгам обраної ВІС ОЗП.

CID - вхідна ємкість по інформаційному входу ВІС ОЗП.

Визначимо стум навантаження і ємкістне навантаження для схем вводу адреси по ланцюгам адресу ВІС ОЗП по формулам:

IAL = m * IIAL = 1 * 1,6 = 1,6 мА

IAH = m * IIAH = 1 * 0,1 = 0,1 мА

CA = m * CIA + Cm = 1 * 5 + 20 = 25 пФ

де IIАL, IIAH - вхідні токи логічного 0 і логічної 1 по ланцюгам адресу обраної ВІС ОЗП.

CIА - вхідна ємкість по входу адресу ВІС ОЗП.

Визначимо струми навантаження ICSL, ICSH і величину ємкісного навантаження СCS по ланцюгам вибору мікросхем (CS) по формулам:

ICSL = mp * IICSL = 1 * 1,6 = 1,6 мА

ICSH = mp * IICSH = 1 * 0,1 = 0,1 мА

CCS = mp * CICS + Cm = 1 * 5 + 20 = 25 пФ

де IICSL, IICSH - вхідні струми логічного 0 і логічної 1 по ланцюгам вибору (CS) ВІС ОЗП.

CСS - вхідна ємкість по ланцюгам вибору мікросхем (CS) ВІС ОЗП.

Значення ICSL, ICSH и CCS не повинні перевищувати максимально допустимі значення для обраних мікросхем, що забезпечують вибір ВІС ОЗП.

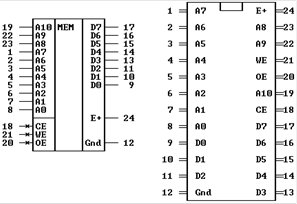

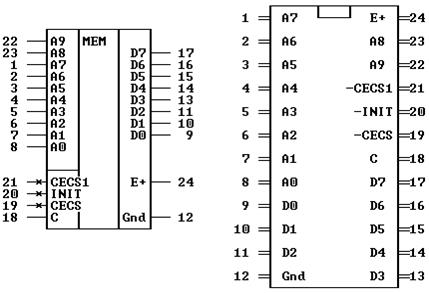

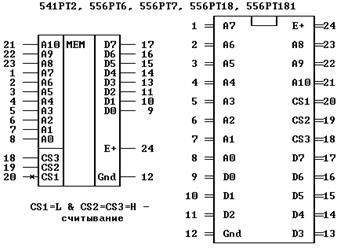

Рис.6 Умовно графічне позначення ОЗП К537РУ10

Найменування виводів:

A0 ÷ A10 - адресні входи.

W/R - запис/зчитування.

CS1 - chip select, чіп вибору.

CEO - виход дозволу.

D0 ÷ D7 - шина даних вводу/виводу.

ОЗП представляє собою статичний асинхронний оперативно запом’ятовуючий пристрій.

Режими роботи ОЗП:

| CS | OE | WR | A0. .10 | D0. .7 | Режим |

| M | X | X | Адрес | Дані | Зберігання |

| L | X | L | Запись | ||

| L | L | H | Зчитування | ||

| L | H | H | Заборона виходу |

Технологічні та електричні характеристики К537РУ10:

Технологія - КМОП

Організація - 2К×8

Час виборки, ns - не більш 220

Напруга живлення, V - 5

Струм живлення, мА

у режимі звернення - 30

у режимі зберігання - 1-2

Вхідна напруга, V

при логічному 0 - min 0 - max 0,4

при логічній 1 - min 0,9Ucc - max 0,5

Вихідна напруга, V

при логічному 0 - min 0 - max 0,4

при логічній 1 - min 2,4 - max 0,4

Вихід - 3 с.

Діапазон робочих температур, ºС - - 10 - +70

Розрахуємо ПЗП:

Оскільки по завданню необхідно створити ПЗП емкість 5К  8, то було прийнято рішення використати дві схеми емкістю 2К

8, то було прийнято рішення використати дві схеми емкістю 2К  8 та одну 1К

8 та одну 1К  8.

8.

Початкові дані для мікросхеми КР556РТ20 1К  8:

8:

Кількість комірок зовнішнього ПЗП NОЗУ - 1К×8

Вхідні струми:

при логічному 0, IIL - 0,25 мА

при логічній 1, IIH - 0,04 мА

Вхідна ємкість логічних схем навантаження, СI - 5 пФ

Монтажні ємкості усіх ланцюгов (См = 20 пФ).

Згідно завдання кількість комірок ПЗП складає NОЗУ.

Розрядність ПЗП nОЗУ повинна відповідати розрядності обробки даних ЦП.

Інформаційна ємкість СОЗУ визначається по формулі:

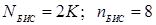

Необхідна швидкодія ПЗП визначається по тимчасовим діаграмам ЦП. Для МК ATmega128 тривалість циклу запису (зчитування) tС равно 2ТМТ, де ТМТ - тривалість машинного такту.

При частоті кварцевого резонатора fтг = 9 МГц тривалість tС дорівнює:

Тривалість циклу мікросхеми пам’яті tcy повинна задовольняти нерівності:

У якості мікросхеми ПЗП виберемо КР556РТ20, тому що вона ідеально підходить і не створює збитковості для даного випадку. Для даної мікросхеми пам’яті ємкість 1К, а розрядність слова 8 біт:

.

.

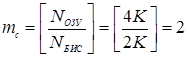

Розрахуємо число ВІС ПЗП в ряду матриці:

де nБИС - розрядність обраної мікросхеми пам’яті.

Визначимо число розрядів стовбців матриці:

де NБИС - кількість комірок обраної мікросхеми пам’яті.

Загальна кількість ВІС ПЗП дорівнює:

Таким чином, кількість корпусів ПЗП дорівнює 1.

Визначимо стум навантаження і ємкістне навантаження для схем вводу адреси по ланцюгам адресу ВІС ПЗП по формулам:

IAL = m * IIAL = 1 * 0,25 = 0,25 мА

IAH = m * IIAH = 1 * 0,04 = 0,04 мА

CA = m * CIA + Cm = 1 * 5 + 20 = 25 пФ

де IIАL, IIAH - вхідні токи логічного 0 і логічної 1 по ланцюгам адресу обраної ВІС ПЗП. CIА - вхідна ємкість по входу адресу ВІС ПЗП.

Визначимо струми навантаження ICSL, ICSH і величину ємкісного навантаження СCS по ланцюгам вибору мікросхем (CS) по формулам:

ICSL = mp * IICSL = 1 * 0,25 = 0,25 мА

ICSH = mp * IICSH = 1 * 0,04 = 0,04 мА

CCS = mp * CICS + Cm = 1 * 5 + 20 = 25 пФ

де IICSL, IICSH - вхідні струми логічного 0 і логічної 1 по ланцюгам вибору (CS) ВІС ПЗП.

CСS - вхідна ємкість по ланцюгам вибору мікросхем (CS) ВІС ПЗП.

Враховуючи, що на відміну від ОЗП інформація з ПЗП тільки зчитується, то необхідно визначити струми навантаження і ємкість навантаження на інформаційні виходи ВІС ПЗП по формулам:

IQL = mР * IIL = 1 * 0,25 = 0,25 мА

IQH = mР * IIH = 1 * 0,04 = 0,04 мА

CQ = mC * CQO + mР *CI + Cm = 1 * 5 + 1 * 5 + 20 = 30 пФ

де IQL, IQH - вхідні струми логічного 0 і логічної 1 мікросхем навантаження ВІС ПЗП, CQO - вихідна ємкість одного інформаційного виходу ВІС ПЗП, CI - вхідна ємкість мікросхем навантаження ВІС ПЗП.

Отримані значення струмів не повинні перевищувати граничні значення для обраних мікросхем пам’яті.

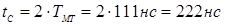

Рис.7 Умовно графічне позначення ПЗП КР556РТ20

Найменування виводів:

A0 ÷ A9 - адресні входи.

D0 ÷ D7 - шина даних вводу/виводу.

CECS, CECS1 - вибір мікросхеми

Технологічні та електричні характеристики КР556РТ20:

Технологія - ТТЛШ

Організація - 1К×8

Час виборки, ns - не більш 65

Напруга живлення, V - 5

Струм живлення, мА - 180 мА

Вхідна напруга, V

при логічному 0 - min 2,4 - max 0,5

при логічній 1 - min 2,4 - max 0,5

Вихідна напруга, V

при логічному 0 - min 2,4 - max 0,5

при логічній 1 - min 2,4 - max 0,5

Вихід - 3 с.

Потужність споживання, mW - 875

Діапазон робочих температур, ºС - - 10 - +70

Початкові дані для мікросхеми КР556РТ18 2К  8:

8:

Кількість комірок зовнішнього ПЗП NОЗУ - 4К×8

Вхідні струми:

при логічному 0, IIL - 0,25 мА

при логічній 1, IIH - 0,04 мА

Вхідна ємкість логічних схем навантаження, СI - 5 пФ

Монтажні ємкості усіх ланцюгів (См = 20 пФ).

Згідно завдання кількість комірок ПЗП складає NОЗУ.

Розрядність ПЗП nОЗУ повинна відповідати розрядності обробки даних ЦП. Інформаційна ємкість СОЗУ визначається по формулі:

Необхідна швидкодія ПЗП визначається по тимчасовим діаграмам ЦП. Для МК ATmega128 тривалість циклу запису (зчитування) tС равно 2ТМТ, де ТМТ - тривалість машинного такту. При частоті кварцевого резонатора fтг = 9 МГц тривалість tС дорівнює:

Тривалість циклу мікросхеми пам’яті tcy повинна задовольняти нерівності:

У якості мікросхеми ПЗП виберемо КР556РТ20, тому що вона ідеально підходить і не створює збитковості для даного випадку. Для даної мікросхеми пам’яті ємкість 1К, а розрядність слова 8 біт:

.

.

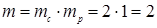

Розрахуємо число ВІС ПЗП в ряду матриці:

де nБИС - розрядність обраної мікросхеми пам’яті. Визначимо число розрядів стовбців матриці:

де NБИС - кількість комірок обраної мікросхеми пам’яті.

Загальна кількість ВІС ПЗП дорівнює:

Таким чином, кількість корпусів ПЗП дорівнює 2.

Визначимо стум навантаження і ємкістне навантаження для схем вводу адреси по ланцюгам адресу ВІС ПЗП по формулам:

IAL = m * IIAL = 2 * 0,25 = 0,50 мА, IAH = m * IIAH = 2 * 0,04 = 0,08 мА

CA = m * CIA + Cm = 2 * 5 + 20 = 30 пФ

де IIАL, IIAH - вхідні токи логічного 0 і логічної 1 по ланцюгам адресу обраної ВІС ПЗП.

CIА - вхідна ємкість по входу адресу ВІС ПЗП.

Визначимо струми навантаження ICSL, ICSH і величину ємкісного навантаження СCS по ланцюгам вибору мікросхем (CS) по формулам:

ICSL = mp * IICSL = 1 * 0,25 = 0,25 мА

ICSH = mp * IICSH = 1 * 0,04 = 0,04 мА

CCS = mp * CICS + Cm = 1 * 5 + 20 = 25 пФ

де IICSL, IICSH - вхідні струми логічного 0 і логічної 1 по ланцюгам вибору (CS) ВІС ПЗП.

CСS - вхідна ємкість по ланцюгам вибору мікросхем (CS) ВІС ПЗП.

Враховуючи, що на відміну від ОЗП інформація з ПЗП тільки зчитується, то необхідно визначити струми навантаження і ємкість навантаження на інформаційні виходи ВІС ПЗП по формулам:

IQL = mР * IIL = 1 * 0,25 = 0,25 мА

IQH = mР * IIH = 1 * 0,04 = 0,04 мА

CQ = mC * CQO + mР *CI + Cm = 2 * 5 + 1 * 5 + 20 = 35 пФ

де IQL, IQH - вхідні струми логічного 0 і логічної 1 мікросхем навантаження ВІС ПЗП, CQO - вихідна ємкість одного інформаційного виходу ВІС ПЗП, CI - вхідна ємкість мікросхем навантаження ВІС ПЗП.

Отримані значення струмів не повинні перевищувати граничні значення для обраних мікросхем пам’яті.

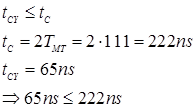

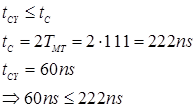

Рис.8 Умовно графічне позначення ПЗП КР556РТ18

Найменування виводів:

A0 ÷ A10 - адресні входи.

D0 ÷ D7 - шина даних вводу/виводу.

CS1 ÷ СS3 - вибір мікросхеми

Технологічні та електричні характеристики КР556РТ20:

Технологія - ТТЛШ

Організація - 2К×8

Час виборки, ns - не більш 60

Напруга живлення, V - 5

Струм живлення, мА - 180 мА

Вхідна напруга, V

при логічному 0 - min 2,4 - max 0,5

при логічній 1 - min 2,4 - max 0,5

Вихідна напруга, V

при логічному 0 - min 2,4 - max 0,5

при логічній 1 - min 2,4 - max 0,5

Вихід - 3 с.

Потужність споживання, mW - 875

Діапазон робочих температур, ºС - - 10 - +70

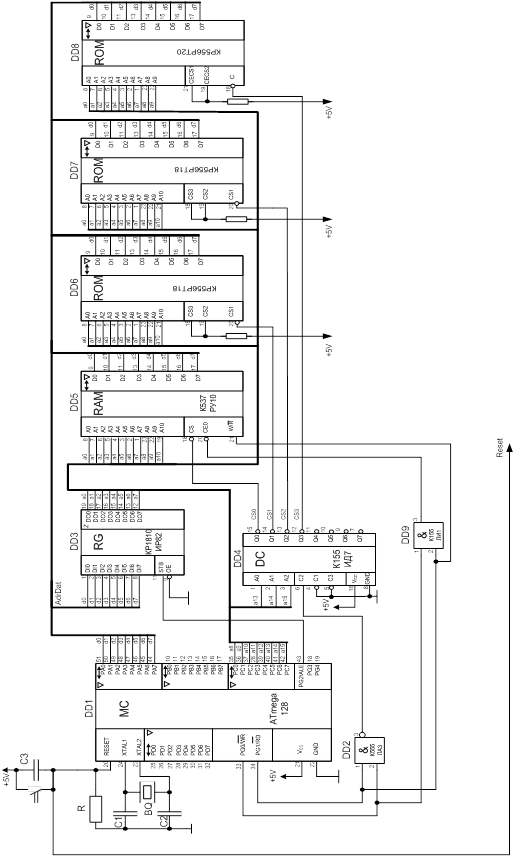

Рис.9 - Схема підключення процесорного блоку і пам’яті

Інтервальний таймер

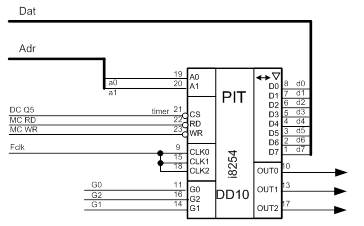

Одним з елементів, обумовлених завданням, є інтервальний таймер i8254. Таймер призначений для формування затримок послідовності імпульсів, формування одиночних імпульсів заданої тривалості, формування стробуємих імпульсів із програмованою затримкою. Виконаний по n-МОП технології.

Рис.10 - Умовне графічне позначення таймеру i8254

D0 - D7 - двонаправлена шина даних з високоімпедансним станом.

А0 - А1 - розряди шини даних, визначають регістр, що буде адресуватися: А1А0 = 00 - адреса каналу 0; А1А0 = 01 - адреса каналу 1; А1А0 = 10 - адреси каналу 2; А1А0 = 11 - адреса регістра керуючого слова

- вибір кристала

- вибір кристала

- сигнал запису

- сигнал запису

- сигналу читання

- сигналу читання

CLK0 - CLK2 - вхід дозволу подачі імпульсу від зовнішнього джерела

GATE0 - GATE2 - вхід дозволу подачі імпульсу сlk на таймер/лічильник

OUT0 - OUT2 - вихід таймерів/лічильників

Вхідні сигнали CLK0 - CLK2 подаються через схеми із зовнішніми керуючими входами GATE0 - GATE2. Кожен лічильник має вихідний сигнал OUT. Інші вузли схеми призначені для установки режиму й реалізації інтерфейсу із системною шиною.

Для функціонування таймера мікроконтролер повинен завантажити керуючі слова, значення яких позначають режим кожного лічильника, і необхідні початкові значення. У завданні нам дані параметри для програмування таймера, тому ми проініціализуємо його в розділі розробки програм ініціалізації.

Електричні параметри i8254:

1. Напруга живлення - 5 В

2. Вихідна напруга:

високого рівня - 2,4 В

низькі рівні - 0,5 В

3. Вихідний струм високого рівня - 1 мА

4. Вихідний струм низького рівня - 5 мА

5. Вхідний струм високого рівня - 30 мкА

6. Вхідний струм низького рівня - 30 мкА

Рис.11 - Схема підключення таймера i8254

Дата: 2019-07-31, просмотров: 422.