Основний елемент системи - мікроконтролер ATmega128, ATmega128L 8-розрядний AVR-мікроконтролер з внутрісистемно програмованою флэш-пам'яттю ємкістю 128 кбайт

Відмітні особливості:

Високопродуктивний, малопотужний 8-розрядний AVR-мікроконтролер Розвинена RISC-архітектура.

133 могутніх інструкцій, більшість з яких виконуються за один машинний цикл.

32 8-разр. регістрів загального призначення + регістри управління вбудованою периферією.

Повністю статична робота.

Продуктивність до 16 млн. операцій в секунду при тактовій частоті 16 Мгц

Вбудований умножаючий пристрій виконує множення за 2 машинних циклу.

Незалежна пам'ять програм і даних.

Зносостійкість 128-ми кбайт внутрісистемно перепрограмміруємой флэш-пам'яті: 1000 циклів запис/стирання.

Опціональний завантажувальний сектор з окремим програмованим захистом.

Внутрішньосистемне програмування вбудованою завантажувальною програмою.

Гарантована двухоперационность: можливість читання під час запису

Зносостійкість 4 кбайт ЕСППЗУ: 100000 циклів запис/стирання

Вбудоване статичне ОЗУ ємкістю 4 кбайт

Опціональна можливість адресації зовнішньої пам'яті розміром до 64 кбайт.

Програмований захист коду програми.

Інтерфейс SPI для внутрішньосистемного програмування.

Інтерфейс JTAG (сумісність із стандартом IEEE 1149.1).

Граничне сканування відповідно до стандарту JTAG.

Обширна підтримка функцій вбудованої відладки.

Програмування флэш-пам'яті, ЕСППЗУ, біт конфігурації і захисту через інтерфейс JTAG.

Відмітні особливості периферійних пристроїв.

Два 8-разр. таймера-лічильника з роздільними переддільниками і режимами порівняння.

Два розширених 16-разр. таймера-лічильника з окремими переддільниками, режимами порівняння і режимами захоплення.

Лічильник реального часу з окремим генератором.

Два 8-разр. каналів ШИМ.

6 каналів ШИМ з програмованим дозволом від 2 до 16 розрядів

Модулятор виходів порівняння.

8 мультіплексованих каналів 10-розрядного аналогово-цифрового перетворення.

8 несиметричних каналів.

7 диференціальних каналів

2 диференціальних каналу з вибірковим посиленням з 1x, 10x і 200x

Двухпроводної послідовний інтерфейс, орієнтований не передачу даних в байтному форматі

Два канали програмованих послідовних УСАПП.

Послідовний інтерфейс SPI з підтримкою режимів ведучий/підлеглий.

Програмований сторожовий таймер з вбудованим генератором.

Вбудований аналоговий компаратор.

Спеціальні можливості мікро контролера.

Скидання при подачі живлення і програмована схема скидання при зниженні напруги живлення.

Вбудований RC-генератор, що калібрується.

Зовнішні і внутрішні джерела переривань.

Шість режимів зниження енергоспоживання: холостий хід (Idle), зменшення шумів АЦП, економічний (Power-save), виключення (Power-down), черговий (Standby) і розширений черговий (Extended Standby)

Програмний вибір тактової частоти

Конфігураційний біт для перекладу в режим сумісності з ATmega103

Загальне виключення підтягаючих резисторів на всіх лініях портів введення-виводу

Уведення-виведення і корпуси

53 програмуємі лінії введення-виводу

64-выв. корпус TQFP

Робоча напруга

2.7 - 5.5В для ATmega128L

4.5 - 5.5В для ATmega128

Градації по швидкодії

0 - 8 Мгц для ATmega128L

0 - 16 Мгц для ATmega128

Короткий огляд:

ATmega128 - малопотужний 8-разр. КМОП мікроконтролер, заснований на розширеній RISC-архітектурі AVR. За рахунок виконання більшості інструкцій за один машинний цикл ATmega128 досягає продуктивності 1 млн. операцій в секунду/МГц, що дозволяє проектувальникам систем оптимізувати співвідношення енергоспоживання і швидкодії.

Ядро AVR поєднує багатий набір інструкцій з 32 універсальними робочими регістрами. Все 32 регістри безпосередньо підключено до арифметико-логічного пристрою (АЛУ), який дозволяє вказати два різні регістри в одній інструкції і виконати її за один цикл. Дана архітектура володіє більшою ефективністю коду за рахунок досягнення продуктивності в 10 разів вище в порівнянні із звичайними CISC-мікроконтролерами.

ATmega128 містить наступні елементи: 128 кбайт внутрісистемно програмованої флэш-пам'яті з підтримкою читання під час запису, 4 кбайт ЕСППЗУ, 4 кбайт статичного ОЗУ, 53 лінії універсального введення-виводу, 32 універсальні робочі регістра, лічильник реального часу (RTC), чотири гнучкі таймери-лічильники з режимами порівняння і ШИМ, 2 УСАПП, двухпроводний послідовний інтерфейс орієнтований на передачу байт, 8-канальний 10-разр. АЦП з опціональним диференціальним входом з програмованим коефіцієнтом посилення, програмований сторожовий таймер з внутрішнім генератором, послідовний порт SPI, випробувальний інтерфейс JTAG сумісний із стандартом IEEE 1149.1, який також використовується для доступу до вбудованої системи відладці і для програмування, а також шість програмно вибираних режимів зменшення потужності. Режим холостого ходу (Idle) зупиняє ЦПУ, але при цьому підтримуючи роботу статичного ОЗУ, таймерів-лічильників, SPI-порту і системи переривань. Режим виключення (Powerdown) дозволяє зберегти вміст регістрів, при зупиненому генераторі і виключенні вбудованих функцій до наступного переривання або апаратного скидання. У економічному режимі (Power-save) асинхронний таймер продовжує роботу, дозволяючи користувачеві зберегти функцію відліку часу в той час, коли решта частини контроллера знаходиться в стані сну. Режим зниження шумів АЦП (ADC Noise Reduction) зупиняє ЦПУ і всі модулі введення-виводу, окрім асинхронного таймера і АЦП для мінімізації імпульсних шумів в процесі перетворення АЦП. У черговому режимі (Standby) кварцевый/резонаторный генератор продовжують роботу, а решта частини мікроконтролера знаходиться в режимі сну. Даний режим характеризується малою споживаною потужністю, але при цьому дозволяє досягти найшвидшого повернення в робочий режим. У розширеному черговому режимі (Extended Standby) основний генератор і асинхронний таймер продовжують працювати.

Мікроконтролер проводиться за технологією високощільної незалежної пам'яті компанії Atmel. Вбудована внутрісистемно програмована флэш-пам'ять дозволяє перепрограмувати пам'ять програм безпосередньо усередині системи через послідовний інтерфейс SPI за допомогою простого програматора або за допомогою автономної програми в завантажувальному секторі. Завантажувальна програма може використовувати будь-який інтерфейс для завантаження прикладної програми у флэш-пам'ять. Програма в завантажувальному секторі продовжує роботу в процесі оновлення прикладної секції флэш-пам'яті, тим самим підтримуючи двухоперационность: читання під час запису. За рахунок поєднання 8-разр. RISC ЦПУ з внутрісистемно самопрограммируемой флэш-пам'яттю в одній мікросхемі ATmega128 є могутнім мікроконтролером, що дозволяє досягти високого ступеня гнучкості і ефективної вартості при проектуванні більшості додатків вбудованого управління. ATmega128 підтримується повним набором програмних і апаратних засобів для проектування, в т. ч.: Сі-компілятори, макроасемблери, програмні отладчики/симуляторы, внутрішньосистемні емулятори і оцінні набори.

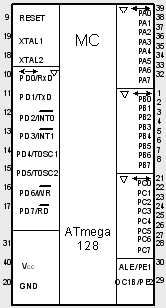

Умовне графічне позначення мікроконтроллера ATmega128 наведено на рис.2.

Рис.2 Умовне графічне позначення мікроконтроллера ATmega128

Найменування виводів ATmega128:

| VCC | вивід джерела споживання |

| RESET | вхід системного скидання |

| XTAL1, XTAL2 | виводи для підключення кварцевого резонатору |

| РА0 ÷ РА7 | 8-розрядний двунаправлений порт А вводу/виводу з третім станом, при роботі з зовнішньою пам’яттю являється суміщеною шиною адреси даних (адрес необхідно по сигналу ALE занести в регістр) |

| PB0 ÷ PB7 | 8 - розрядний двунаправлений порт В вводу/виводу з третім станом, який має альтернативні функції |

| OC0/ТО (РВО) | вход зовнішнього сигналу таймера/лічильника ТО або виход таймера/лічильника ТО в режимах Compare, PWM |

| OC2/Т1 (РВ1) | вхід зовнішнього сигналу таймера/лічильника Т1 |

| AIN0 (PB2) | позитивний вхід компаратору |

| AIN1 (PB3) | негативний вхід компаратору |

| SS (PB4) | вибір підлеглого пристрою (slave) на шині SPI (послідовний інтерфейс) |

| MOS1 (PB5) | виход головного (master) чи вхід підлеглого (slave) пристрою даних модуля SPI |

| MІS0 (PB6) | вхід головного (master) чи вихід підлеглого (slave) пристрою даних модуля SPI |

| SCK (РВ7) | виход головного (master) чи вхід підлеглого (slave) пристрою тактового сигналу модуля SPI |

| PC0 ÷ PC7 | 8 - розрядний двунаправлений порт С вводу/виводу з третім станом, має альтернативну функцію - передає старший байт адреси (А8÷А15) при роботі з зовнішньою пам’яттю |

| PD0÷PD7 | 8 - розрядний двунаправлений порт D вводу/виводу з третім станом, має альтернативні функції |

| RxD0 (PD0) | вхід приймача універсального асинхронно послідовного порта (USART) |

| TxD0 (PD1) | виход передавальника універсального асинхронно послідовного порта (USART) |

| INT0 (PD2) | вхід зовнішнього переривання 0 |

| INT1 (PD3) | вхід зовнішнього переривання 1 |

| XCK0 (PD4) | вхід/вихід зовнішнього сигналу синхронізації (тактового сигналу USART) |

| OC1A (PD5) | виход А таймера/лічильника Т1 в режимі порівняння (Compare) і в режимі шин сигнала (PWM) |

| WR (PD6) | строб запису у зовнішнє ОЗП |

| RD (PD7) | строб читання із зовнішнього ОЗП |

| РЕ0÷РЕ2 | 3-розрядний двунаправлений порт Е вводу/виводу с третім сстаном, має альтернативні функції |

| РЕ0 (INT2) | вхід зовнішнього переривання 2 |

| ICP1 | вхід захвату таймера/лічильника Т1 (режим Compare) |

| РЕ1 (ALE) | строб адреси зовнішнього ОЗУ, записується адрес в регістр-заклямку |

| PE2 (OC1B) | вихід В таймера/лічильника Т1 в режимі Compare и PWM |

| GND | загальний вивід |

Електричні характеристики

Гранично-допустимі параметри

| Робоча температура | -55°C…+125°C |

| Температура зберігання | -65°C…+150°C |

| Напруга на будь-якому виводі по відношенню до загального пі-танія, окрім RESET | -1.0В … VCC+0.5В |

| Напруга на виводі скидання RESET по відношенню до об-щему | -1.0В … +13.0В |

| Максимальна робоча напруга | 6.0В |

| Постійний струм через лінію введення-виводу | 40.0 мА |

| Постійний струм через виводи VCC і GND | 200.0 мА |

Статичні характеристики

| Обозн. | Параметр | Умови вимірювання | Мин. | Ном. | Макс. | Ед. изм. |

| VIL | Вхідна напруга низького рівня | Окрім виводів XTAL1 і RESET | -0.5 | 0.2 VCC (1) | В | |

| VIL1 | Вхідна напруга низького рівня | виведення XTAL1, ви-брана зовнішня син-хронізация | -0.5 | 0.1 VCC (1) | В | |

| VIL2 | Вхідна напруга низького рівня | виведення скидання RESET | -0.5 | 0.2 VCC (1) | В | |

| VIH | Вхідна напруга високого рівня | Окрім виводів XTAL1, RESET | 0.6 VCC (2) | VCC + 0.5 | В | |

| VIH1 | Вхідна напруга високого рівня | Виведення XTAL1, ви-брана зовнішня син-хронізация | 0.7 VCC (2) | VCC + 0.5 | В | |

| VIH2 | Вхідна напруга високого рівня | Виведення скидання RESET | 0.85 VCC (2) | VCC + 0.5 | В | |

| VOL | Вихідна напруга низького рівня (3) (порты A,B,C,D, E, F, G) | IOL = 20 мА, VCC = 5В IOL = 10 мА, VCC = 3В | 0.7 0.5 | В | ||

| VOH | Вихідна напруга високого рівня (4) (порты A,B,C,D) | IOH = - 20 мА, VCC = 5В IOH = - 10 мА, VCC = 3В | 4.0 2.2 | В | ||

| IIL | Вхідний струм витоку через лінію введення-виводу | Vcc = 5.5В, лог.0 (абс. значение) | 8.0 | мкА | ||

| IIH | Вхідний струм витоку через лінію введення-виводу | Vcc = 5.5В, лог.1 (абс. значение) | 8.0 | мкА | ||

| RRST | Опір подтягивающего резистора на вході скидання | 30 | 100 | кОм | ||

| RPEN | Опір подтягивающего резистора на вході PEN | 25 | 100 | кОм | ||

| RPU | Опір подтягивающего резистора на лініях введення-виводу | 20 | 100 | кОм | ||

| ICC | Споживаний струм | 4 МГц, VCC = 3В, активний режим (ATmega128L) | 5 | мА | ||

| 8 МГц, VCC = 5В, активний режим (ATmega128) | 20 | мА | ||||

| 4 МГц, VCC = 3В, режим холостого хода (ATmega128L) | 2 | мА | ||||

| 8 МГц, VCC = 5В, режим холостого хода (ATmega128) | 12 | мА | ||||

| Режим виключення (Power-down) (5) | Стор. таймер включен, VCC = 3В | < 25 | 40 | мкА | ||

| Стор. таймер отключен, VCC = 3В | < 10 | 25 | мкА | |||

| VACIO | Вхідна напруга зсуву аналогового компаратора | VCC = 5В Vвх = VCC/2 | 40 | мВ | ||

| IACLK | Вхідний струм витоку аналогового компаратора | VCC = 5В Vвх = VCC/2 | -50 | 50 | нА | |

| tACID | Затримка на ініциалізацію аналогового компаратора | VCC = 2.7В VCC = 5.0В | 750 500 | нс | ||

| tACID | Затримка распространенію сигналу в аналоговому компараторі | VCC = 2.7В VCC = 5.0В | 750500 | нс |

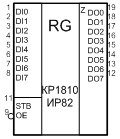

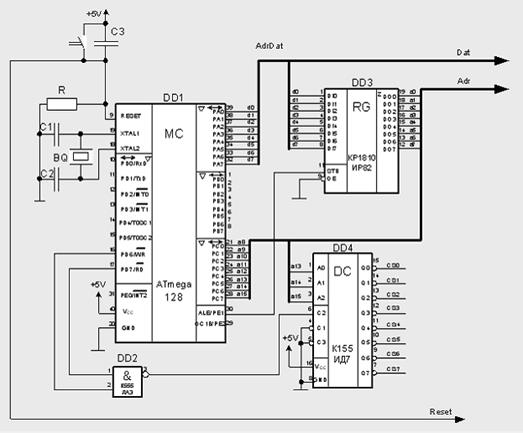

Завдяки тому, що шина даних і адреси в МК ATmega128 сполучені й мають поділ тільки в часі, то для їхнього поділу будемо використати регістр із третім станом К1810ИР82 для зберігання адреси.

Восьмирозрядні буферні регістри К1810ИР82 використовуються для організації запам'ятовуючих пристроїв, портів уводу-виводу, мультиплексорів і т.п. Буферні регістри складаються із восьми тригерів Т з виходними схемами 5Ш з трьома станами.

Формувач має дві групи - А і В виводів, а також два керуючих виводи - SТB та ОЕ. Дозвіл передачі залежить від рівня сигналу на виводі ОЕ, а напрямок передачі визначається рівнем сигналу на виводі Т.

Електричні параметри К1830ИР82.

Вхідний струм низького рівня не більше 0,2 мА

Вхідний струм високого рівня не більше 50 мкА

Вихідна напруга низького рівня не більше 0,45 В при струмі 32мА

Вихідна напруга високого рівня не меньше 2,4 В при струмі 1мА

Рис.3 - Умовне графічне позначення К1830ИР82

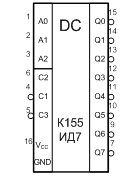

Для створення адресації зовнішніх пристроїв використовується дешифратор 3-8. На входи якого потрапляють молодші розряди адреси, а на виході установлюються сигнали вибору кристалу мікросхеми.

Рис.4 - Умовне графічне позначення К155ИД7

В цій мікро ЄОМ присутні пять зовнішніх пристроїв. Таким чином селектор адреси повинен бути більше ніж на пять розрядів, а також він повинен мати інверсні виходи для керування виборкою кристалів які також інверсні. Вище приведений (SN74138N) повністю задовольняє цим вимогам.

Розробка фізичних адрес зовнішніх пристроїв:

| А13 | А14 | А15 | CS | Назва пристрою | Фізична адреса | |

| 0 | 0 | 0 | 0 | RAM1 (2K) | 0000H-1FFFH | |

| 1 | 0 | 0 | 1 | ROM1 (2K) | 2000H-3FFFH | |

| 0 | 1 | 0 | 2 | ROM2 (2K) | 4000H-5FFFH | |

| 1 | 1 | 0 | 3 | ROM3 (1K) | 6000H-7FFFH | |

| 0 | 0 | 1 | 4 | ККіІ | 8000Н | |

| 1 | 0 | 1 | 5 | АЦП | A000Н | |

| 0 | 1 | 1 | 6 | Інтервальний таймер | C000Н | |

| 1 | 1 | 1 | 7 | Послідовний інтерфейс | E000H | |

Рис.5 - Схема підключення процесорного блоку

Дата: 2019-07-31, просмотров: 317.