§ Одним из наиболее полезных свойств C166 является поддержка нескольких режимов конфигурации, когда, например, выборка кода и данных из внешней памяти осуществляется по 16-разрядной демультиплексной шине с нулевым ожиданием, а доступ к медленной периферии (часы RTC) из соображений экономии может происходить по 8-разрядной шине с 3 состояниями ожидания. В первом случае шина управляется регистром конфигурации BUSCON0, а во втором случае - регистрами конфигурации BUSCON1 и ADDRESEL1, которые определяют режим шины и адресный диапазон соответственно.

§ В ряде микроконтроллеров (C165 и C167) присутствует до четырех независимых дополнительных регистров конфигурации BUSCON1-BUSCON4, каждому из которых соответствует свой внешний вывод CS для соединения с входом разрешения выборки кристалла. Размер и начальный адрес диапазона для каждого сигнала CS1-CS4 задается в регистрах ADDRSEL1-ADDRSEL4. При задании областей действия сигналов CS необходимо помнить, что начальный адрес должен быть кратен размеру блока. Например, для блока размером 64 Кбайт, начальный адрес должен быть равен 0x00000 или 0x10000 или 0x20000 и т.д.

§ Характеристики системной шины для областей памяти, не перекрываемых данными четырьмя адресными диапазонами, задаются в регистре BUSCON0 и устанавливаются аппаратно при считывании линий порта 0 во время сброса, т.е. сигнал CS0 используется для адресации всех областей не определенных сигналами CS1-CS4.Кроме того, для экономии внешней логики присутствуют программируемые сигналы управления шиной. Это означает, что при более чем 20-кратном выигрыше в производительности проект с С166 получается проще, чем для 8031. С166 содержит также программируемые функции арбитража шины HOLD/HOLDA/BREQ для операций межпроцессорного обмена.

§ Непосредственное управление внешней шиной в соответствии с содержимым регистров конфигурации осуществляет контроллер внешней шины. В каждом диапазоне временные параметры циклов чтения-записи и режим работы системной шины задаются специальными битами в регистрах конфигурации. Ширина адресной шины может составлять в зависимости от кристалла 16 (для несегментированного режима), 18 (80C166), 22 (C164) и 24 (C165 и С167) разряда. Ширина шины данных может быть 8 или 16 разрядов, и работа может вестись в мультиплексном и демультиплексном (MUX и NMUX) режимах (у C161 и C164 предусмотрена только мультиплексная внешняя шина). Демультиплексный шинный интерфейс оптимален при высоких требованиях к времени обращения к внешним ОЗУ и ПЗУ. Как уже отмечалось, режимы работы шины могут динамически меняться в процессе выполнения программы. Сравнение скорости работы для различных конфигураций шины при частоте ЦПУ 20 МГц приведено в таблице

Система прерываний

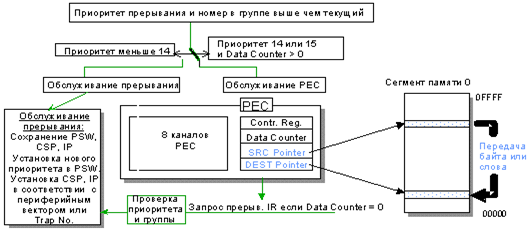

§ Разветвленная схема прерываний C166 с 64 уровнями (16 уровней и на каждом уровне группа из 4 прерываний) обеспечивает гибкое и быстрое

§ задание приоритетов и обслуживание запросов прерываний (рисунок 3.4). В контроллере прерываний предусмотрены аппаратные ловушки (Hardware-Traps) и программные ловушки (Software-Traps), позволяющие обрабатывать ошибки, возникающие при неверном исполнении команд, нарушении границ стека, а также отслеживать немаскируемое прерывание NMI, программный и аппаратный сброс. Приоритеты прерываний от аппаратных и программных ловушек самые высокие.

§ Контроллер прерываний обеспечивает малое время отклика на запрос прерывания: минимальное время составляет 250 нс @20 МГц, а максимальное - 600 нс. Чтобы уменьшить время отклика при выполнении сложных команд умножения и деления, занимающих 5 и 10 циклов соответственно, также предусмотрено прерывание. Обработка прерываний осуществляется в течение малых временных интервалов. Это очень важно для высокоуровневых приложений, таких как управление приводами, когда решаются задачи цифровой обработки сигналов и весьма нежелательны флуктуации входных и выходных переменных. Таким образом, достигается высокая производительность в реальном масштабе времени.

§ Механизм обработки прерываний работает следующим образом. Для каждого прерывания имеется собственный регистр управления Interrupt Control Register (xxIC). При установке одного или нескольких флагов запроса прерывания Interrupt Request (IR) в регистрах управления xxIC производится сравнение их приоритетов с текущим приоритетом выполняемой программы, который содержится в регистре состояния процессора. После проверки номера в группе в регистре прерывания с наибольшим номером уровня и группы очищается флаг IR, и контроллер приступает к обработке этого прерывания. При этом в стеке автоматически сохраняется содержимое регистра состояния процессора PSW, указателя команд IP и в сегментированном режиме указателя сегмента CSP и загружаются новые значения этих регистров согласно

§ процедуре обработки прерывания.

Рисунок 3.4 – Схема прерываний

Регистрация внешних прерываний может осуществляться в альтернативном режиме по внешним входам, например, по входам Capture. Кроме того, имеется немаскируемое прерывание NMI. Часть внешних прерываний регистрируются каждые 0,5 цикла, т.е. каждые 50 нс @ 20 МГц.

§ Изменение уровня приоритета прерывания во время исполнения программы является достаточно типичной задачей для ряда приложений. Например, уровень приоритета может зависеть от значения сигнала на внешнем входе. В этом случае после проверки состояния входа процедура обслуживания прерывания переключает уровень прерывания на более низкий, изменяя содержимое регистра ILVL. После понижения уровня выполняемого прерывания могут поступить запросы на прерывание с более высоким приоритетом. Такая ситуация может привести к определенным проблемам.

Пусть, например, выполняется прерывание A на уровне 10 и поступает запрос от прерывания B с уровнем 12, которое и поступает на выполнение. Если теперь уровень прерывания B будет снижен до значения меньшего, чем 10, прерывание A не сможет стать активным пока не закончится выполнение B. Возможен еще более плохой вариант, если прерывание B снизит свой уровень до значения 5, и теперь даже прерывание C с уровнем 7 сможет его прервать. Такие ситуации

§ удлиняют время исполнения прерывания A, что не соответствует его новому приоритету. Поэтому для понижения уровня приоритета текущего прерывания всегда следует закончить текущую задачу, и начать новую с более низким приоритетом. Это можно осуществить при установке бита IR в каком-либо незадействованном регистре управления xxIC.

§ Контроллер периферийных событий - Peripheral Events Controller (PEC) освобождает ЦПУ от простых, но частых обслуживаний прерываний, осуществляя перенос данных в любую позицию нулевого сегмента без переключения задачи. Процесс переноса данных практически не затрагивает работу контроллера и не зависит от выполняемой программы - контроллер только приостанавливает выполнение текущей программы на один цикл (100 нс), даже не сохраняя свое состояние в стеке. Время отклика контроллера для обслуживания PEC составляет от 150 до 450 нс при цикле ЦПУ 100 нс. Для контроллера PEC отведены два верхних уровня приоритета, что позволяет обслуживать одновременно 8 каналов PEC. Каждый канал управляется собственным регистром PEC, который позволяет программировать передачу байта или слова данных с инкрементом адреса или без него с однократным, многократным или бесконечным числом пересылок. Обработка прерываний PEC выполняется в соответствии с приведенной диаграммой ( рисунок 3.5).

Рисунок 3.5 – Диаграмма прерываний

Генерация системного такта

§ Временной дискретой для ядра C166 является период такта, равный 50 нс при тактовой частоте 20 МГц. Большая часть команд C166 исполняются за два такта, т.е. за 100 нс. Для достижения номинального быстродействия внутренний такт должен иметь скважность 50%, что не всегда может быть получено при тактировании от кварцевого резонатора. При несовпадении длительностей высокого и низкого уровня тактового сигнала временная дискрета определяется по длительности самого короткого уровня, который должен быть не меньше 50 нс. Это означает, что при асимметрии такта понижается максимально возможная тактовая частота. Например, при длительности высокого уровня 50 нс, а низкого - 60 нс рабочая частота равна 18 МГц. Кроме требования симметричности времена переключения уровней тактового сигнала должны быть не более 5 нс.

§ Поэтому для генерации полностью симметричного системного такта в состав некоторых микроконтроллеров семейства C166 входит встроенный делитель входной частоты на 2. В этом случае требуется кварцевый генератор, работающий на частоте 40 МГц. Члены семейства, имеющие в маркировке индекс 'W' не содержат делителя и тактируются непосредственно. Без делителя сегодня выпускаются только кристаллы 8xC166W, с которыми рекомендуется работать на тактовой частоте 18 МГц.

§ В новых кристаллах C163, C164CI, C167 присутствует встроенное устройство PLL, которое преобразует входную частоту во внутренний системный такт с коэффициентом умножения 0.5, 1, 1.5, 2, 2.5, 3, 4 и 5. Например, при использовании кварцевого генератора 5 МГц для достижения обычных 20 МГц на встроенном устройстве PLL осуществляется умножение входной частоты на 4. Задание режима PLL осуществляется на фазе сброса при подключении резистора между входом P0L и нулем. При потере внешнего такта генерируется

§ прерывание, и PLL продолжает работать на частоте 5...10 МГц. Внутренний такт отслеживается PLL также в режимах прямого тактирования и деления входной частоты на 2.

| P0H.7 | P0H.6 | P0H.5 | Коэффиц. умножения | Фактор PLL | Делитель | Комментарий |

| 1 | 1 | 1 | 4 | 4 | OFF | по умолчанию |

| 1 | 0 | 1 | 2 | 2 | OFF | |

| 1 | 1 | 0 | 3 | 3 | OFF | |

| 1 | 0 | 0 | 5 | 5 | OFF | |

| 0 | 1 | 1 | W | OFF | OFF | прямой такт |

| 0 | 0 | 1 | 0.5 | OFF | ON | через делитель |

| 0 | 1 | 0 | 1.5 | 3 | ON | |

| 0 | 0 | 0 | 2.5 | 5 | ON |

Дата: 2019-07-30, просмотров: 352.