Регистр для хранения n-разрядного слова может быть построен на синхронных RS-триггерах.

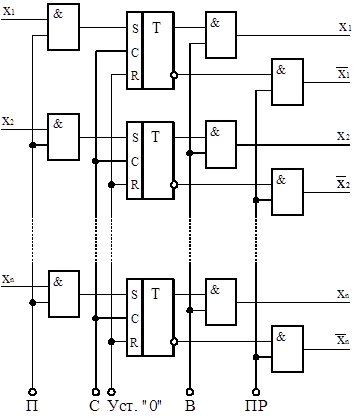

Рис.3.1 Функциональная схема регистра хранения.

В схеме регистра предусмотрены цепи, обеспечивающие выполнение дополнительных, вспомогательных микроопераций. Объединение входов R каждого триггера общей шиной образует шину гашения (Уст.0). Для установки триггера в состояние ноль необходимо падать одновременно сигналы соответствующие 1 по шине Уст.0 и шине С, объединяющей синхронизирующие входы триггеров.

Цепь параллельного приёма кода х1, х2,..., хn представлена конъюнкторами, выходы которых связаны с установочными входами S триггеров. Входы этих конъюнкторов объединены общей шиной П. Для осуществления операции “приём” предварительно регистры устанавливаются в состояние 0. После этого принимаемый код х1, х2,..., хn подаётся на входы конъюнкторов. Затем подаётся сигнал, соответствующий 1 по шинам П и С. В разрядах, где xi=1, происходит установка триггеров в единичное состояние. В разрядах, где xi=0, состояние триггеров не изменяется.

Операция “выдача” реализуется с помощью конъюнкторов, на входы которых поступают сигналы с прямых выходов триггеров. Вторые входы этих конъюнкторов объединены общей шиной выдачи В. Подавая сигнал 1 по шине В, получают на выходах конъюнкторов прямой код х1, х2,..., хn.

Операция “преобразование” осуществляется при подаче сигнала 1 по шине ПР, которая объединяет конъюнкторы, управляемые инверсными выходами триггеров, на выходе конъюнкторов при этом появляется обратный код

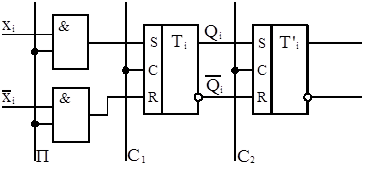

Рис.3.2 Схема парафазной передачи

В регистрах используются также парафазный приём и выдача информации. При этом не требуется предварительной установки в 0 элемента хранения при выполнении приёма.

Для приёма необходимо подать сигнал 1 на шинах С1 и П. Чтобы триггер Ti осуществлял хранение кода, достаточно исключить подачу сигнала по шине П.

Использование парафазной передачи позволяет совместить выдачу кода с одного регистра с приёма кода в другой регистр. Для этого осуществляется коммутация выхода Qi триггера Ti со входом S триггера T’i и выхода i триггера Ti со входом R триггера T’i. Для парафазной передачи кода с триггера Ti на триггер T’i достаточно подать сигнал по шине С2.

Регистры сдвига

Сущность сдвига состоит в том, что с приходом каждого тактового импульса происходит перезапись (сдвиг) содержимого триггера каждого разряда в соседний разряд без изменения порядка следования единиц и нулей.

При сдвиге информации вправо после каждого тактового импульса бит из более старшего разряда сдвигается в младший, а при сдвиге влево – наоборот.

Регистры сдвига, помимо операции хранения, осуществляет преобразование последовательного двоичного кода в параллельный, а параллельного – в последовательный, выполняют арифметические и логические операции, служат в качестве цифровых элементов временной задержки.

Регистры сдвига строят на синхронных двухступенчатых RS-, JK-триггерах или на асинхронных JK-, D-триггерах с динамическим управлением записью. Внутренняя организация таких триггерных схем предусматривает разделение во времени этапов приёма входной информации и смены выходной. В них по переднему фронту синхронизирующего сигнала происходит приём информации, а по заднему – изменение состояния.

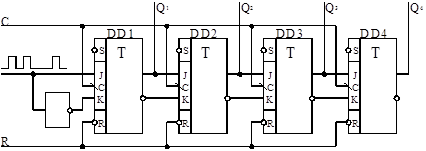

Рассмотрим работу четырёхразрядного регистра с последовательным вводом входной информации и сдвигом её вправо. В регистре применены RS(JK) - триггеры, а первый их них при помощи инвертора преобразован в D-триггер. Схема напоминает схему счётчика с параллельным переносом, но поскольку здесь применены не Т-триггеры, а RS(JK) - триггеры, то обеспечивается не счёт, а перенос (сдвиг) импульсов, поступающих на вход.

Допустим, что в регистр последовательно вводится, начиная с младшего разряда, двоичный код 1101, который поступает от внешнего устройства синхронно с тактовыми импульсами.

С первым тактовым импульсом в регистр DD1 будет записана единица младшего разряда. Со следующим тактовым импульсом эта единица будет сдвинута в триггер DD2 и окажется на его выходе. Одновременно в первый триггер поступит ноль (следующий разряд кода). Таким же образом будут происходить сдвиги с выхода Q2 на вход DD3 и с Q3 в DD4. После четырёх тактовых импульсов код на выходах Q4–Q1 будет соответствовать коду 1101 и может быть считан внешним устройством. Таким образом, регистр преобразует последовательный код в параллельный.

Рис.3.3 Четырёхразрядный сдвигающий регистр с последовательным вводом.

После очередного тактового импульса (пятого) информационный сигнал, бывший на выходе последнего триггера, выводится из регистра и пропадает.

На выходе Q4 каждый сигнал появляется через четыре такта, считая с момента подачи его на вход. Это свойство регистра сдвига часто используют для задержки цифровой информации на заданное число тактовых периодов.

Литература

1. Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. – Л.: Энергоатомиздат. Ленингр. отд-ние, 1986. – 280 с.

2. Каган Б.Н. Электронные вычислительные машины и системы: Учеб. пособие для вузов. – 2-е изд., перераб. и доп. – М.: Энергоатомиздат, 1985. – 552 с.

3. Проектирование импульсных и цифровых устройств радиотехнических систем: Учеб. пособие для радиотехн. спец. вузов / Гришин Ю.П., Казаринов Ю.М., Катиков В.М. и др.; Под редакцией Ю.М. Казаринова. – М.: Высшая школа, 1985. – 319 с.

4. Программное обеспечение микроЭВМ: Практическое пособие для инж.-пед. работников системы проф. -техн. образования. В 11кн. / Под редакцией В.Ф. Шаньгина. Кн.1. Структура и функционирование микроЭВМ. А.Е. Костин. – М.: Высшая школа, 1987. – 95 с.

5. Савельев А.Я. Прикладная теория цифровых автоматов: Учебник для вузов по специальности Эвм. – М.: Высшая школа, 1987. – 272 с.

6. Шило В.А. Популярные цифровые микросхемы: Справочник. – Челябинск: Металлургия, Челябинское отделение, 1988. – 352 с.

7. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник: В 2 Т. / Н.Н. Аверьянов, А.И. Березенко, Ю.И. Борщенко и др.; Под редакцией В.А. Шехнова. – М.: Радио и связь, 1988. – Т.2. – 368 с.

Дата: 2019-05-29, просмотров: 329.