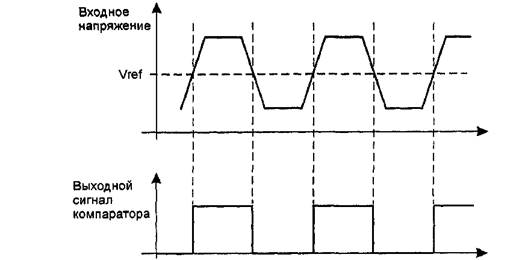

В ряде моделей микроконтроллеров AVR и PIC используется встроенный аналоговый компаратор напряжения, сравнивающий входное напряжение на двух входах. Как только напряжение на неинвентирующем входе станет больше, чем на инвентирующем, на выходе компаратора устанавливается лог. 1. Часто аналоговый компаратор используют для сравнения некоторого входного напряжения с опорным (рис. 8.4).

Для активизации компаратора требуется предварительно перевести соответствующие выводы микроконтроллера в режим входов. Время срабатывания компараторов небольшое, поэтому с их помощью можно быстро формировать ответные реакции на изменение соотношений входных напряжений.

В микроконтроллерах AVR входам компаратора AIN0 и AIN1 обычно соответствуют разряды 0/1 или 2/3 порта В. В микроконтроллерах PIC конфигурация входов компаратора (вывода порта А) настраивается с помощью разрядов регистра CMCON, о чем речь пойдет чуть позже.

В микроконтроллерах AVR для управления работой аналогового компаратора используется регистр ACSR (рис. 8.5), расположенный в области ввода/вывода по адресу 0x08 (адрес 0x28 в SRAM).

Рис. 8.4. Принцип работы аналогового компаратора напряжений

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ACD | – | ACO | ACI | ACIE | ACIC | ACIS1 | ACIS0 |

Рис. 8.5. Регистр ACSR микроконтроллеров AVR

Назначение разрядов регистра ACSR:

-ACD – если установлен в лог. 1, то питание аналогового компаратора отключено;

-АСО – напрямую связан с выходом аналогового компаратора;

-ACI – флаг прерываний от аналогового компаратора – устанавливается в лог. 1, когда наступает событие, определенное разрядами ACIS1 и ACIS0;

-ACIE – разряд разрешения прерывания от аналогового компаратора;

-ACIC – разряд разрешения захвата на входе аналогового компаратора; для того чтобы можно было вызвать прерывание по захвату, оно должно быть разрешено разрядом TICIE1 в регистре TIMSK;

-ACIS1, ACIS0 – устанавливают вид события на выходе аналогового компаратора, которое должно вызвать прерывание его работы (табл. 8.3).

Таблица 8.3. Вид событий для вызова прерывания от аналогового компаратора

| ACIS1 | AC1S0 | Вид прерывания аналогового компаратора |

| 0 | 0 | Прерывание при изменении состояния выхода (разряда АСО) |

| 0 | 1 | Не используется |

| 1 | 0 | Прерывание по ниспадающему фронту на выходе аналогового компаратора (напряжение на AIN1 больше, чем на AIN0) |

| 1 | 1 | Прерывание по нарастающему фронту на выходе аналогового компаратора (напряжение на AIN0 больше, чем на AIN1) |

В микроконтроллерах PIC могут использоваться два аналоговых компаратора – в частности, в серии Р1С16С62х. В этом случае для управления их работой предназначен регистр CMCON (рис. 8.6).

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| C2OUT | C1OUT | – | – | CIS | CM2 | CM1 | CM0 |

Рис. 8.6. Регистр CMCON микроконтроллеров серии Р1С16С62х

-СМ0-СМ2 – выбор режима работы компаратора (табл. 1.26);

-CIS – разряд управления входным коммутатором компаратора (табл. 8.4);

-C10UT – выходной сигнал компаратора 1;

-C20UT – выходной сигнал компаратора 2.

Таблица 8.4. Конфигурация входов компараторов напряжения в серии Р1С16С62х

| CIS | СМ2 | СМ1 | CM0 | Компаратор 1 | Компаратор 2 | ||

| Вход + | Вход– | Вход + | Вход– | ||||

| X | 0 | 0 | 0 | RA0 | RA3 | RA2 | RA1 |

| 0 | 0 | 0 | 1 | RA2 | RA0 | RA2 | RA1 |

| 1 | 0 | 0 | 1 | RA2 | RA3 | RA2 | RA1 |

| 0 | 0 | 1 | 0 | Vref | RA0 | Vref | RA1 |

| 1 | 0 | 1 | 0 | Vref | RA3 | Vref | RA2 |

| X | 0 | 1 | 1 | RA2 | RA0 | RA2 | RA1 |

| X | 1 | 0 | 0 | RA3 | RA0 | RA2 | RA1 |

| X | 1 | 0 | 1 | - | – | RA2 | RA1 |

| X | 1 | 1 | 0 | RA2 | RA0 | RA2 | RA1 |

| X | 1 | 1 | 1 | - | - | - | - |

Программирование микроконтроллеров AVR семейства Mega

Общие сведения

В общей сложности микроконтроллеры семейства Mega поддерживают следующие режимы программирования:

-режим последовательного программирования (по интерфейсу SPI);

-режим параллельного программирования при высоком напряжении;

-режим программирования через интерфейс JTAG.

Под “высоким” напряжением здесь понимается управляющее напряжение (12 В), подаваемое на вывод RESET микроконтроллера для перевода последнего в режим программирования.

Режимы программирования для конкретного микроконтроллера представлены в табл. 9.1.

Таблица 14.1. Режимы программирования микроконтроллеров семейства Mega

| Режим программирования | ATmega 8515x/8535x | ATmega 8x | ATmega 16x/32x | ATmega 64x/128x | ATmega 48x/88x/168x | ATmega 162x | ATmega 164x/324x ATmega 644x | ATmega 165x | ATmega 325x/3250x, ATmega 645x/6450x | ATmega 640x, ATmega 1280x/1281x, ATmega 2560x2561x |

| 1.Последовательное, по интерфейсу SPI | + | + | + | + | + | + | + | + | + | + |

| 2. Параллельное, при высоком напряжении | + | + | + | + | + | + | + | + | + | + |

| 3. По интерфейсу JTAG | + | + | + | + | + | + | + |

Кроме того, микроконтроллеры семейства Mega имеют возможность самопрограммирования. Под этим термином понимается изменение содержимого памяти программ, управляемое самим микроконтроллером.

В процессе программирования могут выполняться следующие операции:

-стирание кристалла (chip erase);

-чтение/запись FLASH-памяти программ;

-чтение/запись EEPROM-памяти данных;

-чтение/запись конфигурационных ячеек;

-чтение/запись ячеек защиты;

-чтение ячеек идентификатора;

-чтение калибровочного байта.

Все модели микроконтроллеров поставляются со стертой памятью программ и памятью данных (во всех ячейках находится число $FF) и пригодны к немедленному программированию.

Защита кода и данных

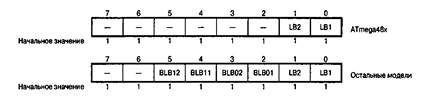

Содержимое FLASH-памяти программ, а также содержимое EEPROM-памяти данных может быть защищено от записи и/или чтения посредством программирования ячеек защиты (Lock Bits) LB1 и LB2. Возможные режимы защиты, соответствующие различным состояниям этих ячеек, приведены в табл. 8.2.

Таблица 8.2. Режимы защиты

| № режима | Ячейки защиты | Описание | |

| LB1 | LB2 | ||

| 1 | 1 | 1 | Защита кода и данных отключена |

| 2 | 0 | 1 | Запись FLASH и EEPROM запрещена |

| 3 | 0 | 0 | Запрещены запись и чтение FLASH и EEPROM |

В режимах 2 и 3 запрещается также изменение конфигурационных ячеек. Поэтому включение защиты следует выполнять в самую последнюю очередь, после программирования остальных областей памяти микроконтроллера.

Во всех микроконтроллерах семейства, кроме ATmega48x, имеется четыре дополнительные ячейки защиты — BLB02, BLB01, BLB12 и BLB11. Ячейки BLB02:BLB01 определяют уровень доступа из секции загрузчика к коду, расположенному в секции прикладной программы, а ячейки BLB12:BLB11, наоборот, определяют уровень доступа из секции прикладной программы к коду, расположенному в секции загрузчика. Отсутствие указанных ячеек в модели ATmega48x обусловлено отсутствием у последней выделенной секции загрузчика. Возможные режимы защиты, соответствующие различным состояниям этих ячеек, приведены в табл. 9.3 и табл. 9.4 соответственно.

Таблица 9.3. Режимы защиты секции прикладной программы

| № режима | Ячейки защиты | Описание | |

| BLB02 | BLB01 | ||

| 1 | 1 | 1 | Нет никаких ограничений по доступу к коду, расположенному в секции прикладной программы |

| 2 | 1 | 0 | Команда SPM не может осуществлять запись по адресам, находящимся в пределах секции прикладной программы |

| 3 | 0 | 0 | Команда SPM не может осуществлять запись по адресам, находящимся в пределах секции прикладной программы, и команда LPM (ELPM), вызываемая из секции загрузчика, не может осуществлять чтение из секции прикладной программы. Если таблица векторов прерываний расположена в секции загрузчика, то при выполнении кода из секции прикладной программы прерывания запрещены |

| 4 | 0 | 1 | Команда lpm (elpm), вызываемая из секции загрузчика, не может осуществлять чтение из секции прикладной программы. Если таблица векторов прерываний расположена в секции загрузчика, то при выполнении кода из секции прикладной программы прерывания запрещены |

Таблица 9.4. Режимы защиты секции загрузчика

| № режима | Ячейки защиты | Описание | |

| BLB12 | BLB11 | ||

| 1 | 1 | 1 | Нет никаких ограничений по доступу к коду, расположенному в секции загрузчика |

| 2 | 1 | 0 | Команда SPM не может осуществлять запись по адресам, находящимся в пределах секции загрузчика |

| 3 | 0 | 0 | Команда SPM не может осуществлять запись по адресам, находящимся в пределах секции загрузчика, и команда LPM (ELPM), вызываемая из секции прикладной программы, не может осуществлять чтение из секции загрузчика. Если таблица векторов прерываний расположена в секции прикладной программы, то при выполнении кода из секции загрузчика прерывания запрещены |

| 4 | 0 | 1 | Команда lpm (elpm), вызываемая из секции прикладной программы, не может осуществлять чтение из секции загрузчика. Если таблица векторов прерываний расположена в секции прикладной программы, то при выполнении кода из секции загрузчика прерывания запрещены |

Все перечисленные ячейки защиты сгруппированы в одном байте. Расположение ячеек защиты в нем для разных моделей приведено на Рис. 14.1.

Рис. 9.1. Байт ячеек защиты

В исходном (запрограммированном) состоянии во всех ячейках защиты содержится 1, после программирования – 0. Стирание ячеек (запись в них лог. 1) может быть произведено только при выполнении команды “Стирание кристалла”, уничтожающей также содержимое FLASH- и EEPROM-памяти.

Конфигурационные ячейки

Как следует из названия, конфигурационные ячейки (Fuse Bits) определяют различные параметры конфигурации микроконтроллера. Эти ячейки расположены в отдельном адресном пространстве, доступном только при программировании. Все конфигурационные ячейки сгруппированы в несколько байтов, а состав этих ячеек зависит от конкретной модели микроконтроллера. Наличие тех или иных ячеек в конкретном микроконтроллере можно определить по табл. 9.5, где в столбцах, отмеченных “звездочкой”, указаны состояния конфигурационных ячеек по умолчанию.

Краткое назначение всех конфигурационных ячеек приведено в табл. 9.6. Подробное описание их назначений было приведено в соответствующих главах книги.

Для изменения содержимого конфигурационных ячеек используются специальные команды программирования. Команда “Стирание кристалла” на состояние этих ячеек не влияет. Напоминаю, что при запрограммированной ячейке защиты LB1 конфигурационные ячейки блокируются. Поэтому конфигурацию микроконтроллера необходимо задавать до программирования ячеек защиты.

Таблица 9.5. Конфигурационные ячейки микроконтроллеров семейства

| Бит | ATmega8515x | ATmega8535x | ATmega8x | ATmegal6x/ 32x | ATtaega64x/ 128x | ATmega48x | ||||||

| Название | * | Название | * | Название | * | Название | * | Название | * | Название | * | |

Дата: 2019-05-28, просмотров: 340.