Для управления интерфейсом SPI в микроконтроллерах используются регистры SSPSTAT (рис. 7.9) и SSPCON1 (рис. 7.10).

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SMP | CKE | D/A | P | S | R/W | UA | BF |

Рис. 7.9. Регистр SSPSTAT микроконтроллеров PIC

Назначение разрядов регистра SSPSTAT:

-BF – флаг заполнения буфера данных;

-UA, R/W, S, P, D/A – имеют отношение к рассмотренному ниже последовательному интерфейсу ГС;

-СКЕ – выбор активного фронта импульсов SCK для передачи данных (используется совместно с разрядом СКР регистра SSPCON1, аналог в микроконтроллерах AVR – разряд SPHA регистра SPCR);

-SMP – точка стробирования данных в режиме Master (1 – стробирование в конце битового интервала; 0 – стробирование в середине интервала). В режиме Slave этот разряд всегда содержит лог. 0.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| WCOL | SSPOV | SSPEN | CKP | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

Рис. 7.10. Регистр SSPCON1 микроконтроллеров PIC

Назначение разрядов регистра SSPCON1:

-SSPM0-SSPM3 – выбор режима работы порта MSSP (значения для интерфейса SPI представлены в табл. 7.5);

-СКР – выбор фронта для передачи (аналог в микроконтроллерах AVR – разряд CPOL регистра SPCR); если СКР=0? то передача осуществляется по нарастающему фронту тактового сигнала;

-SSPEN – флаг разрешения работы интерфейса SPI;

-SSPOV – флаг переполнения приемного буфера;

-WCOL – флаг коллизий при записи (1 – запись новых данных в буферный регистр была произведена в момент передачи).

Таблица 7.5. Выбор режима работы порта MSSP для интерфейса SPI

| SSPM3 | SSPM2 | SSPM1 | SSPM0 | Режим |

| 0 | 0 | 0 | 0 | Режим Master, частота = Fosc / 4 |

| 0 | 0 | 0 | 1 | Режим Master, частота = Fosc /16 |

| 0 | 0 | 1 | 0 | Режим Master, частота = Fosc / 64 |

| 0 | 0 | 1 | 1 | Режим Master, частота = выход TMR2 / 2 |

| 0 | 1 | 0 | 0 | Режим Slave, вывод SS разрешен |

| 0 | 1 | 0 | 1 | Режим Slave, вывод SS не используется |

Синхронная передача данных по интерфейсу I2С

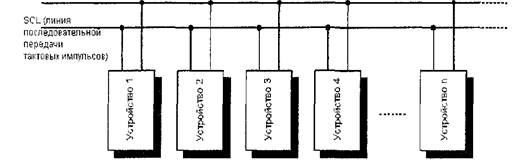

Интерфейс I2С (Inter-integrated Circuit), состоящий только из двух линий (SDA и SCL), предназначен для низкоскоростного последовательного обмена данными с периферийными устройствами, подсоединенных к одной общей шине (рис. 7.11).

Рис. 7.11. Подключение устройств к шине I2C

Характеристики шины I2С:

-работа только с двумя линиями, благодаря чему требуется меньше мест соединения и минимизируются затраты на проводку;

-зона действия – до 3 м;

-возможность работать в режиме с одним ведущим блоком (Single-Master) или с несколькими ведущими блоками (Multi-Master).

Линия SCL используется для передачи синхроимпульсов. Если данные не передаются, она содержит высокий уровень сигнала. Линия SDA используется для побитной передачи данных. Если данные не передаются, то она имеет высокий потенциал. Передаваемые данные действительны в фазе высокого уровня такта и могут менять свое состояние только в фазе низкого уровня.

Каждый блок, подсоединенный к шине, во время передачи данных может быть или приемником или передатчиком, а также ведущим (Master) или ведомым (Slave). Ведущее устройство инициирует передачу данных. В частности, Master занимает шину тем, что генерирует стартовый сигнал на линии SCL и начинает обмен с ведомым устройством. До тех пор, пока на шине работает ведущее устройство, не может быть активным никакой другой Master-блок.

Ведомым является устройство, по адресу которого обращается ведущее устройство с требованием передачи данных. Теоретически Master может одновременно снабжать одними и теми же данными несколько ведомых устройств. В роли ведущего устройства в большинстве случаев выступает микропроцессор, оборудованный или специальной аппаратной частью с шиной типа I2С, или контроллером шины, работающим под управлением специального программного обеспечения.

Протокол шины I2С

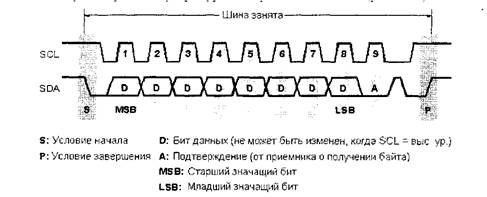

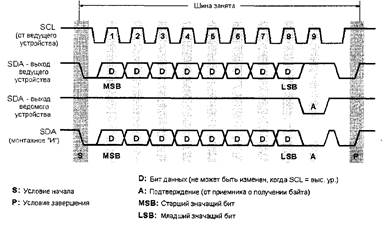

Для того чтобы несколько блоков могли обмениваться данными, необходим некоторый протокол, который описывает процесс передачи данных по шине и в любой момент времени не допускает ошибочной интерпретации состояния шины. В случае шины с несколькими ведущими устройствами (что относится и к I2С) необходимо также установить, когда и какое ведущее устройство имеет право занимать шину. Эти условия регулируются протоколом шины (рис. 7.12).

Рис. 7.12. Протокол передачи байта данных через шину I2C

Работа шины и ее занятость, определяется условием начала передачи – изменение ведущим устройством состояние линии SDA с высокого уровня на низкий. После наступления условия начала передачи шина будет занята ведущим устройством, создавшим это условие, вследствие чего все другие ведущие устройства будут заблокированы. Условие начала является однозначным состоянием на шине, потому что смена уровня сигнала на линии SDA, как правило, допускается только тогда, когда тактовая линия SCL находится в состоянии низкого уровня.

Все устройства, подключенные к шине, должны распознать условие начала передачи и переключаются на прием (ведомое устройство/приемник). Условие начала передачи также учитывается и другим ведущим устройством, которое со своей стороны имело намерение занять шину. В результате оно немедленно отзывает свое требование. Устройство, создавшее условие начала передачи, в данный момент времени является для шины ведущим (Master), а все остальные устройства – потенциальными ведомыми (Slave). Ведущее устройство теперь отвечает за тактовый сигнал и становится передатчиком.

После создания условия начала ведущее устройство начинает передачу данных. Оно переводит тактовую шину в состояние низкого уровня и теперь может занять линию передачи данных затребованным информационным разрядом (высокий или низкий уровень в линии SDA). Затем тактовая шина опять переводится в состояние высокого уровня.

Изменение в линии SDA может происходить только в фазе низкого уровня сигнала в линии SCL Во время фазы высокого уровня в линии SCL линия SDA должна быть стабильной.

Передача данных, как правило, выполняется побайтно, при этом первым передается старший разряд. После передачи полного байта данных, состоящей из восьми тактовых циклов, следует бит подтверждения от приемника.

Бит подтверждения (квитирования) – это реакция приемника на принятый байт данных. Он является для передатчика признаком того, что приемник физически присутствует и "прослушивает" линию. Одновременно с этим бит подтверждения можно рассматривать как сигнал синхронизации.

Бит подтверждения, как правило, генерируется приемником. Если ведущее устройство принимает от ведомого устройства несколько байтов данных, то оно квитирует каждый отдельный байт битом подтверждения, за исключением последнего. Такое отрицательное квитирование сообщает ведомому устройству, что передача данных завершена, и далее последует условие завершения или новое условие начала передачи.

Для передачи бита подтверждения ведущее устройство генерирует на линии SCL дополнительный тактовый импульс (рис. 7.13). Приемник выдает сигнал положительного квитирования, переводя линию SDA в состояние низкого уровня, или отрицательного квитирования, переводя линию SDA в состояние высокого уровня.

Рис. 7.13. Выработка бита квитирования приемником, работающим в режиме ведомого устройства

Таким образом, для передачи одного байта данных, как правило, требуется девять тактовых циклов. После передачи одного байта данных и приема бита подтверждения передача данных может быть сразу же продолжена. Если приемник реагирует на передачу байта данных отрицательным квитированием, то ведущее устройство должно завершить передачу данных, опять освободив шину.

Шина после окончания передачи данных, которая может состоять из любого количества байтов, опять освобождается ведущим устройством. Освобождение шины осуществляется с помощью условия завершения – изменение в линии SDA уровня сигнала с низкого на высокий в то время, когда по тактовой шине SCL передается сигнал высокого уровня.

После создания условия завершения передачи шина освобождается. Условие завершения передачи также представляет собой однозначное состояние на шине. Все блоки и устройства распознают его и подготавливаются к появлению нового условия начала передачи. В том случае, если ведущее устройство из-за промежуточной занятости шины отзывает свое требование занять шину, то оно может предпринять новую попытку создать условие начала передачи и тем самым получить шину для своих нужд.

Полная передача данных через шину I2С, в принципе, состоит из условия начала передачи, одного или нескольких байтов данных (за которыми, соответственно, следует бит квитирования), и условия завершения передачи.

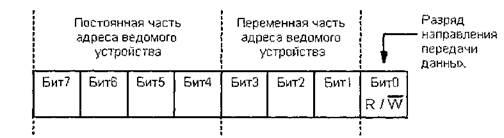

Адресация ведомых устройств

Выбор ведомого устройства, с которым хотело бы обмениваться данными ведущее устройство, осуществляется посредством первого байта, который всегда определяется как адрес ведомого устройства – первый байт последовательности данных. Он однозначно сопоставлен определенному устройству, подключенному к шине, и имеет длину 7 бит (разряды от 1 до 7). Теоретически, таким образом можно адресовать до 128 ведомых устройств, однако по определению некоторые адреса ведомых устройств имеют особое значение. Адрес ведомого устройства состоит из двух частей: постоянной и переменной (рис. 7.14).

Рис. 7.14. Формат адреса шины I2C

Постоянная часть адреса описывает требования к определенным группам устройств и определяется изготовителем. Его длина определена в результате практического опыта и в большинстве случаев составляет 4 бита. Он будет тем короче, чем больше однотипных устройств в схеме. Постоянная часть адреса жестко "прошита" в интегральной схеме и не может быть изменена пользователем.

Переменная часть адреса ведомого устройства служит для выбора определенного устройства из группы однотипных кристаллов, среди которых все имеют постоянную часть адреса ведомого устройства. Благодаря этому, к шине могут быть подсоединены несколько однотипных интегральных схем. Переменная часть

в большинстве случаев определяется пользователем с помощью внешних схем (через дополнительные выводы).

С помощью разрядов 1-7 адреса ведомого устройства однозначно идентифицируется требуемый ведомый блок. Разряд 0 задает направление передачи данных. Он определяет, должны ли быть приняты или переданы данные. Если разряд направления передачи данных содержит лог. 1 (чтение), то ведущее устройство находится в режиме приемника, а ведомое – в режиме передатчика. Если разряд направления передачи данных содержит лог. 0 (запись), то ведущее устройство будет работать как передатчик, а ведомое – как приемник.

Адрес ведомого устройства также подтверждается этим устройством с помощью бита квитирования. Если ведущее устройство после адресации получает отрицательное квитирование, то оно может заключить, что ведомое устройство или вообще отсутствует, или в настоящий момент с ним невозможно установить связь (например, оно занято обработкой заданий, критическими с точки зрения времени).

Работа с интерфейсом I2С в микроконтроллерах PIC

Интерфейс I2C аппаратно реализован не во всех микроконтроллерах AVR, однако, благодаря высокому допустимому значению тактовой частоты, возможна его организация с помощью программного обеспечения.

В микроконтроллерах PIC обмену данными по интерфейсу 12С соответствует особый режим работы порта MSSP. Линии SCL соответствует вывод 3 порта С, а линии SDA – вывод 4 того же порта.

Для управления передачей в режиме I2С используются три регистра: уже рассмотренные выше SSPSTAT (рис. 7.8) и SSPCON1 (рис. 7.9), а также SSPCON2 (рис. 7.10).

Назначение разрядов регистра SSPSTAT, имеющих отношение к 12С:

-BF – флаг заполнения буфера данных;

-UA – устанавливается в лог. 1 в том случае, если необходимо модифицировать адрес устройства (содержимое регистра SSPADD);

-R/W – указывает на тип операции: 0 – запись, 1 – чтение;

-S – устанавливается в лог. 1 при обнаружении условия начала передачи;

-Р – устанавливается в лог. 1 при обнаружении условия завершения передачи;

-D/A – признак переданного байта: 0 – байт адреса, 1 – байт данных. Назначение разрядов регистра SSPCON1, имеющих отношение к I2С:

-SSPM0-SSPM3 – выбор режима работы порта MSSP (значения для интерфейса I С представлены в табл. 7.6);

-СКР – установка этого разряда в лог. 1 разрешает тактирование;

-SSPEN – флаг разрешения работы интерфейса;

-SSPOV – флаг переполнения приемного буфера;

-WCOL – флаг коллизий при записи (1 – запись новых данных в буферный регистр была произведена в момент передачи).

Таблица 7.6. Выбор режима работы порта MSSP для интерфейса l2C

| SSPM3 | SSPM2 | SSPM1 | SSPMO | Режим |

| 0 | 1 | 1 | 0 | Режим Slave, используется 7-разрядный адрес |

| 0 | 1 | 1 | 1 | Режим Slave, используется 10-разрядный адрес |

| 1 | 0 | 0 | 0 | Режим Master, частота = F0sc / (4 (SSPADD + 1)) |

| 1 | 0 | 1 | 1 | Режим Master с программным управлением |

| 1 | 1 | 1 | 0 | Режим Slave, используется 7-разрядный адрес |

| 1 | 1 | 1 | 1 | Режим Slave, используется 10-разрядный адрес |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| GCEN | ACKSTAT | ACKDT | ACKEN | RCEN | PEN | RSEN | SEN |

Рис. 7.15. Регистр SSPCON2 микроконтроллеров PIC

Назначение разрядов регистра SSPCON2:

-SEN – устанавливается в лог. 1 для создания условия начала передачи;

-RSEN – устанавливается в лог. 1 для создания повторных условий начала передачи;

-PEN – сбрасывается в лог. О для создания условия окончания передачи;

-RCEN – устанавливается в лог. 1 для разрешения режима приема;

-ACKEN – инициирует последовательность битов квитирования;

-ACKDT – устанавливается в лог. 1 для отправки подтверждения при приеме байта;

-ACKSTAT – устанавливается в лог. 1 при получении подтверждения приема от ведомого устройства.

Модуль шины CAN

Когда осуществляется обмен данными между несколькими устройствами по одной общей шине, существует вероятность возникновения самых разнообразных ошибок. Кроме того, возникают сложности с адресацией. В системе, состоящей из двух устройств, все очень просто: одно устройство передает данные, а другое опрашивает шину и принимает данные. В случае же с несколькими устройствами, требуется определить, какое именно из них передает данные и какому из устройств, подключенных к общей шине. Все это обусловливает необходимость в некотором протоколе обмена данными.

Протокол определяет метод адресации, проверку ошибок и общий формат данных для всех устройств, использующих шину. Один из таких протоколов – протокол CAN (Controller Area Network), поддерживаемый рядом микроконтроллеров семейства PIC18 и некоторыми последними разработками компании Atmel.

3. Аналого-цифровое преобразование

Число в цифровой форме определяется на основании отношения входного напряжения к полному номиналу напряжения аналого-цифрового преобразователя (АЦП). Например, если на вход АЦП с номинальным напряжением 5 В подать напряжение 1 В„ то на цифровом выходе появится число, соответствующее 1/5=0,2 разрешающей способности преобразователя. Так, если используется АЦП с разрешением 8 бит, то максимальное возможное значение на его выходе 2 - 1 = 255. Таким образом, напряжению 1 В на аналоговом входе соответствует 0,2 - 255 = 51 на цифровом выходе.

Встроенные АЦП микроконтроллеров AVR и PIC имеют разрешение 10 бит и позволяют считывать напряжение на одном из восьми (в некоторых моделях – пяти) аналоговых входов (обычно – порт А).

В микроконтроллерах AVR для управления режимом АЦП используются два регистра: регистр управления ADCSR (рис. 8.1) и регистр мультиплексирования ADMUX (определяет, какие из восьми входов порта А являются аналоговыми).

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ADEN | ADSC | ADFR | ADIF | ADIE | ADPS2 | ADPS1 | ADPS0 |

Рис. 8.1. Регистр ADCSR микроконтроллеров AVR

Назначение разрядов регистра ADCSR:

-ADPS0 – ADPS2 – выбор коэффициента деления тактовой частоты (табл. 8.1); чем выше частота работы АЦП (производная от частоты системной синхронизации), тем ниже эффективное разрешение, поэтому следует устанавливать коэффициент деления;

-ADIE – разряд маскирования прерывания от АЦП (1 – по окончанию преобразования разрешено прерывание);

-ADIF – флаг прерывания от АЦП (устанавливается аппаратно по окончанию цикла преобразования);

-ADFR – лог. 1 в этом разряде переводит АЦП в несинхронизированный режим работы – обычно АЦП работает в режиме прерывания, чтобы процессор каждый раз не ожидал завершения медленно протекающего преобразования, однако в несинхронизированном режиме АЦП выполняет преобразование постоянно, как можно быстрее (на период такого преобразования должны быть запрещены все прерывания);

-ADSC – флаг начала преобразования;

-ADEN – флаг разрешения использования АЦП.

Таблица 8.1. Выбор коэффициента деления частоты системной синхронизации для тактирования АЦП микроконтроллеров AVR

| ADPS2 | ADPS1 | ADPS0 | Коэффициент деления |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 2 |

| 0 | 1 | 0 | 4 |

| 0 | 1 | 1 | 8 |

| 1 | 0 | 0 | 16 |

| 1 | 0 | 1 | 32 |

| 1 | 1 | 0 | 64 |

| 1 | 1 | 1 | 128 |

Таким образом, в общем случае процесс аналого-цифрового преобразования в микроконтроллерах AVR протекает следующим образом:

-установить в лог. 1 разряды регистра ADMUX, соответствующие аналоговым входам;

-установить разряды 0-2 регистра ADCSR для выбора коэффициента деления частоты системной синхронизации;

-установить в лог. 1 разряд ADIE для разрешения режима прерывания;

-установить в лог. 1 разряд ADEN, чтобы разрешить использование АЦП;

-установить в лог. 1 разряд ADSC, чтобы начать преобразование;

-результат преобразования сохраняется в регистровой паре ADCL, ADCH;

В микроконтроллерах PIC для управления работой встроенного АЦП также используются два регистра: ADCON0 (рис. 8.2) и ADCON1 (рис. 8.3).

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ADCS1 | ADCS0 | CHS2 | CHS1 | CHS0 | GO/DONE | ADIF | ADON |

Рис. 8.2. Регистр ADCON0 микроконтроллеров PIC

Назначение разрядов регистра ADCON0:

-ADON – флаг разрешения использования АЦП;

-ADIF – разряд запроса на прерывание по окончанию преобразования;

-GO/DONE – установка этого разряда в лог. 1 активизирует АЦП; по окончанию преобразования автоматически сбрасывается в лог. 0;

-CHS0-CHS2 – выбор аналогового входа порта А (назначение этих разрядов зависит от типа микроконтроллера);

-ADCS0-ADCS1 – выбор рабочей частоты АЦП (табл. 1.24).

Таблица 8.2. Выбор рабочей частоты АЦП микроконтроллеров PIC

| ADCS1 | ADCS0 | Частота |

| 0 | 0 | Частота системной синхронизации / 2 |

| 0 | 1 | Частота системной синхронизации / 8 |

| 1 | 0 | Частота системной синхронизации / 32 |

| 1 | 1 | Тактирование от встроенного RC-осциллятора АЦП (250 кГц) |

Максимальная допустимая рабочая частота АЦП микроконтроллеров PIC – 625 кГц. Это следует учитывать при выборе коэффициента деления частоты системной синхронизации.

Использование внутреннего RC-осциллятора АЦП не рекомендуется для микроконтроллеров с частотой системной синхронизации выше 1 МГц.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ADFM | – | – | – | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

Рис. 8.3. Регистр ADC0N1 микроконтроллеров PIC

Назначение разрядов регистра ADCON1;

-PCFG0-PCFG3 – разряды конфигурации – определяют, какие выводы порта АЦП являются аналоговыми входами, а какие используются для подачи опорных напряжений Vref+ и Vref–; наиболее распространенная конфигурация: 0000, которая определяет все 8 выводов аналоговыми входами, а в качестве опорных напряжений – напряжения VDD и Vss; другие значения разрядов PCFG0-PCFG3 варьируются в зависимости от типа микроконтроллера;

-ADFM – выбор разрешения преобразования: 1 – 10 бит; 0 – 8 бит.

Результат преобразования сохраняется в регистровой паре ADRESL, ADRESH, причем в регистре ADRESH используются только младшие два разряда в случае преобразования с разрешением 10 бит.

Таким образом, в общем случае процесс аналого-цифрового преобразования в микроконтроллерах PIC протекает следующим образом:

-определить с помощью разрядов регистра ADCON1 конфигурацию преобразования;

-установить разряды 6-7 регистра ADCON0 для выбора рабочей частоты АЦП;

-установить разряды 3-5 регистра ADCON0 для выбора аналогового канала;

-установить в лог. 1 разряды ADON и GO регистра ADCON0, чтобы начать преобразование;

-дождаться окончания преобразования (лог. 0 в разряде DONE регистра ADCON0) и считать результат из регистровой пары ADRESLL, ADRESH.

Дата: 2019-05-28, просмотров: 374.