Интерфейс SPI (Serial Peripheral Interface) служит для обмена данными с периферийными устройствами. В качестве таких устройств могут выступать простые сдвиговые регистры или буквенно-цифровые модули индикации, а также сложные микропроцессорные системы или системы регистрации данных. Многие компании-изготовители предлагают большой выбор устройств с интерфейсом SPI.

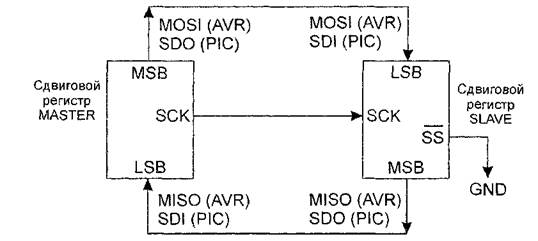

В случае обмена данными по интерфейсу SPI микроконтроллер работает в режиме ведущего устройства (Master), взаимодействуя с одним или несколькими ведомыми блоками (Slave). Схема передачи данных по интерфейсу SPI микроконтроллеров AVR/PIC показана на рис. 7.6 (MSB – старший разряд, a LSB – младший разряд передаваемого байта).

Рис. 7.6. Схема передачи данных по интерфейсу SPI микроконтроллеров AVR/PIC

Ведущее устройство берет на себя активную часть обмена данными, вызывая передачу и управляя процессом. Ведомое устройство не может само быть активным. Оно принимает и передает данные только тогда, когда происходит его активизация со стороны ведущего устройства по линии /SS. Ведущее устройство также генерирует такт для передачи по выходной линии SCK. Для ведомого блока вывод SCK является входом, через который он получает от Master-устройства тактирующие сигналы.

Если ведомое устройство активизируется ведущим по линии /SS, то начинается обмен данными: Master записывает подлежащий передаче байт в свой сдвиговой регистр данных (для микроконтроллеров AVR – регистр SPDR, для микроконтроллеров PIC – регистр SSPBUF). С помощью каждого выработанного тактового импульса Master перемещает один бит данных на выход MOSI/SDO, a Slave одновременно в обратном направлении передает один бит на вход MISO/SDI ведущего блока. Таким образом, в течение цикла SPI, состоящего из восьми тактовых импульсов, Master и Slave обмениваются байтом данных.

По окончании передачи данных в регистре состояния интерфейса SPI устанавливается флаг соответствующего запроса на прерывание. Этот флаг указывает на окончание передачи и вызывает запрос на прерывание после того как в регистре управления SPI будет установлен разряд разрешения на прерывание от интерфейса SPI. В режиме "Master" текущая передача данных может быть преждевременно завершена выдачей в линию /SS сигнала лог. 1.

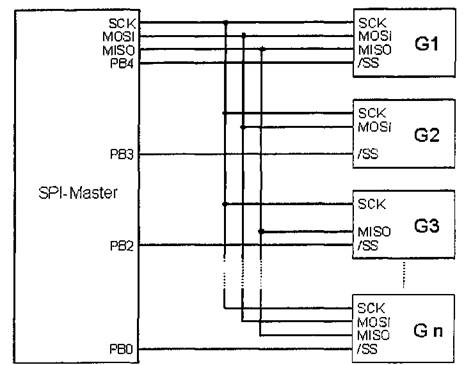

К интерфейсу SPI ведущего устройства можно подключать несколько ведомых устройств (пример для микроконтроллеров AVR – на рис. 7.7), однако активным будет только то из них, на вход /SS которого будет подан уровень лог. 0. Выходы MISO незадействованных ведомых блоков находятся в высокоомном состоянии и не влияют на процесс передачи данных.

В примере на рис. 7.7 устройство G2, с точки зрения ведущего устройства, является только блоком передачи (например, ЦАП с интерфейсом SPI), а устройство G3 – только блоком приема.

Рис. 7.7. Подключение нескольких ведомых устройств к одному ведущему по SPI (для AVR)

В микроконтроллерах AVR в качестве линий SPI используются выводы порта В (табл. 7.2). В микроконтроллерах PIC для последовательной синхронной передачи данных используется порт MSSP, работающий в режиме интерфейса SPI или I2С. Линиям SPI соответствуют выводы порта А и С (табл. 7.2).

Таблица 7.2. Распределение выводов портов для линий интерфейса SPI

| Линия | Микроконтроллеры AVR | Микроконтроллеры PIC |

| /SS | Разряд 4 порта В | Зависит от модели (например, разряд 5 порта А) |

| MOSI (SDO) | Разряд 5 порта В | Разряд 5 порта С |

| MISO(SDI) | Разряд 6 порта В | Разряд 4 порта С |

| SCK | Разряд 7 порта В | Разряд 3 порта С |

Дата: 2019-05-28, просмотров: 412.