· ЗУ с произвольным доступом. Цикл обращения таких устройств не зависит от того, в каком физическом месте находятся требуемые данные. Такой способ доступа характерен для полупроводниковых ЗУ. Число записанных одновременно битов данных за одно обращение называют шириной выборки (доступа).

· ЗУ с прямым доступом. В таких ЗУ носитель информации непрерывно вращается (HDD, CD-ROM), в результате требуемые данные доступны для чтения-записи через некоторый фиксированный промежуток времени. Такие ЗУ называют «ЗУ циклического типа».

· ЗУ с последовательным доступом. При последовательном доступе прежде че найти нужный участок ЗУ нужно «просмотреть» либо все предыдущие участки памяти, либо предыдущий (последний) участок памяти (накопитель на магнитной ленте).

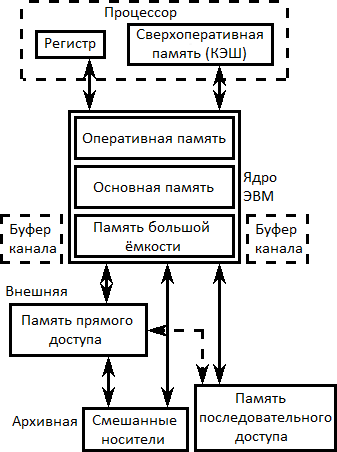

Требования, которые предъявляются к ёмкости и быстродействию памяти являются противоположными с точки зрения технического исполнения (если память быстрая, то ёмкость мала и наоборот). Поэтому в современных ЭВМ память строится в виде иерархической структуры.

На любом модуле памяти может быть несколько однотипных модулей ЗУ.

Основная память обеспечивает хранение информации, которая непосредственно используется процессором (АЛУ или УУ) в ходе выполнения программы. Основная память напрямую связана с процессором и, следовательно, её характеристики влияют на производительность ЭВМ в целом. Быстродействие памяти меньше быстродействия процессора примерно в 4-5 раз.

Для того чтобы убрать этот дисбаланс используется промежуточная кэш-память с большим быстродействием, но с меньшей ёмкостью.

Чтобы описать некоторый уровень иерархии памяти, нужно ответить на 4 вопроса:

1. Где может размещаться блок (минимальная единица информации) на верхнем уровне иерархии (размещение блока)?

2. Как найти блок, когда он находится на верхнем уровне (идентификация блока)?

3. Какой блок должен быть замещён в случае промаха (замещение блоков)?

4. Что происходит во время записи (стратегия записи)?

Организация кэш-памяти

Рассмотрим организацию кэш-памяти более детально, отвечая на 4 вопроса об иерархии памяти.

Принципы размещения блоков в кэш-памяти определяют три основных типа их организации:

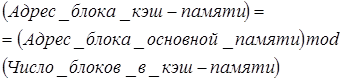

1. Если каждый блок основной памяти имеет только одно фиксированное место, на котором он может появиться в кэш-памяти, то такая кэш-память называется кэшем с прямым отображением (direct mapping). Это наиболее простая организация кэш-памяти, при которой для отображения адресов блоков основной памяти на адреса кэш-памяти просто используются младшие разряды адреса блока. Таким образом все блоки основной памяти, имеющие одинаковые младшие разряды в своём адресе попадают в один блок кэш-памяти.

2. Если некоторый блок основной памяти может располагаться на любом месте кэш-памяти, то кэш называется полностью ассоциативным (fully associative).

3. Если некоторый блок основной памяти может располагаться на ограниченном множестве мест в кэш-памяти, то кэш называется множественно-ассоциативным (set associative). Обычно множество представляет собой группу из двух или большего числа блоков в кэше. Если множество состоит из n блоков, то такое размещение называется множественно-ассоциативным с n каналами (n-way set associative). Для размещения блока прежде всего необходимо определить множество. Множество определяется младшими разрядами адреса блока памяти (индексом):

Далее блок может размещаться на любом месте данного множества.

Диапазон возможных организаций кэш-памяти очень широк: кэш-память с прямым отображением есть просто одноканальная множественно-ассоциативная кэш-память, а полностью ассоциативная кэш-память с  блоками может быть названа

блоками может быть названа  -канальной множественно-ассоциативной. В современных процессорах как правило используется либо кэш-память с прямым отображением, либо двух- (четырех-) канальная множественно-ассоциативная кэш-память.

-канальной множественно-ассоциативной. В современных процессорах как правило используется либо кэш-память с прямым отображением, либо двух- (четырех-) канальная множественно-ассоциативная кэш-память.

У каждого блока в кэш-памяти имеется адресный тэг, указывающий, какой блок в основной памяти данный блок кэш-памяти представляет. Эти тэги обычно одновременно сравниваются с выработанным процессором адресом блока памяти.

Кроме того, необходим способ определения того, что блок кэш-памяти содержит достоверную или пригодную для использования информацию. Наиболее общим способом решения этой проблемы является добавление к тэгу так называемого бита достоверности (valid bit).

Адресация множественно-ассоциативной кэш-памяти осуществляется путём деления адреса, поступающего из процессора на три части:

1. Поле смещения – используется для выбора байта внутри блока кэш-памяти

2. Поле индекса – определяет номер множества

3. Поле тэга – используется для сравнения

Если общий размер кэш-памяти зафиксировать, то увеличение степени ассоциативности приводит к увеличению количества блоков в множестве, при этом уменьшается размер индекса и увеличивается размер тэга.

При возникновении промаха контроллер кэш-памяти должен выбрать подлежащий замещению блок. Польза от использования организации с прямым отображением заключается в том, что аппаратные решения здесь простые. Выбирать просто нечего в данном случае, так как на попадание проверяется только один блок и только этот блок может быть замещён.

При полностью ассоциативной и множественно-ассоциативной организации кэш-памяти имеются несколько блоков из которых надо выбрать кандидата в случае промаха. Как правило, для замещения блоков используются две основные стратегии – случайная и LRU (Last Recently Used – алгоритм удаления наиболее давно не использующихся элементов).

В первом случае чтобы иметь равномерное распределение блоки-кандидаты выбираются случайно. В некоторых системах чтобы получить воспроизводимое поведение, которое особенно полезно во время отладки аппаратуры, используют псевдослучайный алгоритм замещения.

Во втором случае, чтобы уменьшить вероятность выбрасывания информации, которая скоро может потребоваться, все обращения к блокам фиксируются и заменяется тот блок, который не использовался дольше всех (LRU).

Достоинство случайного способа заключается в том, что его проще реализовать в аппаратуре. Когда количество блоков для поддержания трассы увеличивается, алгоритм LRU становится всё более дорогим и часто только приближённым.

При обращениях к кэш-памяти на реальных программах преобладают обращения по чтению. Все обращения за командами являются обращениями по чтению и большинство команд не пишут в память. Обычно операции записи составляют менее 10% общего трафика памяти. Желание сделать общий случай более быстрым означает оптимизацию кэш-памяти для выполнения операций чтения, однако при реализации высокопроизводительной обработки данных нельзя пренебрегать и скоростью операций записи.

К счастью, общий случай является и более простым. Блок из кэш-памяти может быть прочитан в то же самое время, когда читается и сравнивается его тэг. Таким образом, чтение блока начинается сразу как только становится доступным адрес блока. Если чтение происходит с попаданием, то блок немедленно направляется в процессор. Если же происходит промах, то от заранее считанного блока нет никакой пользы и никакого вреда.

Дата: 2019-02-02, просмотров: 438.