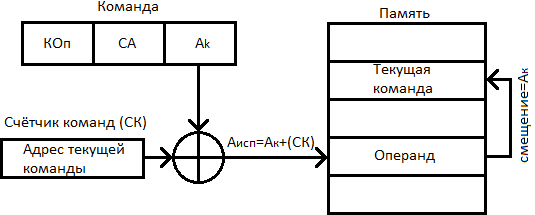

При относительной адресации для получения исполнительного адреса операнда содержимое подполя  команды складывается с содержимым счётчика команд. Таким образом, адресный код в команде представляет собой смещение относительно адреса текущей команды. Следует отметить, что в момент вычисления исполнительного адреса операнда в счетчике команд может уже быть сформирован адрес следующей команды, что нужно учитывать при выборе величины смещения. Обычно подполе

команды складывается с содержимым счётчика команд. Таким образом, адресный код в команде представляет собой смещение относительно адреса текущей команды. Следует отметить, что в момент вычисления исполнительного адреса операнда в счетчике команд может уже быть сформирован адрес следующей команды, что нужно учитывать при выборе величины смещения. Обычно подполе  трактуется как двоичное число в дополнительном коде.

трактуется как двоичное число в дополнительном коде.

Адресация относительно счетчика команд базируется на свойстве локальности, выражающемся в том, что большая часть обращений происходит к ячейкам, расположенным в непосредственной близости от выполняемой команды. Это позволяет сэкономить на длине адресной части команды, поскольку разрядность подполя может быть небольшой. Главное достоинство данного способа адресации состоит в том, что он делает программу перемещаемой в памяти: независимо от текущего расположения программы в адресном пространстве, взаимное положение команды и операнда остается неизменным, поэтому адресация операнда остается корректной.

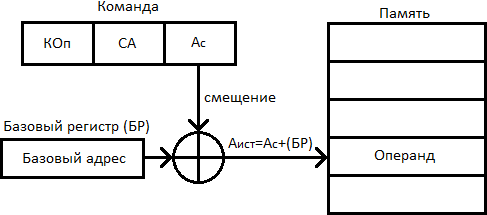

8 способ: Базовая регистровая адресация

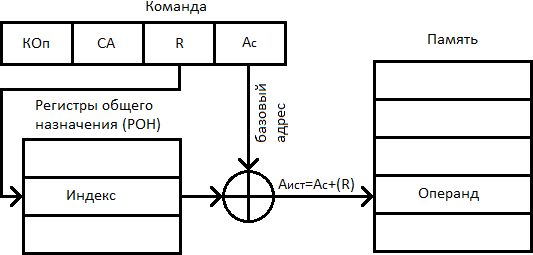

В случае базовой регистровой адресации (БРА) регистр, называемый базовым, содержит полноразрядный адрес, а подполе  – смещение относительно адреса. Ссылка на базовый регистр может быть явной или неявной. В некоторых ВМ имеется специальный базовый регистр и его использование является неявным, то есть подполе

– смещение относительно адреса. Ссылка на базовый регистр может быть явной или неявной. В некоторых ВМ имеется специальный базовый регистр и его использование является неявным, то есть подполе  в команде отсутствует.

в команде отсутствует.

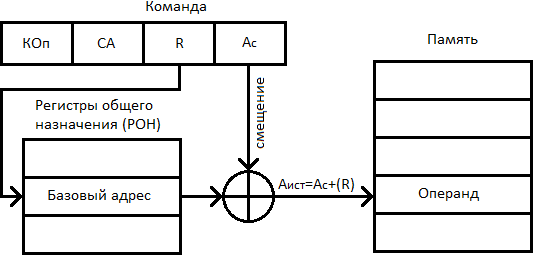

Более типичен случай, когда в роли базового регистра выступает один из регистров общего назначения (РОН), тогда его номер явно указывается в подполе  команды.

команды.

Базовую регистровую адресацию обычно используют для доступа к элементам массива, положение которого в памяти в процессе вычислений может меняться. В базовый регистр заносится начальный адрес массива, а адрес элемента массива указывается в подполе  команды в виде смещения относительно начального адреса массива. Достоинство данного способа в том, что смещение имеет меньшую длину, чем полный адрес, и это позволяет сократить длину адресного поля команды. Короткое смещение расширяется до полной длины исполнительного адреса путем добавления слева битов, совпадающих со значением знакового разряда смещения.

команды в виде смещения относительно начального адреса массива. Достоинство данного способа в том, что смещение имеет меньшую длину, чем полный адрес, и это позволяет сократить длину адресного поля команды. Короткое смещение расширяется до полной длины исполнительного адреса путем добавления слева битов, совпадающих со значением знакового разряда смещения.

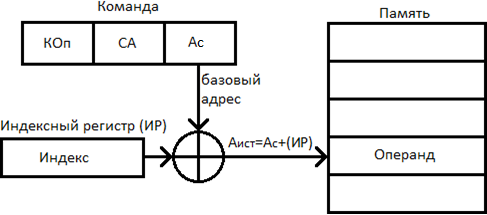

Способ: индексная адресация

При индексной адресации (ИА) подполе  содержит адрес ячейки памяти, а регистр (указанный явно или неявно) – смещение относительно этого адреса. Как видно, этот способ адресации похож на базовую регистровую адресацию. Поскольку при индексной адресации в поле

содержит адрес ячейки памяти, а регистр (указанный явно или неявно) – смещение относительно этого адреса. Как видно, этот способ адресации похож на базовую регистровую адресацию. Поскольку при индексной адресации в поле  находится полноразрядный адрес ячейки памяти, играющий роль базы, длина этого поля больше, чем при базовой регистровой адресации. Тем не менее, вычисление исполнительного адреса операнда производится идентично.

находится полноразрядный адрес ячейки памяти, играющий роль базы, длина этого поля больше, чем при базовой регистровой адресации. Тем не менее, вычисление исполнительного адреса операнда производится идентично.

Индексная адресация предоставляет удобный механизм для организации итеративных вычислений. Пусть, например, имеется массив чисел, расположенных в памяти последовательно, начиная с адреса  , и мы хотим увеличить на единицу все элементы данного массива. Для этого требуется извлечь каждое число из памяти, прибавить к нему 1 и вернуть обратно, а последовательность исполнительных адресов будет следующей:

, и мы хотим увеличить на единицу все элементы данного массива. Для этого требуется извлечь каждое число из памяти, прибавить к нему 1 и вернуть обратно, а последовательность исполнительных адресов будет следующей:

и т. д., вплоть до последней ячейки, занимаемой рассматриваемым массивом. Значение  берется из подполя команды, а в выбранный регистр, называемый индексным регистром, сначала заносится 0. После каждой операции содержимое индексного регистра увеличивается на 1.

берется из подполя команды, а в выбранный регистр, называемый индексным регистром, сначала заносится 0. После каждой операции содержимое индексного регистра увеличивается на 1.

Так как это стандартный случай, в большинстве ЭВМ увеличение или уменьшение содержимого индексного регистра до или после обращения к нему осуществляется автоматически как часть машинного цикла. Такой прием называется автоиндексированием. Если для индексной адресации используются специально выделенные регистры, автоиндексирование может производиться неявно и автоматически. При задействовании для хранения индексов регистров общего назначения необходимость операции автоиндексирования должна указываться в команде специальным битом.

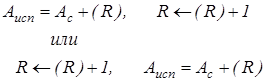

Автоиндексирование с увеличением содержимого индексного регистра носит название автоинкрементной адресации и может быть описано следующим образом:

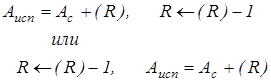

В первом варианте увеличение содержимого индексного регистра происходит после формирования исполнительного адреса, и этот способ называется постинкрементным автоиндексированием. Во втором случае сначала производится увеличение содержимого индексного регистра, и уже новое значение используется для формирования исполнительного адреса. Тогда говорят о преинкрементном автоиндексировании. Автоиндексирование с уменьшением содержимого индексного регистра носит название автодекрементной адресации и может быть описано так:

Здесь также возможны два варианта, отличающиеся последовательностью выполнения операций уменьшения содержимого индексного регистра и вычисления исполнительного адреса: постдекрементное автоиндексирование и предекрементное автоиндексирование. Интересным и весьма полезным является еще один вариант индексной адресации – индексная адресация с масштабированием и смещением: содержимое индексного регистра умножается на масштабный коэффициент и суммируется с  . Масштабный коэффициент может принимать значения: 1, 2, 4, 8, для чего в адресной части команды выделяется дополнительное поле. Описанный способ адресации реализован, например, в микропроцессорах фирмы Intel. Следует особо отметить, что система команд многих ВМ предоставляет возможность различным образом сочетать базовую и индексную адресации в качестве дополнительных способов адресации.

. Масштабный коэффициент может принимать значения: 1, 2, 4, 8, для чего в адресной части команды выделяется дополнительное поле. Описанный способ адресации реализован, например, в микропроцессорах фирмы Intel. Следует особо отметить, что система команд многих ВМ предоставляет возможность различным образом сочетать базовую и индексную адресации в качестве дополнительных способов адресации.

Способ: страничная адресация (СТА)

Страничная адресация предполагает разбиение адресного пространства на страницы. Страница определяется своим начальным адресом, выступающим в качестве базы. Старшая часть этого адреса хранится в специальном регистре – регистре адреса страницы (РАС). В адресном коде команды указывается смещение внутри страницы, рассматриваемое как младшая часть исполнительного адреса. Исполнительный адрес образуется конкатенацией (присоединением)  к РАС.

к РАС.

Способ: блочная адресация

Блочная адресация используется в командах, для которых единицей обработки служит блок данных, расположенных в последовательных ячейках памяти. Этот способ очень удобен при работе с внешними запоминающими устройствами и в операциях с векторами. Для описания блока обычно берётся адрес ячейки, где хранится первый или последний элемент блока и общее количество элементов блока, заданное числом байтов или ячеек. Вместо длины блока может использоваться специальный признак «конец блока», помещаемый за последним элементом блока.

Способ: стековая адресация

Во всех современных процессорах аппаратно поддерживается стек, т.е. область оперативной памяти, предназначенная для временного хранения любой операции. Рассмотрим безадресное кодирование команд при стековой организации памяти.

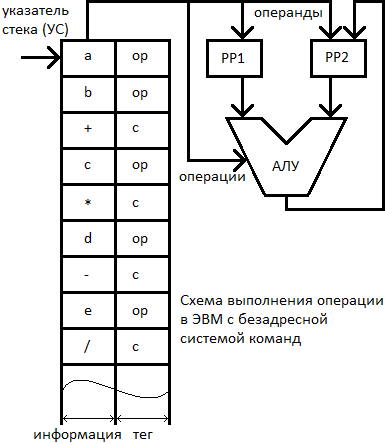

Обращение к ячейкам такой памяти производится последовательно с помощью специального указателя стека (УС), определяющего работающую в данный момент ячейку. Каждая ячейка снабжена тегом – специальным признаком хранимой информации. В состав такой ЭВМ, помимо АЛУ, входят два специальных регистра РР1 и РР2. Здесь значения тегов следующие: ОР (OPerand) – в данной ячейке хранится операнд; С (Command) – признак кода операции.

Рассмотрим работу такой ЭВМ на примере выражения:

На первых двух тактах работы из памяти извлекаются операнды a и b и помещаются в рабочие регистры РР1 и РР2. Считав следующую ячейку стековой памяти, УУ по её тегу определяет, что данная информация представляет собой код операции. Этот код отправляется в АЛУ, где и проводится сложение хранящихся в регистре операндов с записью результата в один из рабочих регистров. Т.к. в следующей ячейке хранится операнд, то он направляется в РР, свободный от записанного результата. После этого производится выполнение следующей операции и т.д.

Для стека характерны две операции:

· PUSH – протолкнуть (поместить элемент в стек);

· POP – вытолкнуть (извлечь элемент из стека).

При этом поддерживается известная процедура «Last In – First Out» (LIFO).

Дата: 2019-02-02, просмотров: 485.