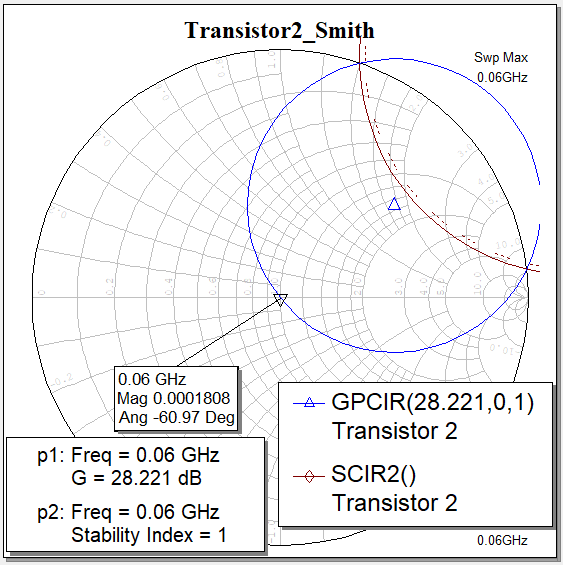

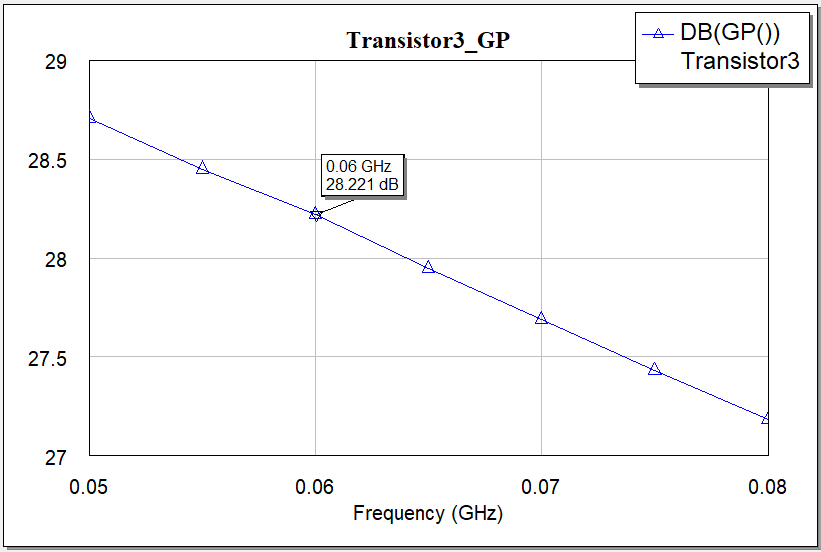

Коэффициент усиления выбирался равным GP для данной частоты (28,221 дБ). Этого достаточно, чтобы при двухкаскадном соединении получить GP, больший 38±0,75 дБ. Выбор GP при построении окружности равного усиления ограничивается значением MSG.

Рисунок 68. Диаграмма Смита. Окружность равного усиления и выходная окружность устойчивости для транзистора NESG340034 (Graphs->Transistor2_Smith)

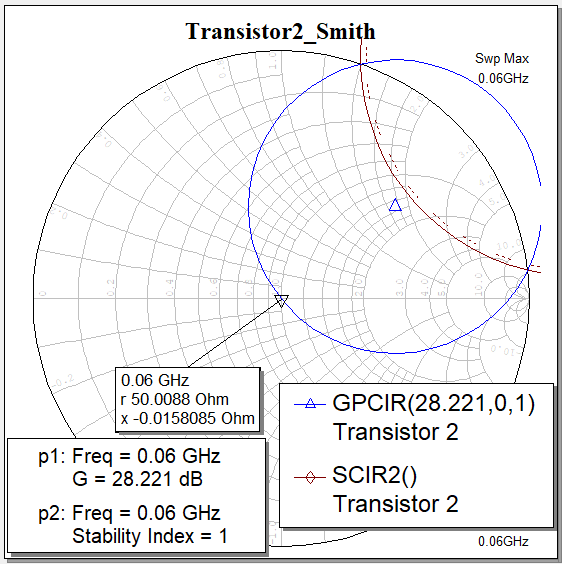

Рисунок 69. Диаграмма Смита. Сопротивление на выходе транзистора NESG340034, обеспечивающее выбранный коэффициент отражения (Graphs->Transistor2_Smith)

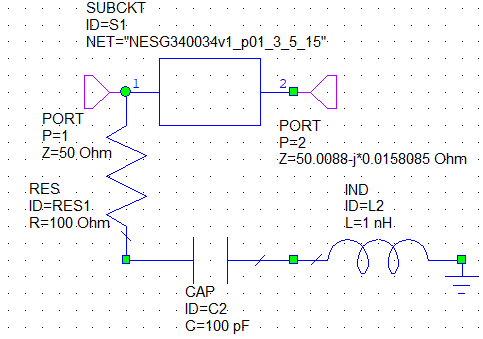

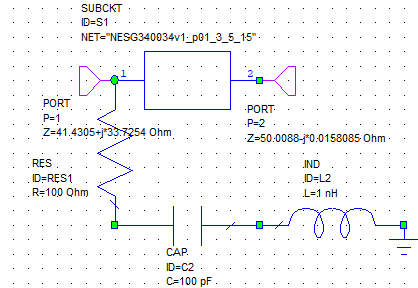

Точка с минимальным коэффициентом отражения на рис. 68 соответствует выходному импедансу 50,0088-j*0,0158085 Ом (рис. 69). Поставим это сопротивление на выходной порт в схеме транзистора (рис. 70).

Рисунок 70. Схема транзистора NSG340034 с выходным портом, обеспечивающим минимальный коэффициент отражения (Circuit Schematics->Transistor_Imped)

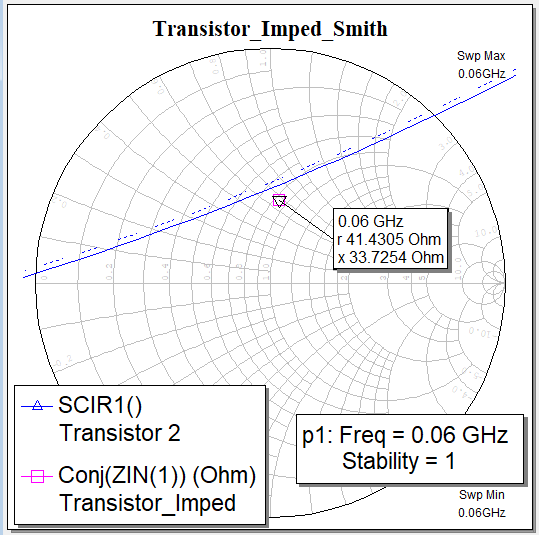

Далее, для схемы, изображённой на рис. 70, определим комплексно-сопряжённое входное сопротивление со стороны порта P=1 на входной диаграмме Смита (рис. 71).

Рисунок 71. Диаграмма Смита. Комплексно-сопряжённое сопротивление со стороны порта P=1 (схема на рис. 70) и входная окружность устойчивости для транзистора NESG340034 (Graphs->Transistor_Imped_Smith)

Приведите окружности для крайних частот диапазона

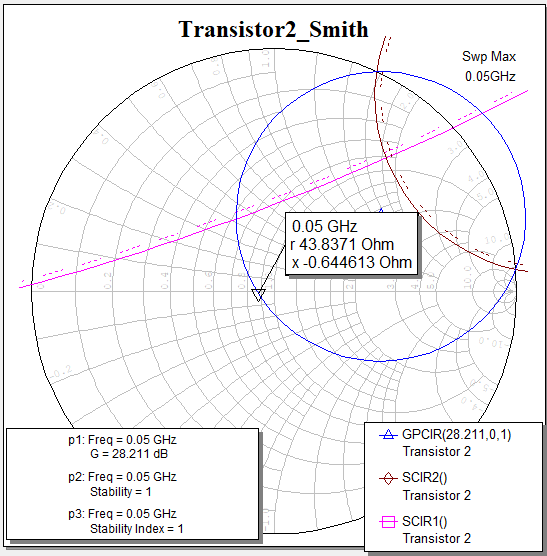

0,05 ГГц:

Рисунок 69а. Диаграмма Смита. Окружность равного усиления и выходная окружность устойчивости для транзистора NESG340034 на частоте 0,05 ГГц (Graphs->Transistor2_Smith)

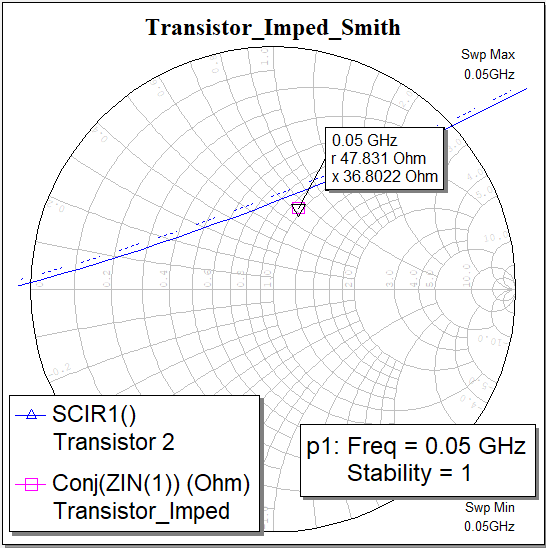

После подстановки этой нагрузки в порт P=2 схемы Circuit Schematcics->Transistor_Imped:

Рисунок 71а. Диаграмма Смита. Комплексно-сопряжённое сопротивление со стороны порта P=1 (схема на рис. 70) и входная окружность устойчивости для транзистора NESG340034 на частоте 0,05 ГГц (Graphs->Transistor_Imped_Smith)

Точка с координатами Conj(ZIN(1)) не попадает в область неустойчивости SCIR1 на диаграмме Смита.

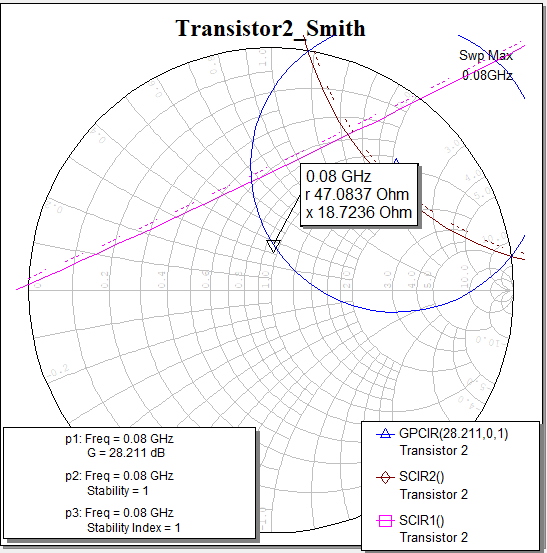

0,08 ГГц:

Рисунок 69б. Диаграмма Смита. Окружность равного усиления и выходная окружность устойчивости для транзистора NESG340034 на частоте 0,08 ГГц (Graphs->Transistor2_Smith)

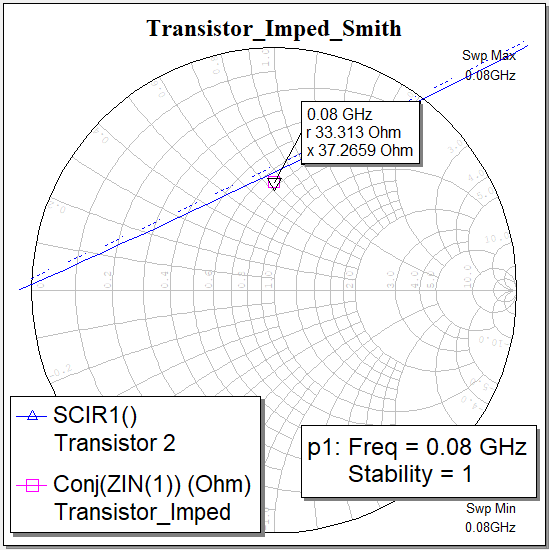

После подстановки этой нагрузки в порт P=2 схемы Circuit Schematcics->Transistor_Imped:

Рисунок 71б. Диаграмма Смита. Комплексно-сопряжённое сопротивление со стороны порта P=1 (схема на рис. 70) и входная окружность устойчивости для транзистора NESG340034 на частоте 0,05 ГГц (Graphs->Transistor_Imped_Smith)

Точка с координатами Conj(ZIN(1)) не попадает в область неустойчивости SCIR1 на диаграмме Смита.

Для частоты 0,06 ГГц искомое сопротивление для порта P=1 равно 41,4305+j*33,7254 Ом. Видно, что точка с этими координатами не попадает в область неустойчивости SCIR1 на диаграмме Смита.

Схема с новыми нагрузками портов (рис. 72) обеспечивает на частоте 60 МГц фактический коэффициент усиления Gp, совпадающий с заданным значением 28,221 дБ (рис. 73).

Рисунок 72. Схема транзистора NSG340034 с нагрузками портов, обеспечивающими заданный фактический коэффициент усиления (Circuit Schematics->Transistor3)

Рисунок 73. Фактический коэффициент усиления для схемы, изображённой на рис. 71 (Graphs->Transistor3_GP)

Т.к. фактический коэффициент усиления Gp транзистора NESG340034 равен 28,221 дБ, а, согласно ТЗ, необходимо построить усилитель с коэффициентом Gp равным 38±0,75 дБ, то необходимо реализовать схему на n = 38/28,221 ≈ 2 каскадах.

Дата: 2019-02-02, просмотров: 448.