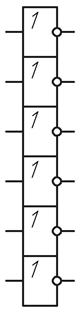

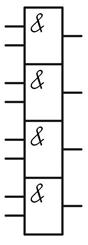

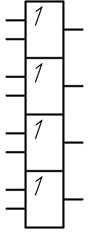

К555(КР1533)ЛН1 К555(КР1533)ЛИ1

К555(КР1533)ЛЛ 1 К555(КР1533)ЛИ3

ПРИЛОЖЕНИЕ В

Структурная схема МП КР580ВМ80А и её описание

Структурная схема МП состоит из 2-х частей: операционной части и управляющей части.

Состав операционной части:

- АЛУ (арифметическо–логическое устройство) – восьмиразрядный комбинационный сумматор для выполнения арифметических операций и набор логических схем для выполнения логических операций, сдвигов и сравнения.

- БФА (буферный регистр аккумулятора) – хранит один операнд на время операции в АЛУ. Этот регистр хранит операнд из аккумулятора.

- БФРГ (буферный регистр) – хранит второй операнд на время операции в АЛУ.

- А (аккумулятор) – восьмиразрядный главный регистр микропроцессора, хранит один операнд до операции в АЛУ и результат после операции в АЛУ.

- РгФл (регистр флагов) – восьмиразрядный регистр, хранит 5 признаков результата в АЛУ.

ZF – признак нулевого результата (ZF=1, если результат 000000002 )

CF – признак основного переноса (CF=1, если есть перенос из 8-го разряда в 9-й).

ACF – признак дополнительного переноса (ACF=1, если есть перенос из 4-го разряда в 5-й).

SF – признак знака (SF=восьмому биту результата).

PF – признак четности (PF=1, если количество единиц в восьмиразрядном результате чётное).

Формат РгФл приведён на рис.П2.2.

- B, C, D, E, H, L – регистры общего назначения (РОН) – это 6 восьми разрядных программно – доступных регистров для временного хранения данных и результата. Они могут объединяться в 16-разрядные регистровые пары – BC, DE, HL; регистры W и Z – программно – недоступны.

-СДК (схема десятичной коррекции) – предназначена для коррекции результата при выполнении операций над двоично-десятичными числами.

Состав управляющей части :

- РгК (регистр команд) – хранит первый байт команды;

- DC (дешифратор команд) – дешифрирует команду; подключает одну из логических схем в устройстве управления, которая вырабатывает определенный набор управляющих сигналов (Yi) для выполнения этой команды;

- УУ (устройство управления) – формирует внутренние управляющие сигналы (Yi) для внутренних блоков МП и внешние управляющие сигналы для системы, а также воспринимает управляющие сигналы из системы;

- РС (программный счётчик) – шестнадцатиразрядный адресный регистр для хранения следующего адреса памяти, по которому будет обращаться МП;

- RA (регистр адреса) – шестнадцатиразрядный адресный регистр для хранения текущего адреса памяти, по которому в данный момент обращается МП;

- SP (указатель стека ) – шестнадцатиразрядный адресный регистр для хранения адреса последней занятой ячейки стековой памяти ( вершины стека);

- СИД (схема инкремент – декремент ) – изменяет на 1 содержимое регистров SP, PC, RA.

- БАдр (буфер данных ) – буферная схема шины адреса – схема с 3-мя состояниями для сопряжения адресных выходов МП А15 – А0 с регистром адреса (RA).

- БД (буфер данных ) – буферная схема шины данных – схема с 3-мя состояниями для сопряжения внешних выводов D0 – D7 с внутренней шиной данных.

| SF 7 | ZF 6 | 0 5 | ACF 4 | 0 3 | PF 2 | 1 1 | CF 0 |

Рисунок В.1 – Формат регистра флагов (РгФл)

Дата: 2018-11-18, просмотров: 739.