Дисциплина ОП 08 Вычислительная техника

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

И

КОНТРОЛЬНЫЕ ЗАДАНИЯ ДЛЯ СТУДЕНТОВ – ЗАОЧНИКОВ

Для специальности 11.02.02 Техническое обслуживание и ремонт радиоэлектронной техники (по отраслям)

Разработала Малафеева Н.Б. - преподаватель ГБПОУ "НРТК"

2018

Содержание

Введение 4

Рабочая программа учебной дисциплины с перечнем рекомендуемой литературы 5

Вопросы для самоконтроля 9

Методические указания по выполнению контрольной работы 10

Задания для контрольной работы 27

Перечень лабораторных работ 35

Перечень рекомендуемой литературы для изучения 36

Приложение А. Таблицы перевода чисел из одной системы в другую и значение степени 2 37

Приложение Б. Условное графическое обозначения ИМС логических элементов 39

Приложение В. Структурная схема микропроцессора КР580ВМ80А и ее описание 40

Приложение Г. Условное графическое обозначения ИМС запоминающих устройств (ЗУ) 43

Приложение Д. Система команд микропроцессора КР580ВМ80А 47

ВВЕДЕНИЕ

Учебная дисциплина «Вычислительная техника» предназначена для реализации государственных требований к минимуму содержания и уровню подготовки выпускников по специальности 11.02.02 Техническое обслуживание и ремонт радиоэлектронной техники среднего профессионального образования.

Учебная дисциплина «Вычислительная техника» является общепрофессиональной и формирует базовые знания для освоения специальных дисциплин «Компьютерная техника», «Основы телекоммуникационных систем», «Микроконтроллеры», «Основы цифровой радиосвязи», а также дисциплин «ТО и ремонт радиоэлектронной техники», «ТО ПЭВМ», «Организация сотовой связи».

Базовыми дисциплинами для изучения «Вычислительной техники» являются: «Информатика», «Электронная техника», «Электротехника», «Цифровая схемотехника».

В результате изучения дисциплины студент должен:

иметь представление :

· о роли и месте знаний по дисциплине «Вычислительная техника» при освоении смежных дисциплин по выбранной специальности и в сфере профессиональной деятельности;

· о современном уровне и перспективах развития вычислительной техники;

знать :

· классификацию, характеристики, принцип действия ЭВМ;

· виды информации, способы ее представления и обработки в ЭВМ;

· арифметические и логические основы ЭВМ;

· типовые узлы и устройства ЭВМ;

· структуру, состав и принципы организации МПС;

· назначение, архитектуру, систему команд, функционирование 8-разрядного микропроцессора КР580ВМ80А;

· виды обмена информацией в МПС;

· организацию памяти и обращения к ней в МПС;

· основы программирования МПС на языке Ассемблер;

· особенности микроЭВМ и персональных ЭВМ (ПЭВМ);

уметь :

· составлять простые программы на языке Ассемблер;

· уметь читать электрические схемы.

Для закрепления теоретического материала студенты выполняют одну домашнюю контрольную работу, состоящую из 6 заданий, и пять лабораторных работ. Формой контроля знаний по дисциплине «Вычислительная техника» является экзамен.

В методических указаниях приведена рабочая программа изучения дисциплины с перечнем рекомендуемой литературы, вопросы для самоконтроля, задания для контрольной работы, методические указания по выполнению каждого задания контрольной работы, перечень лабораторных работ и перечень рекомендуемой литературы для самостоятельного изучения дисциплины.

РАБОЧАЯ ПРОГРАММА УЧЕБНОЙ ДИСЦИПЛИНЫ С ПЕРЕЧНЕМ РЕКОМЕНДУЕМОЙ ЛИТЕРАТУРЫ

ВВЕДЕНИЕ

Роль, содержание и место знаний по дисциплине ‘‘Вычислительная техника’’ в сфере профессиональной деятельности. Связь ее с другими общепрофессиональными и специальными дисциплинами. История развития вычислительной техники в нашей стране. Современный уровень и перспективы развития в области создания современных средств вычислительной техники

Цифровые сигналы: форма и параметры (низкий и высокий логические уровни, фронт и срез, частота повторения и период следования). Основы цифровой обработки сигналов: прием, хранение, преобразование и выдача.

Л. [1, 5, 16]

Тема 4.2 Архитектура 8-разрядных МП (БИС КР580ВМ80А)

Основные технические характеристики БИС МП КР580ВМ80А. Структура МП: структура и функции операционной и управляющей частей. УГО МП. Функционирование МП: цикл команды, машинный цикл, такт. Формирование управляющих сигналов, байт состояния. Система команд. Классификация команд. Режимы адресации. Форматы данных и команд. Программирование на машинном языке. Размещение в памяти программ, исходных данных, промежуточных и конечных результатов. Программирование на языке Ассемблер: запись ассемблерных программ, принципы составления программ, реализация простых программ, отладка и запуск программ.

Л. [4, 6, 7, 15]

Тема 4.3 Архитектура 16-разрядных микропроцессоров

Технические характеристики микропроцессоров К1810ВМ86 и I80286. Архитектура МПК1810ВМ86: сегментация памяти, структура МП, система команд, режимы адресации, форматы данных и команд, режимы работы (минимальный и максимальный), управляющие сигналы, реакция на внешние сигналы. Составление простых программ на языке Ассемблер для МП К1810ВМ86.

Архитектура МП I80286: программная модель, механизм защиты памяти, реальный и защищенный режимы, формирование адреса в этих режимах, общая характеристика системы команд, прерывания и исключения, мультизадачность. Виртуальная память.

Л. [3, 6, 9, 11]

Тема 4.5 Микроконтроллеры

Микроконтроллеры: определение, особенности архитектуры. Технические характеристики отечественных микроконтроллеров и микроконтроллеров фирмы ATMEL.Обобщенная структура микроконтроллера.

Л. [16]

ВОПРОСЫ ДЛЯ САМОКОНТРОЛЯ

1. Классификация и структура ЭВМ.

2. Назовите системы счисления, используемые в ЭВМ.

3. Назовите этапы синтеза цифровых устройств.

4. Назначение типовых комбинационных устройств: шифраторов, дешифраторов, мультиплексоров, сумматоров.

5. Назначение типовых последовательностных устройств: триггеров, регистров, счетчиков, ИМС памяти.

6. Назначение и структура микропроцессорной системы (МПС). Модули и шины МПС.

7. Способы организации обмена информацией в МПС: программно-управляемый обмен, режим прерывания, прямой доступ к памяти.

8. Назначение и особенности регистровых запоминающих устройств, кэш-памяти, внутренней и внешней памяти МПС.

9. Периферийные устройства: назначение и классификация. Принцип работы устройств ввода и вывода информации. Накопители на магнитных и оптических носителях. Flash-память.

10. Назначение микропроцессора (МП), основные технические характеристики МП.

11. Технические характеристики и структура БИС МП КР580 ВМ80А.

12. Классификация команд МП КР580 ВМ80А по выполняемым функциям.

13. 16-разрядные МП: типы и их технические характеристики.

14. 32-разрядные МП: типы и их технические характеристики.

15. Микропроцессоры Pentium: типы и их технические характеристики.

16. Основные особенности однокристальных микроЭВМ– микроконтроллеров.

17. Перспективы развития и применения МП.

18. Принципы организации МПС на микропроцессорном комплекте БИС.

19. Блок центрального процессора: назначение блока; БИС, входящие в блок ЦП.

20. Принципы организации параллельного и последовательного ввода-вывода информации в МПС, БИС универсального синхронно-асинхронного приемопередатчика.

21. Режим прерываний, организация режима прерываний с помощью программируемого контроллера прерываний.

22. Режим прямого доступа к памяти, организация ПДП с помощью программируемого контроллера ПДП.

23. Режим реального времени, организация режима реального времени с помощью программируемого интервального таймера.

24. Назовите назначение модуля основной памяти и принципы организации модулей оперативной и постоянной памяти (модуля ОЗУ и модуля ПЗУ).

25. Назовите способы организация интерфейса с модулем основной памяти.

Решение.

1.Составим таблицу функционирования ЦУ по заданной логической функции выхода.

F( x2, x1, x0 ) =  X0+

X0+  X0+X2

X0+X2

На наборе N0: X2=0, X1=0 и X0=0

F( x2, x1, x0) =  X0+

X0+  X0+X2

X0+X2  = (

= (  *0) +(

*0) +(  *0)+(0*

*0)+(0*  )=1*0+0*1+0*1=0

)=1*0+0*1+0*1=0

F0 (0, 0, 0) =0;

-на наборе N1: X2=0, X1=0 и X0=1

F( x2, x1, x0)=  X0+

X0+  X0+X2

X0+X2  =(

=(  *1)+(

*1)+(  *1)+(0*

*1)+(0*  )=(1*1)+(1*1)+(0*1)=1+1+0=1

)=(1*1)+(1*1)+(0*1)=1+1+0=1

F1 (0, 0, 1) =1;

-на наборе N2: X2=0, X1=1 и X0=0

F( x2, x1, x0 ) =  X0+

X0+  X0+X2

X0+X2  =(

=(  *0)+(

*0)+(  *0)+(0*

*0)+(0*  )==(1*0)+(0*0)+(0*0)=0+0+0=0

)==(1*0)+(0*0)+(0*0)=0+0+0=0

F2 (0, 1, 0) =0;

-на наборе N3: X2=0, X1=1 и X0=1

F( x2, x1, x0 ) =  X0+

X0+  X0+X2

X0+X2  =(

=(  1)+(

1)+(  1)+(0

1)+(0  )=(1*1)+(0*1)+(0*0)=1+0+0=1

)=(1*1)+(0*1)+(0*0)=1+0+0=1

F3 (0, 1, 1) =1;

-на наборе N4: X2=1, X1=0 и X0=0

F( x2, x1, x0 ) =  X0+

X0+  X0+X2

X0+X2  =(

=(  *0)+(

*0)+(  *0)+(1*

*0)+(1*  )=(0*0)+(1*0)+(1*1)=0+0+1=1

)=(0*0)+(1*0)+(1*1)=0+0+1=1

F4 (1, 0, 0) =1;

-на наборе N5: X2=1, X1=0 и X0=1

F( x2, x1, x0 ) =  X0+

X0+  X0+X2

X0+X2  =(

=(  *1)+(

*1)+(  *1)+(1*

*1)+(1*  )=(0*1)+(1*1)+(1*1)=0+1+1=1

)=(0*1)+(1*1)+(1*1)=0+1+1=1

F5(1, 0, 1) =1;

-на наборе N6: X2=1, X1=1 и X0=0

F( x2, x1, x0 ) =  X0+

X0+  X0+X2

X0+X2  =(

=(  *0)+ (

*0)+ (  *0) +(1*

*0) +(1*  ) =(0*0)+(0*0)+(1*0)=0+0+0=0

) =(0*0)+(0*0)+(1*0)=0+0+0=0

F6(1, 1, 0) =0;

-на наборе N7: X2=1, X1=1 и X0=1

F( x2, x1, x0 ) =  X0+

X0+  X0+X2

X0+X2  =(

=(  *1)+(

*1)+(  *1)+(1*

*1)+(1*  )=(0*1)+(0*1)+(1*0)=0+0+0=0

)=(0*1)+(0*1)+(1*0)=0+0+0=0

F7(1, 1, 1) =0.

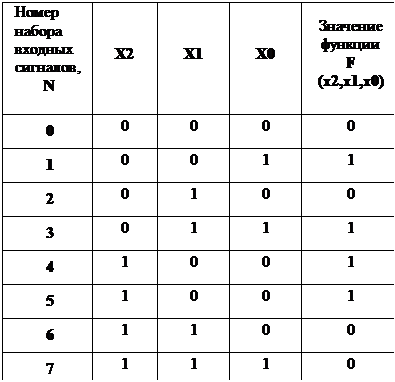

Полученные значения занесем в таблицу 1.

Таблица 1 - Таблица функционирования ЦУ

Таблица 1 - Таблица функционирования ЦУ

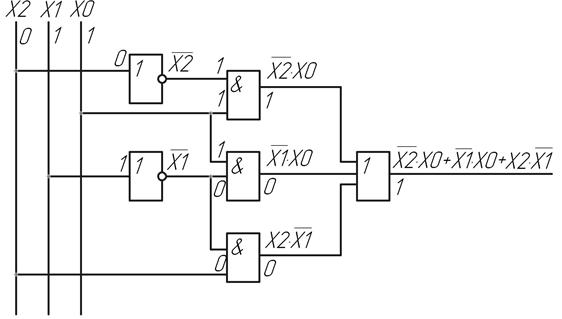

2.Построим электрическую функциональную схему ЦУ в базисе И - ИЛИ- НЕ.

Для построения функциональной схемы по заданному выражению

F( x2, x1, x0) =  X0+

X0+  X0+ X2

X0+ X2

потребуется:

· два элемента НЕ (  и

и  );

);

· три двухвходовых элемента И (3 элемента 2И);

· один трехвходовый элемент ИЛИ (1 элемент 3ИЛИ).

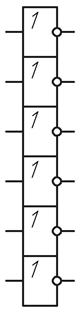

Схема электрическая функциональная ЦУ приведена на рисунке 1.

Рисунок 1 – Схема электрическая функциональная ЦУ

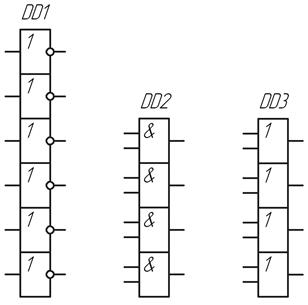

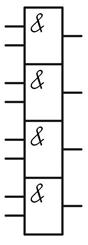

2. Выберем конкретные ИМС логических элементов серии К555 из Приложения Б.

Для построения схемы электрической принципиальной ЦУ выберем ИМС К555ЛН1 (шесть элементов НЕ), К555ЛИ1 (четыре двухвходовых элемента И) и К555ЛЛ1 (четыре двухвходовых элемента ИЛИ). Так как трехвходовый элемент ИЛИ отсутствует в Приложении Б, поэтому при построении схемы используем два двухвходовых элемента ИЛИ.

Рисунок 2 - УГО ИМС логических элементов К555ЛН1 (DD1), К555ЛИ1 (DD2) и К555ЛЛ1 (DD3)

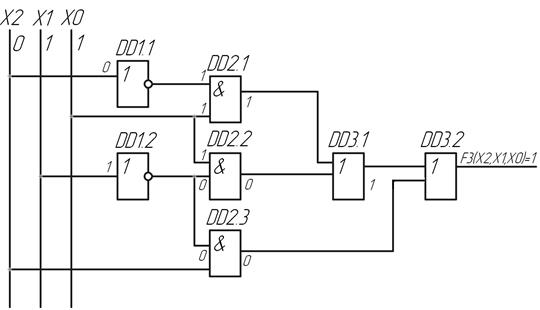

3. Построим схему электрическую принципиальную ЦУ.

Логические элементы ИМС К555ЛН1 обозначим DD1.1, DD1.2; логические элементы ИМС К555ЛИ1 обозначим DD2.1, DD2.2, DD2.3; логические элементы ИМС К555ЛЛ1 обозначим DD3.1, DD3.2.

В ИМС К555ЛН1 из шести элементов НЕ используем только 2 элемента, в ИМС К555ЛИ1 из четырех элементов И используем только 3 элемента, а в ИМС К555ЛЛ1 из четырех элементов ИЛИ используем два элемента. Для построения схемы электрической принципиальной ЦУ потребовалось: 1/3 микросхемы К555ЛН1, 2/3 микросхемы К555ЛИ1, ½ микросхемы К555ЛЛ1.

Схема электрическая принципиальная ЦУ приведена на рисунке 3.

Рисунок 3 – Схема электрическая принципиальная ЦУ

4. На схемах проставлены логические сигналы на входах и выходах каждого логического элемента для входного набора N=3, на котором Х2=0, Х1=1, Х0=1. Чтобы правильно проставить логические уровни на схеме, вспомните таблицы истинности логических элементов И, ИЛИ, НЕ.

Методические указания по выполнению задания №4

Для ответа на вопросы изучите тему 3.3 “Основная (внутренняя) память МПС” раздела 3.

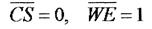

УГО ИМС ЗУ и назначении ее выводов вы найдете в приложении Б, тип ИМС определяется по обозначению микросхемы: "RAM» - это ИМС оперативного запоминающего устройства (ИМС ОЗУ);

ROM – это ИМС постоянного запоминающего устройства (ИМС ПЗУ).

Количество ячеек памяти (N) в ИМС определяется по формуле

N , шт=2 n ,

где n - число адресных входов (А0, А1 и т.д.)

Разрядность ячейки памяти (m) определяется по количеству выходов ИМС (DO или DB). Информационную емкость ИМС (V) можно посчитать по формуле:

V, бит = m * N,

где m - разрядность ячейки памяти;

N - количество ячеек памяти.

Адрес ячейки памяти задан в шестнадцатеричной системе счисления.

Чтобы определить логические сигналы на выводах ИМС ЗУ, необходимо перевести шестнадцатеричный адрес ячейки памяти в двоичный и подать его на адресные входы ИМС (А0, А1 и т.д.)

Режим записи обеспечивается сигналами

Режим чтения обеспечивается сигналами

Рассмотрим пример.

Задана ИМС ЗУ К135РУ5

1. Определить:

а) Тип ИМС ЗУ;

б) Назначение и режимы работы ИМС;

в) Назначение внешних выводов ИМС;

г) Количество ячеек памяти в ИМС - N, шт;

д) Разрядность ячейки памяти – m, бит;

е) Информационную емкость ИМС – V, бит.

2. Указать значение логических сигналов, которые требуется подать на выводы ИМС, для записи 1 в ячейку памяти с адресом 25В

Рисунок 4 – УГО ИМС К135РУ5

а) Тип ИМС К135РУ5 – это ИМС оперативного запоминающего устройства (RAM);

б) Назначение ОЗУ - для кратковременного хранения программ, которые в текущий момент выполняет микропроцессор, и обрабатываемых данных. Режимы работы ОЗУ - запись, хранение и считывание двоичной информации;

в) Назначение выводов:

А0-А9 - адресные входы;

А0 - младший разряд адреса;

А9 - старший разряд адреса;

DI (Data Input) – вход данных;

DO (Data Output – выход данных;

— «Разрешение записи»:

— «Разрешение записи»:

· = 0 — режим записи информации,

· = 1 — режим чтения информации;

— «Выбор микросхемы»:

— «Выбор микросхемы»:

· = 0 — микросхема выбрана: запись или чтение информации;

· = 1 — режим хранения информации;

г) Количество ячеек памяти в ИМС

N=2n,

так как число адресных входов А0-А9 равно 10, т.е. n=10, поэтому

N=210=1024 шт.

д) Разрядность одной ячейки памяти m=1бит;

е) Информационная емкость ИМС:

V, бит = m*N=l*1024 = 1024 бита

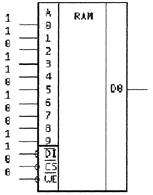

2. Переведем шестнадцатеричный адрес в двоичную систему:

Такие уровни логических сигналов нужно подать на адресные входы ИМС, чтобы обратиться к ячейке памяти с адресом 25В.

Чтобы записать 1 в эту ячейку памяти необходимо подать на вход DI=1 и обеспечить режим записи сигналами

После определения, уровней логических сигналов, проставим, их на выводах. ИМС (см. рисунок).

Методические указания по выполнению задания №5

Для выполнения этого задания необходимо изучить теоретический материал разделов 3, 4 и 5 по рекомендуемой литературе.

Микропроцессорная система (МПС) - это специализированная информационно- вычислительная или управляющая система, построенная на микропроцессорном комплекте БИС (МПК БИС).

Следует обратить внимание на дуализм микропроцессорной техники. МПС – это программно-управляемая система, которая функционирует благодаря наличию как аппаратной части, так и программного обеспечения.

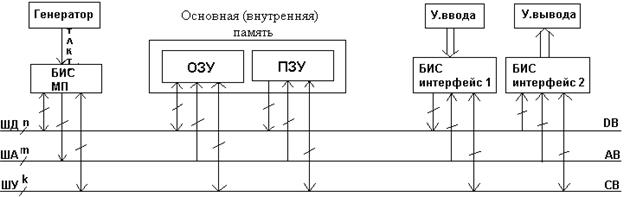

Структурная схема трехшинной МПС приведена на рисунке 5.

Рисунок 5 – Структурная схема трехшинной МПС

Микропроцессор (МП) – обрабатывает данные и управляет обработкой. Основная (внутренняя) память - хранит программы и обрабатываемые данные. Интерфейсные БИС 31организуют сопряжение периферийных устройств (внешней памяти, устройств ввода – вывода информации) с микропроцессорной системой.

Все модули МПС связаны между собой 3–мя шинами: шиной данных (ШД), шиной адреса (ША) и шиной управления (ШУ). По ШД передаются обрабатываемые данные, по ША передаются адреса устройств, по ШУ передаются управляющие сигналы.

Для ответа на вопрос в вариантах 1, 4, 7 и 10 изучите тему 4.1 раздела 4. Основными техническими характеристиками МП являются:

· разрядность МП – это максимальное количество бит информации, обрабатываемых МП за один цикл;

· адресуемая память - это максимальное количество ячеек памяти, к которым может обратиться МП посредством своей шины адреса. Т. к. одна ячейка памяти всегда хранит 1 байт информации, поэтому адресуемая память измеряется в байтах, килобайтах (Кб), мегабайтах (Мб), гигабайтах (Гб);

· тактовая частота синхронизирует работу всех блоков МП, а также работу всех устройств МПС. Период тактовой частоты Т (такт) является наименьшей единицей времени для МП;

· быстродействие – это количество элементарных операций типа «регистр - регистр», выполняемых МП в одну секунду;

· технология (микрон) – это размер одного компонента в кристалле МП.

Технические характеристики МП фирмы Intel приведены в таблице 2. Подробную информацию о МП Вы найдете в методическом пособии для студентов «Микропроцессоры фирмы Intel», составленном Малафеевой Н. Б.

Для ответа на вопрос 2 и 8 вариантов необходимо разобраться с такими видами обмена

информацией в МПС как режим прерывания и прямой доступ к памяти (ПДП).

В режиме ПДП передача данных между периферийными устройствами (ПФУ) и памятью МПС происходит напрямик без участия МП и управляется контроллером ПДП. Этот контроллер обеспечивает операцию быстрого ввода-вывода блоков данных и разгружает МП от управления операциями передачи данных от ПФУ к памяти (см. Л.16, стр. 338-341).

В процессе работы МПС возникают события, требующие немедленной реакции со стороны МП. Это осуществляется с помощью механизма прерываний. Прерывание – это такой режим работы МП, при котором он прерывает выполнение текущей программы по запросу ПФУ и переходит к выполнению специальной прерывающей подпрограммы, предназначенной для обработки этого запроса прерывания. После выполнения прерывающей подпрограммы МП возвращается к выполнению прерванной программы. Для реализации механизма прерываний в МПС используется программируемый контроллер прерываний (см. Л.16, стр. 270-271).

Ответ на вопрос варианта 6 («Flash- память») Вы найдете в Л.16 на стр.205-213 и в Л.8.

Ответ на вопрос варианта 5 «(Микроконтроллеры») Вы найдете в Л.16 на стр.252-255,

Ответ на вопрос варианта 3(«Кэш-память в микропроцессорах») Вы найдете в Л.3 на стр.126-129, 136-139.

Ответ на вопрос варианта 9 («Запоминающие устройства МПС») Вы найдете в Л.2, где описывается внешняя память, и в Л.6, где рассматривается внутренняя (основная ) память МПС.

Таблица 2

Таблица с характеристиками микропроцессоров

Методические указания по выполнению задания №6

В задаче приведен фрагмент программы на языке Ассемблер микропроцессора КР580ВМ80А.

Для решения задачи изучите структуру микропроцессора КР580ВМ80А (приложение В), его систему команд: команды передачи данных, арифметические и логические команды, команды сдвигов, а так же элементы программирования на языке Ассемблер.

Помните, что все регистры МП - восьмиразрядные, а значения адресов и данных в программе заданы в шестнадцатеричной системе счисления.

Пример 1. Микропроцессор КР580ВМ80А выполняет фрагмент программы:

LXIH, 8040

LDA 8060

МО V В, А

LDA 8050

ADD M

SUB В

ADD A

STA 8060

HLT

В ячейке памяти с адресом 8040 записано число 74, по адресу 8050 — число 8А, по адресу 8060 – число 51, т.е.

М[8040]=74; М[8050]=8А; М[8060]=51.

Решение.

1. Структурная схема МП КР580ВМ80А и назначение блоков МП приведены в приложении В.

2. По мнемокоду каждой команды определим содержание выполняемой операции (см. Приложение Д).

а) LXIH ,8040 – команда передачи данных: записывает содержимое 2 и 3 байтов команды в регистровую пару HL, т.е. 80 загружается в регистр Н (80 –> Н), а 40 в регистр L (40 –> L);

HL=8040.

б) LDA 8060 – команда передачи данных: загрузка в регистр- аккумулятор микропроцессора числа из ячейки памяти с адресом, указанным в команде, т.е. 8060.

М[8060]=51 –> Аккумулятор.

Т.е. после выполнения этой команды в аккумуляторе будет записано число 51.

Акк=51.

в) MOV В,А – команда передачи данных: передача числа из регистра А в регистр В,

т.е. А–>В=51,

Акк=В=51.

г) LDA 8050 – команда передачи данных: загрузка в аккумулятор содержимого ячейки памяти с адресом 8050. Т. к. по этому адресу в памяти записано число 8А, поэтому оно будет загружено в регистр-аккумулятор.

М[8050]=8А–>Акк,

Акк=8А.

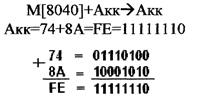

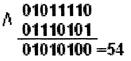

д) ADDM – арифметическая команда: суммирование содержимого аккумулятора с содержимым ячейки памяти, адрес которой записан в регистровой паре HL, результат остается в аккумуляторе,

в паре HL=8040, М[8040]=74,а в Акк=8А.

Akk=FE

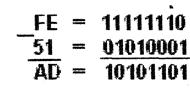

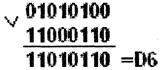

е) SUB В – арифметическая команда: вычитание содержимого регистра В из содержимого аккумулятора, результат остается в аккумуляторе.

Акк-В–>Акк

Akk=FE-51=AD=10101101

Акк= AD

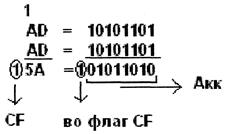

ж) ADDA – арифметическая команда: суммирование содержимого аккумулятора, с содержимым регистра А (аккумулятора), результат остается в аккумуляторе.

Акк+Акк–>Акк

AD+AD=5A=Akk

Акк=5А, С F=1

з) STA 8060 – команда передачи данных: запись содержимого аккумулятора в ячейку памяти с адресом 8060

Акк–>М[8060]

5 A–>[8060]

и) HLT — команда управления микропроцессором: останов

3. Результат Z=5A16=010110102;

результат находится в ячейке памяти с адресом 8060 и в аккумуляторе микропроцессора

Akk= Z=5 A= M[8060]

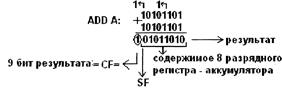

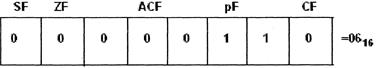

4. Содержимое регистра флагов МП определяется по результату выполнения последней команды фрагмента программы, изменяющей флаги, - это ADD А.

МП анализирует результат выполнения этой команды по 5 признакам (признак нуля, признак знака результата, признак четности числа единиц в результате, признаки основного и дополнительного переносов), и в соответствии с ними выставляет 5 арифметических флагов –ZF (флаг нуля), SF (флаг знака результата), PF (флаг четности), CF (флаг основного переноса из 8 разряда в 9ый) и ACF (флаг дополнительного переноса из 4 разряда в 5ый)

Проанализируем результат операции сложения:

флаг знака результата SF=0, т.к. восьмой бит результата равен 0;

флаг нуля ZF=0, так как результат отличено от 0;

флаг дополнительного переноса ACF=1, т.к. есть перенос из 4 бита в 5 (из младшей тетрады, результата в старшую);

флаг основного переноса CF=1, так как есть перенос из 8 бита в 9;

флаг четности числа единиц в восьми разрядном результате PF=l, так как в результате четное количестве единиц (4 шт)

Все флаги хранятся в определенных разрядах регистра флагов (рис 6)

Рисунок 6 - Содержимое RgF (Регистра флагов)

5. При рассмотрении команд программы (пункт 2) были определены узлы операционного устройства МП, которые участвовали в выполнении фрагмента:

а) Регистровая пара HL;

б) Регистр – аккумулятор;

в) Регистр В;

г) АЛУ;

д) Регистр флагов;

е) 2 буферных регистра на входах АЛУ (БФА и БФР2), в которых хранятся операнды, участвующие в операции АЛУ.

Пример 2.

МП КР580ВМ80А выполняет фрагмент программы:

LXI H, 75C6,

MVI А , 5Е

ANA H

ORA L

СМА

XRA H

STA 8020

HLT

Решение.

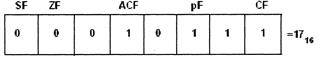

При выполнении этого задания необходимо изучить логические команды микропроцессора (см. Приложение Д) и вспомнить основные логические операции; “И” (ANA), "ИЛИ” (ORA),

исключающее “ИЛИ” (XRA) и “НЕ” (СМА)

Таблица 3 - Таблица истинности логических операций.

1. Структурная схема микропроцессора КР580ВМ80А приведена в приложении В.

2. По мнемокоду каждой команды определим содержание выполняемой операции.

a) LXI Н, 75С6 – команда передачи данных: запись второго (75) и третьего (С6) байтов команды в регистровую пару HL

75–>регистр Н

С6–>регистр L

HL=75С6

б) MVI А, 5Е – команда передачи данных: занесение второго байта команды (5Е) в регистр-аккумулятор

5Е–>Акк

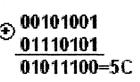

в) ANA Н – логическая команда: логическое “И” над содержимым аккумулятора и регистра Н. Результат сохраняется в аккумуляторе.

Акк ^ Н –> Акк

Акк=5Е=010111102

N=75=011101012

Акк=54

г) ORA L – логическая команда: логическое “ИЛИ” над содержимым аккумулятора и регистра L. Результат сохраняется в аккумулятор. Акк v L –> Акк

Акк=54=010101002

L=C6=110001102

Акк= D6

д) СМА – логическая команда: инверсия аккумулятора

кк–>Акк

кк–>Акк

= 00101001 = 29 = Aкк,

= 00101001 = 29 = Aкк,

Акк=29

е) XRA Н – логическая команда: “исключающее ИЛИ” над содержимым аккумулятора и содержимым регистра Н. Результат сохраняется в аккумуляторе

Акк  Н –> Акк

Н –> Акк

Акк=29=001010012

Н=75=011101012

Акк=5С

ж) STA 8020 – команда передачи данных: запись содержимого аккумулятора в ячейку памяти с адресом 8020.

Акк–> М [8020]

5С–> М [8020]

з) HLT – останов.

3. Результат.

Z=5 C16=010111012

в ячейке памяти с адресом 8020 и в аккумуляторе МП

Z=5 C= M [8020]= Akk

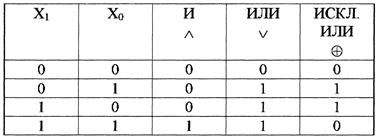

4. Содержимое регистра флагов

определим по двоичному результату команды XRA H.

Z=010111002

флаг знака результата SF=0, т. к. восьмой бит результата равен 0;

флаг нуля ZF=0, т. к. результат не равен 0;

флаг четности PF = l, т. к. в результате четное число единиц (4 единицы).

Команда XRA Н обнуляет флаги основного (CF) и дополнительного (ACF) переносов

CF= ACF=0

Запишем содержимое регистра флагов (см. рисунок 7)

Рисунок 7 - Содержимое регистра флагов

5. В выполнении фрагмента участвуют следующие узлы операционного устройства:

а) Регистровая пара HL;

б) Регистр - аккумулятор;

в) Регистр флагов;

г) Арифметико-логическое устройство;

д) Два буферных, регистра АЛУ – БфР и БфА.

ЗАДАНИЯ ДЛЯ КОНТРОЛЬНОЙ РАБОТЫ

ЗАДАНИЕ 1

Два десятичных числа А и В перевести в двоичную систему счисления (с точностью 8 знаков после запятой) и шестнадцатеричную систему счисления (с точностью 2 знака после запятой).

Произвести сложение и вычитание этих чисел в десятичной, двоичной и шестнадцатеричной системах счисления.

Значения А и В заданы в таблице 4.

Примечание. При вычитании из большего числа вычесть меньшее.

Таблица 4

| Номер варианта | А | В |

| 1 | 2 | 3 |

| 1 | 84,3 | 51,2 |

| 2 | 54,8 | 23,9 |

| 3 | 19,6 | 87,5 |

| 4 | 73,1 | 50,4 |

| 5 | 67,5 | 92,3 |

| 6 | 34,7 | 82,5 |

| 7 | 91,2 | 35,6 |

| 8 | 28,9 | 75,6 |

| 9 | 69,8 | 51,3 |

| 10 | 49,3 | 76,9 |

ЗАДАНИЕ 2

Заданы два двоичных числа Y 1 и Y 2, приведенные в таблице 5.

1. Записать заданные числа в прямом, обратном и дополнительном кодах.

2. Сложить числа в обратном и дополнительном кодах.

Сделать проверку, выполнив арифметическую операцию в двоичной системе счисления.

Таблица 5

| Номер варианта | Y1 | Y2 |

| 1 | 2 | 3 |

| 1 | -001101 2 | -100101 2 |

| 2 | +011011 2 | -011101 2 |

| 3 | -011100 2 | +110101 2 |

| 4 | +110011 2 | -001011 2 |

| 5 | - 0 01100 2 | -1 0 010 0 2 |

| 6 | +010111 2 | -110001 2 |

| 7 | -001001 2 | -101111 2 |

| 8 | -100011 2 | +100000 2 |

| 9 | +110100 2 | -011111 2 |

| 10 | -010001 2 | -011000 2 |

ЗАДАНИЕ 3

Задана логическая функция выхода цифрового устройства F ( x 2, x 1, x 0).

1. Составить таблицу функционирования ЦУ.

2. Построить электрическую функциональную схему ЦУ в базисе И- ИЛИ- НЕ.

3. Выбрать ИМС серии К555 или К1533.

4. Построить электрическую принципиальную схему ЦУ на выбранных ИМС.

5. Указать на электрических схемах значения логических уровней на входах и выходах каждого логического элемента для заданного набора

входных сигналов N.

Логическая функция F ( x 2, x 1, x 0) и номер набора N приведены в таблице 6.

Таблица 6

| Номер варианта | Логическая функция F( x2, x1, x0) | Номер входного набора N |

| 1 | 2 | 3 |

| 1 |  X0 +X1 X0 +X1  + +

| 1 |

| 2 | X2 +  X0 +X1 X0 +X1

| 2 |

| 3 | (X2 +  )(X1 + )(X1 +  ) )

| 3 |

| 4 |  ( (  + X0)(X2 + + X0)(X2 +  ) )

| 4 |

| 5 |  X0 + X2X1 + X0 + X2X1 +

| 5 |

| 6 | X0 (X1 +  )(X2 + )(X2 +  ) )

| 0 |

| 7 | (X2 + X1)(X1 + X0)

| 6 |

| 8 |  + ( + (  X1) + (X2X0) X1) + (X2X0)

| 7 |

| 9 | X2X1X0 +

| 4 |

| 10 | X0 + (X2  ) + ) +  X1X0 X1X0

| 5 |

ЗАДАНИЕ 4

Привести структурную схему трехшинной микропроцессорной системы (МПС). Указать назначение модулей и шин МПС. Ответить на вопрос из таблицы 7 для своего варианта.

Таблица 7

| Номер варианта | Формулировка вопроса |

| 1 | 2 |

| 1 | Дать определение основных технических характеристик микропроцессора: разрядность, адресуемая память, частота, быстродействие, технология. Основные технические характеристики и режимы работы микропроцессора Intel Pentium PRO. |

| 2 | Режим прямого доступа к памяти в МПС. |

| 3 | Кэш-память микропроцессоров. Назначение. Особенности. |

| 4 | Дать определение основных технических характеристик микропроцессоров: разрядность, адресуемая память, частота, быстродействие, технология. Основные технические характеристики и режимы работы микропроцессора Вашего компьютера. |

| 5 | Особенности однокристальных микроЭВМ (микроконтроллеров). Привести пример БИС микроконтроллера. |

| 6 | Flash – память. Назначение. Параметры. |

| 7 | Дать определение основных технических характеристик микропроцессоров: разрядность, адресуемая память, частота, быстродействие, технология. Основные технические характеристики и режимы работы микропроцессора Intel 80286. |

| 8 | Режим прерываний в МПС. |

| 9 | Запоминающие устройства (память) микропроцессорных систем. Назначение. Виды запоминающих устройств. |

| 10 | Дать определение основных технических характеристик микропроцессоров: разрядность, адресуемая память, частота, быстродействие, технология. Основные технические характеристики и режимы работы микропроцессора Intel 8086. |

ЗАДАНИЕ 5

Привести условное графическое обозначение (УГО) интегральной микросхемы запоминающего устройства (ИМС ЗУ).

3. Определить:

- тип ИМС ЗУ;

- назначение и режимы работы ИМС;

- назначение внешних выводов ИМС;

- количество ячеек памяти в ИМС – N, штук;

- разрядность ячейки памяти – m, бит;

- информационную емкость ИМС – V, бит.

4. Указать на УГО ИМС ЗУ значения логических сигналов, которые следует подать на выводы ИМС, чтобы обратиться к ячейке памяти с заданным адресом и записать (или считать) информацию.

5. Тип ИМС, режим работы ИМС и адрес ячейки памяти для своего варианта выбрать из таблицы 8. УГО ИМС приведены в приложении.

Таблица 8

| Номер варианта | Тип ИМС | Режим работы ИМС | Адрес ячейки памяти |

| 1 | 2 | 3 | 4 |

| 1 | К537РУ10A | Запись числа А8 | 4F8 |

| 2 | К537РУ8А | Запись числа Е3 | 70B |

| 3 | К537РУ13А | Запись числа 8 | 27А |

| 4 | КР537РУ4А | Запись 1 | 8D0 |

| 5 | К573РФ2 | Считывание | 410 |

| 6 | К573РФ8А | Считывание | 3B0С |

| 7 | К573РР2 | Считывание | 1BC |

| 8 | КР556РТ15 | Считывание | 13F |

| 9 | КМ1609РР2А | Считывание | 1FA6 |

| 10 | КР537РУ17 | Запись числа 3F | 98D |

Примечание. Данные и адреса в таблице 8 заданы в шестнадцатеричной системе счисления.

ЗАДАНИЕ 6

Микропроцессор КР580ВМ80А выполняет фрагмент программы (таблица 7).

1. Привести структурную схему микропроцессора КР580ВМ80А и указать его назначение.

2. Определить содержание каждой команды программы.

3. Определить результат Z в двоичной и шестнадцатеричной системах счисления. Где находится результат?

4. Определить содержимое регистра флагов после выполнения фрагмента программы (состояние флагов CF, ZF, ACF, PF и SF - пояснить).

5. Выделить на структурной схеме микропроцессора узлы операционного устройства, которые участвуют в выполнение фрагмента.

Содержимое ячеек памяти до выполнения фрагмента программы указано в таблице 9

(столбец 3).

Таблица 9

| Номер варианта | Фрагмент программы | Содержимое ячеек памяти до выполнения фрагмента |

| 1 | 2 | 3 |

| 1 | LXI D, 8025 LXI H, 8048 LDAX D ORA M ADC E CMA XRI, B4 ADD A MOV M, A RRC ADD H HLT | M [8025] = 14 M [8048] = AB |

| 2 | LXI H, 8015 LXI D, 8040 LDAX D ORA L ADD M SBB E ADD A ADD E RAL ADC H MOV M, A HLT | M [8015]=2F M [8016]=35 M [8040]=59 |

| 3 | LXI H, 8020 LDA 8020 ADD M ADC M RAR MOV M, A LDA 8030 ADD A XRA L ADD M STA 8030 HLT | M [8020]=46 M [8030]=1A |

| 4 | LXI B, 2AF4 MVI A, C8 ANA C SUB B MOV D, A MOV A, C CMA XRA D ADD C RAL ADC A STA 8081 HLT | |

| 5 | LDA 8060 RRC ADD A MOV D,A LXI H, 8050 LDA 8040 ADD M ANA L SUB D ADI, E3 STA 8044 HLT | M [8040]=44 M [8050]=37 M [8060]=15 |

| 6 | MVI A, 20 MVI B, 37 LXI H, 4015 ANA B RAL ORA H XRA L CMA SUB B ADD A STA 8020 HLT | |

| 7 7 | MVI A, 23 ADD A RAR MOV B,A LXI H, 8030 ADD L SBB H CMA ADD M ANA B STA 8020 HLT | M [8030]=18 |

| 8 | LXI H, 8050 LDA 8020 MOV B, A LDA 8040 MOV C, A ADD A SBB B ADD C RAR STA 8050 XRA M HLT | M [8020]=29 M [8040]=2F M [8050]=49 |

| 9 | MVI A, 0F MVI D, 35 ADD D RAL SUI, 19 CMA STA 8022 LXI H, 8022 ADD A ADC M ANA L MOV M, A HLT | |

| 10 | LHLD 8020 MOV B, H MOV C, L LDAX B STC* RAR ADC B ORA L SUB C LXI H, 8021 ADD M STA 8080 HLT | M [8020]=2F M [8021]=80 M [802F]=78 |

Примечание. Адреса и содержимое ячеек памяти заданы в шестнадцатеричной системе счисления.

*) Команда STC устанавливает флаг CF в единицу (CF = 1).

ПЕРЕЧЕНЬ ЛАБОРАТОРНЫХ РАБОТ

1. Архитектура и эксплуатация микроЭВМ «Микролаб КР580».

2. Изучение режимов работы микроЭВМ «Микролаб КР580» и основных функций программы «Монитор

3. Исследование выполнения отдельных команд и простых программ на микроЭВМ «Микролаб КР580».

4. Исследование способов организации и выполнения программ арифметической обработки.

5. Исследование способов организации и выполнения программ ввода- вывода.

ПРИЛОЖЕНИЕ А

Таблицы перевода чисел из одной системы в другую и значение степени 2

Таблица А.1-Таблица перевода чисел из одной системы в другую.

| Десятичные q=10 | Двоичные q=2 | Восьмеричные q=8 | Шестнадцатеричные q=16 |

| 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 | 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 10000 10001 10010 10011 10100 10101 10110 10111 11000 11001 11010 11011 11100 11101 11110 11111 100000 | 0 1 2 3 4 5 6 7 10 11 12 13 14 15 16 17 20 21 22 23 24 25 26 27 30 31 32 33 34 35 36 37 40 | 0 1 2 3 4 5 6 7 8 9 A B C D E F 10 11 12 13 14 15 16 17 18 19 1A 1B 1C 1D 1E 1F 20 |

|

Таблица А.2 - Значение степени 2

| |||

n

| 2 | ||

| 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 | 1 2 4 8 16 32 64 128 256 512 1024 2048 4096 8192 16384 32768 65536 131072 262144 524288 1048576

| ||

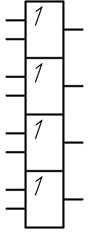

Приложение Б

К555(КР1533)ЛН1 К555(КР1533)ЛИ1

К555(КР1533)ЛЛ 1 К555(КР1533)ЛИ3

ПРИЛОЖЕНИЕ В

Структурная схема МП КР580ВМ80А и её описание

Структурная схема МП состоит из 2-х частей: операционной части и управляющей части.

Состав операционной части:

- АЛУ (арифметическо–логическое устройство) – восьмиразрядный комбинационный сумматор для выполнения арифметических операций и набор логических схем для выполнения логических операций, сдвигов и сравнения.

- БФА (буферный регистр аккумулятора) – хранит один операнд на время операции в АЛУ. Этот регистр хранит операнд из аккумулятора.

- БФРГ (буферный регистр) – хранит второй операнд на время операции в АЛУ.

- А (аккумулятор) – восьмиразрядный главный регистр микропроцессора, хранит один операнд до операции в АЛУ и результат после операции в АЛУ.

- РгФл (регистр флагов) – восьмиразрядный регистр, хранит 5 признаков результата в АЛУ.

ZF – признак нулевого результата (ZF=1, если результат 000000002 )

CF – признак основного переноса (CF=1, если есть перенос из 8-го разряда в 9-й).

ACF – признак дополнительного переноса (ACF=1, если есть перенос из 4-го разряда в 5-й).

SF – признак знака (SF=восьмому биту результата).

PF – признак четности (PF=1, если количество единиц в восьмиразрядном результате чётное).

Формат РгФл приведён на рис.П2.2.

- B, C, D, E, H, L – регистры общего назначения (РОН) – это 6 восьми разрядных программно – доступных регистров для временного хранения данных и результата. Они могут объединяться в 16-разрядные регистровые пары – BC, DE, HL; регистры W и Z – программно – недоступны.

-СДК (схема десятичной коррекции) – предназначена для коррекции результата при выполнении операций над двоично-десятичными числами.

Состав управляющей части :

- РгК (регистр команд) – хранит первый байт команды;

- DC (дешифратор команд) – дешифрирует команду; подключает одну из логических схем в устройстве управления, которая вырабатывает определенный набор управляющих сигналов (Yi) для выполнения этой команды;

- УУ (устройство управления) – формирует внутренние управляющие сигналы (Yi) для внутренних блоков МП и внешние управляющие сигналы для системы, а также воспринимает управляющие сигналы из системы;

- РС (программный счётчик) – шестнадцатиразрядный адресный регистр для хранения следующего адреса памяти, по которому будет обращаться МП;

- RA (регистр адреса) – шестнадцатиразрядный адресный регистр для хранения текущего адреса памяти, по которому в данный момент обращается МП;

- SP (указатель стека ) – шестнадцатиразрядный адресный регистр для хранения адреса последней занятой ячейки стековой памяти ( вершины стека);

- СИД (схема инкремент – декремент ) – изменяет на 1 содержимое регистров SP, PC, RA.

- БАдр (буфер данных ) – буферная схема шины адреса – схема с 3-мя состояниями для сопряжения адресных выходов МП А15 – А0 с регистром адреса (RA).

- БД (буфер данных ) – буферная схема шины данных – схема с 3-мя состояниями для сопряжения внешних выводов D0 – D7 с внутренней шиной данных.

| SF 7 | ZF 6 | 0 5 | ACF 4 | 0 3 | PF 2 | 1 1 | CF 0 |

Рисунок В.1 – Формат регистра флагов (РгФл)

ПРИЛОЖЕНИЕ Г

ПРИЛОЖЕНИЕ Д

Дисциплина ОП 08 Вычислительная техника

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

И

КОНТРОЛЬНЫЕ ЗАДАНИЯ ДЛЯ СТУДЕНТОВ – ЗАОЧНИКОВ

для специальности 11.02.02 Техническое обслуживание и ремонт радиоэлектронной техники (по отраслям)

Разработала Малафеева Н.Б. - преподаватель ГБПОУ "НРТК"

2018

Содержание

Введение 4

Рабочая программа учебной дисциплины с перечнем рекомендуемой литературы 5

Вопросы для самоконтроля 9

Методические указания по выполнению контрольной работы 10

Задания для контрольной работы 27

Перечень лабораторных работ 35

Перечень рекомендуемой литературы для изучения 36

Приложение А. Таблицы перевода чисел из одной системы в другую и значение степени 2 37

Приложение Б. Условное графическое обозначения ИМС логических элементов 39

Приложение В. Структурная схема микропроцессора КР580ВМ80А и ее описание 40

Приложение Г. Условное графическое обозначения ИМС запоминающих устройств (ЗУ) 43

Приложение Д. Система команд микропроцессора КР580ВМ80А 47

ВВЕДЕНИЕ

Учебная дисциплина «Вычислительная техника» предназначена для реализации государственных требований к минимуму содержания и уровню подготовки выпускников по специальности 11.02.02 Техническое обслуживание и ремонт радиоэлектронной техники среднего профессионального образования.

Учебная дисциплина «Вычислительная техника» является общепрофессиональной и формирует базовые знания для освоения специальных дисциплин «Компьютерная техника», «Основы телекоммуникационных систем», «Микроконтроллеры», «Основы цифровой радиосвязи», а также дисциплин «ТО и ремонт радиоэлектронной техники», «ТО ПЭВМ», «Организация сотовой связи».

Базовыми дисциплинами для изучения «Вычислительной техники» являются: «Информатика», «Электронная техника», «Электротехника», «Цифровая схемотехника».

В результате изучения дисциплины студент должен:

иметь представление :

· о роли и месте знаний по дисциплине «Вычислительная техника» при освоении смежных дисциплин по выбранной специальности и в сфере профессиональной деятельности;

· о современном уровне и перспективах развития вычислительной техники;

знать :

· классификацию, характеристики, принцип действия ЭВМ;

· виды информации, способы ее представления и обработки в ЭВМ;

· арифметические и логические основы ЭВМ;

· типовые узлы и устройства ЭВМ;

· структуру, состав и принципы организации МПС;

· назначение, архитектуру, систему команд, функционирование 8-разрядного микропроцессора КР580ВМ80А;

· виды обмена информацией в МПС;

· организацию памяти и обращения к ней в МПС;

· основы программирования МПС на языке Ассемблер;

· особенности микроЭВМ и персональных ЭВМ (ПЭВМ);

уметь :

· составлять простые программы на языке Ассемблер;

· уметь читать электрические схемы.

Для закрепления теоретического материала студенты выполняют одну домашнюю контрольную работу, состоящую из 6 заданий, и пять лабораторных работ. Формой контроля знаний по дисциплине «Вычислительная техника» является экзамен.

В методических указаниях приведена рабочая программа изучения дисциплины с перечнем рекомендуемой литературы, вопросы для самоконтроля, задания для контрольной работы, методические указания по выполнению каждого задания контрольной работы, перечень лабораторных работ и перечень рекомендуемой литературы для самостоятельного изучения дисциплины.

РАБОЧАЯ ПРОГРАММА УЧЕБНОЙ ДИСЦИПЛИНЫ С ПЕРЕЧНЕМ РЕКОМЕНДУЕМОЙ ЛИТЕРАТУРЫ

ВВЕДЕНИЕ

Роль, содержание и место знаний по дисциплине ‘‘Вычислительная техника’’ в сфере профессиональной деятельности. Связь ее с другими общепрофессиональными и специальными дисциплинами. История развития вычислительной техники в нашей стране. Современный уровень и перспективы развития в области создания современных средств вычислительной техники

Цифровые сигналы: форма и параметры (низкий и высокий логические уровни, фронт и срез, частота повторения и период следования). Основы цифровой обработки сигналов: прием, хранение, преобразование и выдача.

Л. [1, 5, 16]

Дата: 2018-11-18, просмотров: 1052.