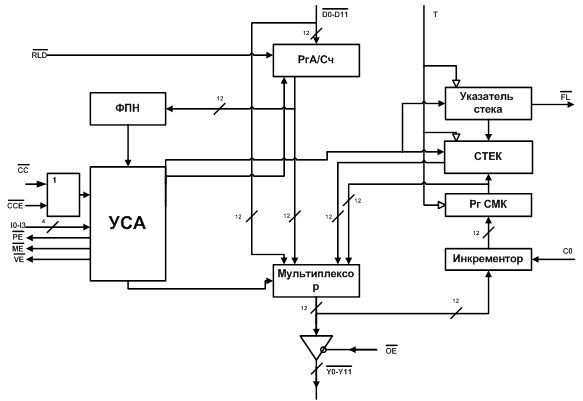

БМУ построен на МПС К1804ВУ4, выполняющей функции управления последовательностью микрокоманд (УМП). Основная функция схемы УМП заключается в формировании последовательности адресов микрокоманд, хранящихся в микропрограммной памяти, под воздействием внешних управляющих сигналов.

Рассматриваемая схема УПМ имеет следующие архитектурные особенности: 12-разрядная размерность всех внутренних элементов УПМ, обеспечивающая возможность адресации до 4096 слов; четыре источника адреса (внутренний регистр адреса/счетчика, счетчик микрокоманд, адресная шина и стек глубиной пять); 16 инструкций управления, большинство из которых являются условными; выходные сигналы отпирания одного из трех внешних устройств, подключенных к адресной шине (позволяют выполнять функции дешифратора); внутренний регистр адреса (может выполнять функции и регистра и счетчика циклов); трехстабильные выходы. Все внутренние регистры построены на триггерах, срабатывающих по положительному фронту тактового сигнала, что упрощает временную синхронизацию.

Устройство управления включает в себя мультиплексор с четырьмя входами, используемый для выбора в качестве источника адреса следующей микрокоманды, регистр/счетчик, вход прямого адреса, счетчик микрокоманд СМК, стек.

Регистр/счетчик РгА/Сч состоит из 12 триггеров D-типа, доступ к которым осуществляется во время одного и того же такта. При выдаче сигнала разрешения загрузки (поступления на вход RLD сигнала низкого уровня) новые данные загружаются в РгА/Сч во время действия переднего фронта тактового импульса. Выход может быть подключен к мультиплексору и использован в качестве источника адреса следующей микрокоманды. В свою очередь, вход прямого адреса устройства является источником данных, загружаемых в РгА/Сч.

Счетчик микрокоманд состоит из 12-разрядного устройства приращения, инкрементора Инкр и 12-разрядного регистра.

Счетчик микрокоманд может использоваться одним из двух способов. Когда сигнал разрешения ввода данных в устройство приращения, подаваемый на вход СО, имеет высокий уровень, в РгСМК во время следующего такта загружается передаваемый на выход адрес, увеличенный на 1 Таким образом обеспечивается последовательное выполнение микрокоманд. Когда сигнал на входе СО имеет низкий уровень, содержимое устройства приращения остается прежним и во время следующего такта СМК перезагружается тем же самым адресом, находящимся на выходе У .Следовательно, одна и та же микрокоманда может выполняться любое количество раз.

Другим источником адреса является вход прямого адреса. Этот источник используется для выполнения переходов в микропрограмме.

Четвертым источником адреса, передаваемого на вход мультиплексора МС, является стек объемом 5 слов

Рис. 3.7.Структурная схема МПС К1804ВУ4

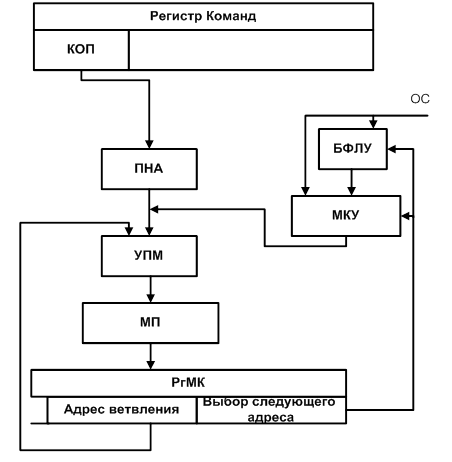

В блок микропрограммного управления входят схема управления последовательностью МК (УПМ), микропрограммная память (МП), регистр микрокоманд (РгМК), блок фиксации логических условий (БФЛУ), мультиплексор кода условий (МКУ), регистр команды (РгК), логические схемы.

ПНА – формирует начальный адрес микропрограммы выполняемой операции. Реализуется на ПЗУ или ПЛМ.

УПМ схема управления последовательностью микрокоманд – формирует последовательность адресов микрокоманд, находящихся в МП. Построена на микросхеме К1804ВУ4.

МП – микропрограммная память представляет собой быстродействующее ПЗУ.

РгМК – регистр микрокоманд.

РгК – регистр команд построен на 6 микросхемах К1804ИР1.

БФЛУ – блок фиксации логических условий.

МКУ – мультиплексор кода условий – производит выбор анализируемого условия.

Выбор следующего адреса определяется инструкцией УПМ и значением логических условий, к которым относятся флажки Z, N, V, C операционных блоков, значение триггера перехода ТП, сигнал занятости ОП Z(ОП) . Выбор анализируемого условия выполняется МКУ.

Рис. 3.8.Блок микропрограммного управления

Регистровая память

Согласно регистровой модели и архитектуре регистровая память должна включать следующие регистры ССП ( СR0), EFLAGS, EIP – 32 разрядные, SR, TR, CR – 15 разрядные, ST() – 80 разрядные. РОНы реализованы внутри МПС, поэтому их описание не приводится. Также к регистровой памяти относятся регистры РгК, РгБ, РАОП, РгЗпОП, РгЧтОП.

32х разрядный регистр ССП(CR0) и регистр флагов EFLAGS, предусмотренные архитектурой IA-32, построены на 4 микросхемах К1804ИР2.

Счётчик команд EIP( 32 разряда) построен на четырёх микросхемах К1804ИР2. Счетчик адреса команд, входящий в EIP, представляет собой 23-разрядный регистр.

Status Register, TAG Register и Control Register также построены на 2 микросхемах К1804ИР2 каждый.

Регистр буфера представляет собой 56-разрядный регистр, который используется для предвыборки команды, с целью уменьшения количества обращений в ОП. Построен на 7 микросхемах К1804ИР2.

Регистры с плавающей точкой представляют собой 8 80-разрядных регистров, которые используются для хранения чисел с ПТ. Выполнены на 20 микросхемах К1804ИР2.

Регистр данных состоит из 32-разрядного регистра и служит для хранения операнда, извлеченного из ОП. Построен на 4 микросхемах К1804ИР2.

Описание К1804ИР2.

Микросхема К1804ИР2 – 8 разрядный параллельный регистр, предназначеннвй для применения в центральных процессорах.

Таблица 3.4 – Назначение выводов К1804ИР2.

| Вывод | Обозначение | Тип вывода | Функциональное назначение выводов |

| 1 | R | Вход | Обнуление регистра |

| 2 | DY0 | Выход | Данные, 0-й разряд |

| 3 | D0 | Вход | Данные, 0-й разряд |

| 4 | D1 | Вход | Данные, 1-й разряд |

| 5 | DY1 | Выход | Данные, 1-й разряд |

| 6 | DY2 | Выход | Данные, 2-й разряд |

| 7 | D2 | Вход | Данные, 2-й разряд |

| 8 | D3 | Вход | Данные, 3-й разряд |

| 9 | DY3 | Выход | Данные, 3-й разряд |

| 10 | C | Вход | Тактовый сигнал |

| 11 | GND | - | Общий |

| 12 | DY4 | Выход | Данные, 4-й разряд |

| 13 | D4 | Вход | Данные, 4-й разряд |

| 14 | D5 | Вход | Данные, 5-й разряд |

| 15 | DY5 | Выход | Данные, 5-й разряд |

| 16 | DY6 | Выход | Данные, 6-й разряд |

| 17 | D6 | Вход | Данные, 6-й разряд |

| 18 | D7 | Вход | Данные, 7-й разряд |

| 19 | DY7 | Выход | Данные, 7-й разряд |

| 20 | EZDY | Вход | Разрешение выходов данных |

| 21 | EWR | Вход | Разрешение записи |

| 22 | Uoc | - | Напряжение питания |

Оперативная память

Слово оперативной памяти составляет 8 байт.. Сама оперативная память рассматривается как черный ящик. Слово выбирается или записывается за одно обращение к памяти при помощи мультиплексоров и демультиплексоров. В состав ОП входят запоминающее устройство( РгЗпОП и РгЧтОП), регистр адреса. Чтение и запись в ОП инициируются сигналами ЧтОП и ЗпОп соответственно. 20 разрядный РгАОП, который хранит адрес команды, которая выполняется в текущий момент, построен на 5 микросхемах К1804ИР1. РгЧтОП и РгЗпОП построены на восьми 8 разрядных микросхемах К1804ИР2.

Блок интерфейса.

БИНТ служит для связи блоков процессора. Он состоит из мультиплексоров, лдемультиплексоров и логических схем согласующих передачу данных и управляющих сигналов.

Посредством БИНТ предоставляется возможность подачи на РгК необходимых разрядов из РгЧтОП или РгБ, осуществляется считывание необходимых байтов из РгК для обработки в БОД, выбор шин входных и выходных данных для БОД, запись в РгЗпОП слово, согласование работы РГЗпОП и ОП.

Также посредством БИНТ происходит выборка адресов регистров в БОД. Для пересылки данных из БПТ в БФТ и обратно также используется БИНТ. Управление БИНТ осуществляется подачей управляющих сигналов из БМУ. Для управления записью в регистры используются соответствующие линии. Выбор подаваемых данных на шины данных МПС также осуществляется посредством БИНТ. ( выбор источников для шин DA и DB)/

Дата: 2019-12-10, просмотров: 376.