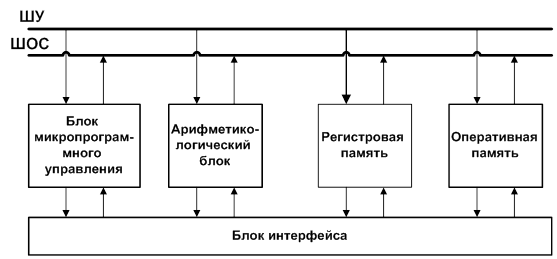

Общая структура процессора

Структурная схема процессора представлена на Рис.3.1. В состав процессора входят: блок микропрограммного управления (БМУ), арифметико-логическое устройство(АЛУ), которое может разделяться на операционный блок с фиксированной точкой и операционный блок с плавающей точкой. Обмен между блоками и также связь между процессором и ОП осуществляется через блок интерфейса (БИНТ). Управляющие сигналы передаются из БМУ в АЛУ (БФТ и/или БПТ) и ОП по шине управления (ШУ). Осведомительные сигналы (ОС) из БФТ, БПТ и ОП поступают в БМУ по шине ШОС.

Рис.3.1.Структурная схема процессора

Выбор и обоснование элементной базы

Для проектирования МП на архитектуре IA-32 был выбран микропроцессорный комплект серии 1804. Сильными сторонами этого комплекта являются микропрограммируемость и возможность разрядного расширения . Высокая производительность реализуется за счёт применения ТТЛШ-технологии. Разнообразие схем, ориентированных на применение в различных устройствах, обеспечивает большую архитектурную гибкость при разработке вычислительной аппаратуры.

Блоки обработки данных построены на схемах К1804ВС2, дополнены схемами ускоренного переноса К1804ВР1.

БМУ построен на схеме К1804ВУ4 . Регистровая память организована на 4х разрядных схемах К1804ИР1 и на 8 разрядных схемах К1804ИР2.

Блоки обработки данных

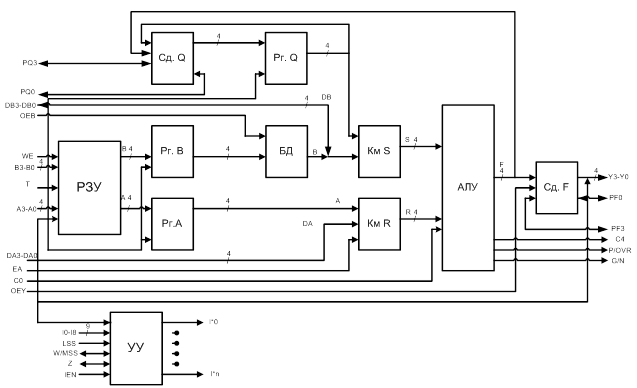

Блок с фиксированной точки

БФТ построен на 8 микропроцессорных секциях К1804ВС2, так как их разрядность 4 бита. Они дополнены 3 схемами ускоренного переноса К1804ВР1., которые уменьшают время вычислений при переносе разряда из одной МПС в другую.

В данной МПС находится РЗУ, содержащее 16 четырёх разрядных регистра. 8 из них будут использоваться как РОНы.

МПС содержит доступные снаружи буферы DY и DB. Корпус имеет 48 выводов. АЛУ выполняет 16 простых операций (7 арифметических, 7 логических, константа 0 и константа 1), а также 9 специальных функций, среди которых есть и многотактные операции (умножение, деление).

Источники операндов задаются сочетанием сигналов на управляющих входах  ,

,  и I0. Это могут быть РА, РВ, DA, DB, PQ в следующих сочетаниях: РА — РВ PA —DB, PA-PQ (EA = 0), DA — РВ, DA - DB, DA —PQ (

и I0. Это могут быть РА, РВ, DA, DB, PQ в следующих сочетаниях: РА — РВ PA —DB, PA-PQ (EA = 0), DA — РВ, DA - DB, DA —PQ (  = 1). В случаях РА — PQ и DA — PQ возможны варианты обмена по шине DB, работающей на выдачу (

= 1). В случаях РА — PQ и DA — PQ возможны варианты обмена по шине DB, работающей на выдачу (  = 0) либо выключенной (

= 0) либо выключенной (  = 1). БФТ связан с ОП, БМУ через шины данных DA, DB, DY, шину МК. На выходе МПс вырабатываются флаги результата: перенос С, переполнение V, знак N, признак нуля Z.

= 1). БФТ связан с ОП, БМУ через шины данных DA, DB, DY, шину МК. На выходе МПс вырабатываются флаги результата: перенос С, переполнение V, знак N, признак нуля Z.

БФТ применяется для выполнения операций над числами с фиксированной точкой.

Рис.3.2. Структурная схема МПС К1804ВС2

Рис.3.2. Структурная схема МПС К1804ВС2

Особенность сдвигателей заключается в том, что на них реализуются не только логические, но и арифметические сдвиги. Арифметические сдвиги не затрагивают знаковый разряд.

В РЗУ МПС К1804ВС2 можно записывать (по адресу В) либо результат АЛУ (сдвинутый или несдвинутый), либо данные с шины DY.

Выделение знакового разряда при арифметических сдвигах, особенности выполнения специальных функций приводят к тому, что МПС должна работать по-разному, в зависимости от того, в какой позиции она находится — старшей, средней или младшей. При создании многоразрядной схемы МПС программируется по занимаемой позиции. Для этого предназначены специальные выводы БИС: LSS и WRITE/MSS. Линия LSS — это вход задания младшей позиции: LSS = 0 — младшая МПС, LSS=1—средняя или старшая МПС. Двунаправленная линия WRITE/MSS имеет два значения: в младшей МПС (при LSS = 0) это выход WRITE для управления входом  (разрешение записи в РЗУ) всех секций; при LSS=1 эта линия становится входом выбора старшей МПС (MSS=0) или средней МПС (MSS = 1).

(разрешение записи в РЗУ) всех секций; при LSS=1 эта линия становится входом выбора старшей МПС (MSS=0) или средней МПС (MSS = 1).

Кроме рассмотренных выше управляющих входов, имеются входы  (разрешение выдачи результата АЛУ па шину DY) и

(разрешение выдачи результата АЛУ па шину DY) и  (разрешение записи в PQ). Выход признака нуля Z в некоторых специальных функциях используется как дополнительный управляющий вход. Так как выходы АЛУ N (знак) и OVR (переполнение) используются только в старшей МПС, а выходы

(разрешение записи в PQ). Выход признака нуля Z в некоторых специальных функциях используется как дополнительный управляющий вход. Так как выходы АЛУ N (знак) и OVR (переполнение) используются только в старшей МПС, а выходы  и

и  для формирования ускоренного переноса — только в средних и младшей МПС, то эти четыре сигнала мультиплексируются в две линии

для формирования ускоренного переноса — только в средних и младшей МПС, то эти четыре сигнала мультиплексируются в две линии  /N и

/N и  /OVR в зависимости от позиции МПС. Всего для управления секцией К1804ВС2 требуется 22 разряда микрокоманды (не считая управления переносом и сдвигами).

/OVR в зависимости от позиции МПС. Всего для управления секцией К1804ВС2 требуется 22 разряда микрокоманды (не считая управления переносом и сдвигами).

Таблица 3.1 - Стандартные функции, реализуемые МПС.

| Сигналы на входах выбора функции |

Функция АЛУ F | |||

| I4 | I3 | I2 | I1 | |

| 0 | 0 | 0 | 0 | Специальные функции при IO=0 |

| 0 | 0 | 0 | 0 | 1111 при IO=1 |

| 0 | 0 | 0 | 1 | S-R-1+CO |

| 0 | 0 | 1 | 0 | R-S-1+CO |

| 0 | 0 | 1 | 1 | R+S+CO |

| 0 | 1 | 0 | 0 | S+CO |

| 0 | 1 | 0 | 1 |  S+CO S+CO

|

| 0 | 1 | 1 | 0 | R+CO |

| 0 | 1 | 1 | 1 |  R+CO R+CO

|

| 1 | 0 | 0 | 0 | 0000 |

| 1 | 0 | 0 | 1 |  Ri^Si Ri^Si

|

| 1 | 0 | 1 | 0 |   Ri+Si Ri+Si

|

| 1 | 0 | 1 | 1 |  Ri+Si Ri+Si

|

| 1 | 1 | 0 | 0 |  Ri+Si Ri+Si

|

| 1 | 1 | 0 | 1 |  RiVSi RiVSi

|

| 1 | 1 | 1 |  0 0

| Ri^Si |

| 1 | 1 | 1 | 1 | RiVSi |

Таблица 3.2 - Специальные функции, реализуемые МПС.

Входы

Функция

Функция АЛУ F

Функция Сд. F

Состояние выводов

Функции Сд. Q и Рг. Q

Состояние выводов

I8

I7

I6

I5

PF3

PF0

PQ3

PQ0

W

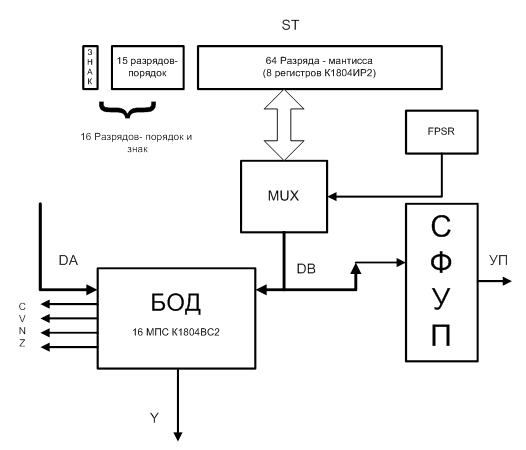

Блок с плавающей точкой

БПТ выполняет операции над числами с плавающей точкой, выполняет их приведение для последующей обработки.

БПТ построен на 16 МПС (К1804ВС2). Регистры РЗУ используются как рабочие. Всего РЗУ состоит из 16ти 64 разрядных регистров. Через мультиплексор из ST , а потом через шину DB, на БОД подаются 64 разряда мантиссы. Для определения вершины стека используется регистр SR. Через шину DY идёт обратная запись в стек 64 разрядов мантиссы. Через шину DA поступают данных из других источников данных. Схема ФУП используется для проверки условий перехода.

Построение БОД для плавающей точки и схема соединения аналогична БФТ.

Рис.3.3. Структурная схема БПТ

Управляющий автомат (УА)

УА с жесткой логикой.

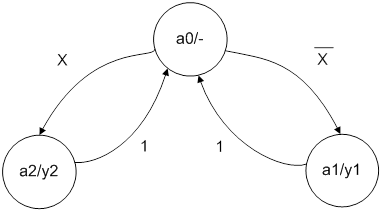

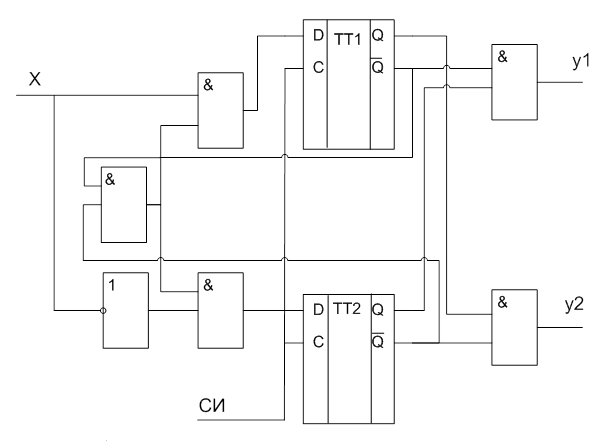

Управляющий автомат с жесткой логикой представляет собой конечный автомат, формирующий выходные сигналы управления в зависимости от текущего состояния и значений осведомительных входных сигналов.

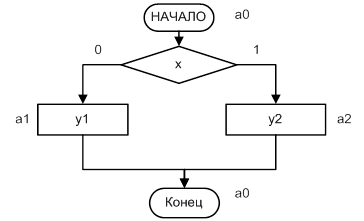

Составим управляющий автомат с жесткой логикой для выполнения команды SUB вычитания чисел в формате с фиксированной точкой.

Составляем отмеченную ГСА:

В условной вершине записываем элемент из множества логический условий X. В операторные вершины записываем операторы (микрооперации) y1 и y2 соответственно из множества микроопераций Y. Начальную и конечную вершины отмечаем символом a1, оставшиеся операторные вершины обозначаем а2 и а3.Находим пути перехода между операторными вершинами.

ГСА автомата имеет условную вершину: x - CR0 и 2 операторные вершины: a1 – Mem16 :=Mem16 - Reg[0..15], a2 – Mem32 :=Mem32 - Reg[0..31]

Рис. 3.4. ГСА алгоритма

Рис. 3.5. Граф автомата Мура

Так как имеется три состояния, то количество триггеров равно 2. (N=]log2n[)

Построение управляющего автомата будем осуществлять на D – триггере.

Таблица 3.3 - Структурная таблица.

| ai | Код ai | ai+1 | Код ai+1 | x | y | Сигналы возбуждения D1 D2 |

| Q1 Q2 | Q1 Q2 | |||||

| a0 | 0 0 | a1 | 0 1 |  x x

| 0 1 | |

| a0 | 0 0 | a2 | 1 0 | x | 1 0 | |

| a1 | 0 1 | a0 | 0 0 | 1 | y1 | 0 0 |

| a2 | 1 0 | a0 | 0 0 | 1 | y2 | 0 0 |

Функции переходов и выходов

D1 = !Q1!Q2 x

D2 = !Q1!Q2!x

y1 = !Q1Q2

y2 = Q1!Q2

Рис. 3.6. Автомат Мура

Дата: 2019-12-10, просмотров: 417.