Введение

Интенсивное развитие микроэлектроники и повышения степени интеграции открыли новое направление в ВТ - создание микропроцессоров и микрокомпьютеров. Появились вычислительные системы с малым уровнем потребления энергии и универсальными возможностями, которые позволяют решать задачи управления объектами различной физической природы. На основе их применения снижаются затраты на автоматизацию основных технических и вспомогательных процессов. В результате будет решена задача комплексной автоматизации производства во всех отраслях. Это позволит увеличить производительность труда, уменьшить себестоимость выпускаемой продукции и значительно сократить ручные операции в промышленности. Однако для широкого развития работ в данном направлении необходимо готовить значительное число инженеров - системотехников, умеющих создавать и применять микропроцессоры и микрокомпьютеры. Кроме того, следует выпускать и много инженеров - математиков, разрабатывающих соответствующее программное обеспечение. Для их обучения необходимо иметь учебные пособия, посвященные аппаратным и программным средствам современной вычислительной техники.

Цель курсового проекта состоит в приобретении практических навыков в проектировании операционного и управляющего автоматов процессора ЭВМ в соответствии с заданными в техническом задании архитектурными особенностями, а также в разработке технической документации, представленной пояснительной запиской и чертежами, выполненными в соответствии с ЕСКД.

Задание на КП

Аспекты разработки процессора

Объектом курсового проектирования является процессор цифровой ЭВМ широкого назначения. Проектируемый процессор должен реализовывать заданную совокупность машинных команд, соответствующих вычислительным системам с архитектурой IA-32. Процесс разработки процессора включает следующие основные шаги:

1) ознакомление с системой заданных машинных команд и архитектурой IA-32,

2) синтез структуры операционных автоматов блоков обработки данных в базисе микропроцессорных секций (МПС) или программируемых логических интегральных схем (ПЛИС),

3) синтез управляющих автоматов с жесткой и микропрограммируемой логикой,

4) разработка математического обеспечения в виде алгоритмов реализации цикла работы процессора и выполнения заданного набора команд,

5) формирование микрокоманды и составление микропрограммы выполнения операции из заданного набора над числами с плавающей точкой,

6) разработка электрических схем (структурной, функциональной и принципиальной) и оформление пояснительной записки.

Исходные данные для проектирования

Набор команд: 18, 57, C2, E2.

Таблица 1. 1 - Команды процессора

| Номер команды | Код операции | Операция | Описание |

| Операции над целыми числами (арифметические) | |||

| 18 | 29h | Sub Mem16, Reg16 Sub Mem32, Reg32 | Mem16 – Reg16->Mem16 Mem32 – Reg32->Mem32 |

| Операции над целыми числами (логические и сдвиги) | |||

| 57 | 0Ch | OR AL, im8 | Al or im8->AL |

| Операции пересылки | |||

| C2 | 87h | XCHG Mem32, Reg32 | Mem32->Tmp Reg32->Mem32 Tmp->Reg32 |

| Операции над числами с плавающей точкой | |||

| E2 | DB/0h | FIADD m16int | m16int+ST(0)->ST(0) |

Таблица 1.2 - Параметры процессора и оперативной памяти

| Ёмкость оперативной памяти, Мб | 8 |

| Длина слова оперативной памяти, байт | 8 |

| Базис реализации процессора | МПС К1804 ВС2 |

| Способ адресации | Базовая EA (0:15) |

Архитектура процессора

Форматы команд

Форматы данных

Таблица 2.2 - Типы данных FPU

| Тип данных | Бит | Количество значащих цифр | Пределы |

| Целое слово | 16 | 4 | -32768 — 32767 |

| Расширенное вещественное | 80 | 19 | 3.37*10-4932 —1.18*104932 |

а) Числа с фиксированной точкой

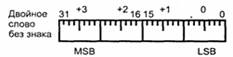

Числа с фиксированной точкой рассматриваются как целые числа со знаком и без знака (Рис.2.1).

Все биты числа с фиксированной точкой без знака используются для представления абсолютной величины числа.. При сложении двух чисел с ФТ без знака считается, что более короткое число дополнено старшими нулями.

В числах с фиксированной точкой со знаком самый левый бит используется для представления знака, за которым следует поле целого числа. Положительные числа представляются в прямом двоичном коде со знаковым битом, равным 0. Отрицательные числа представляются в дополнительном коде со знаковым битом, равным 1.

В некоторых операциях для получения результата используется представление числа в обратном коде. Обратный код числа получается инвертированием каждого бита этого числа.

Рис. 2.1. Представление чисел с фиксированной точкой.

б) Числа с плавающей точкой.

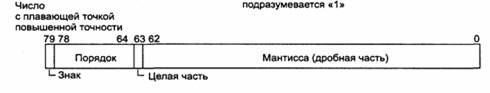

Вещественный формат IEEE, используемый в проектируемом процессоре:

·  расширенное вещественное: бит 79 — знак мантиссы, биты 78 – 64 — 15-битная экспонента + 16 383, биты 63 – 0 — 64-битная мантисса с первой цифрой (то есть бит 63 равен 1) (Рис. 2.2).

расширенное вещественное: бит 79 — знак мантиссы, биты 78 – 64 — 15-битная экспонента + 16 383, биты 63 – 0 — 64-битная мантисса с первой цифрой (то есть бит 63 равен 1) (Рис. 2.2).

Рис. 2.2. Представление чисел с плавающей точкой (расширенный формат)

Формат начинаются со знакового бита для всего числа; 0 указывает на положительное число, 1 — на отрицательное. Затем следует смещенная экспонента. В конце идут мантиссы по 23, 52 и 63 бита соответственно.

Нормализованная мантисса начинается с 1, за которой следует 1 остаток мантиссы. 1 бит перед мантиссой сохраняется. Следовательно, стандарт определяет мантиссу следующим образом. Она состоит из явного бита, который всегда равен 1, и явной двоичной точки, за которыми идут 63 произвольных бита. Если все 63 бита мантиссы равны 0, то мантисса имеет значение 1,0. Если все биты мантиссы равны 1, то числовое значение мантиссы немного меньше, чем 2,0. Значащая часть числа (s) всех нормализованных чисел лежит в диапазоне 1 < s < 2.

Регистр адреса ОП.

Данный регистр должен обеспечивать возможность содержания всех адреса, по которым идет обращение к оперативной памяти. Длину данного регистра можно рассчитать по следующей формуле:

n(РАОП) = log2 (E / L) = log2 (223/ 23) = 20 [бит].

где E – емкость оперативной памяти (8Мб);

L – длина слова (8 байт).

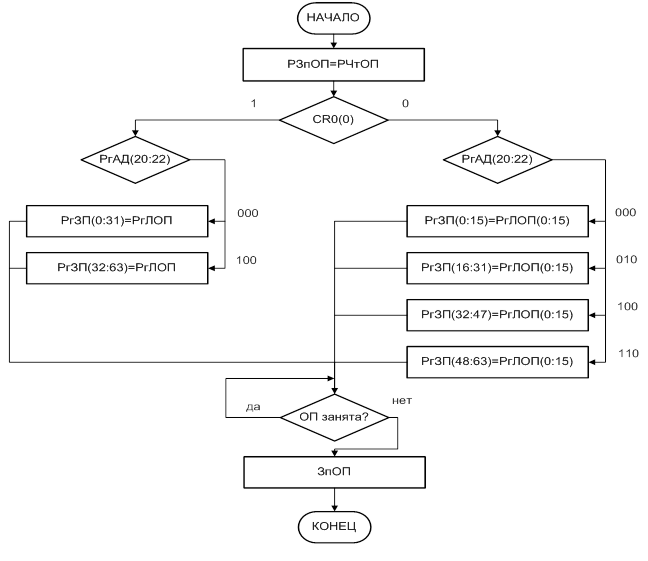

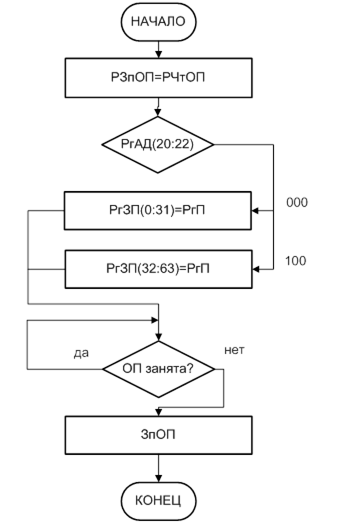

3) Регистр чтения и регистр записи.

Оба регистра будут иметь одинаковую разрядность, равную длине слова ОП- L.

n(РгЧт/РгЗп)=64 [бит]

Регистровая модель

Структура ССП

Словом состояния программы является регистр CR0.

Он содержит системные флаги управления, которые контролируют режим работы статусом процессора.

ССП имеет следующий формат:

| P G | C D | N W | A M | W P | N E | E T | T S | E M | M P | P E | |||

| 31 | 30 | 29 | 28 19 | 18 | 17 | 16 | 15 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Регистр CR0 содержит флаги, которые управляют или показывают условия, относящиеся к системе в целом, а не к отдельной задаче. Младшие 16 бит (биты с 0 по 15) этого регистра называются словом состояния машины (Machine Status Word - MSW) для совместимости с МП 80286.

PE - разрешение защиты (Protection Enable, 286+). Когда PE=1 процессор находится в защищенном режиме. Если бит сброшен, то процессор находится либо в режиме реального адреса, либо в режиме системного управления (тип режима определяется аппаратно: в режиме системного управления активен сигнал SMIACT#).

MP - наличие сопроцессора (Math Present, 286+). Влияет на выполнение команды WAIT/FWAIT, которая используется для взаимодействия с сопроцессором(0).

EM - эмуляция сопроцессора (Emulation, 286+). Показывает, нужно ли эмулировать функции сопроцессора. Установка бита EM часто возникает в случае отсутствия сопроцессора в системе. Когда EM=1, любая команда для сопроцессора, команда MMX или SSE/SSE2 вызывает особый случай(0).

TS - задача переключена (Task Switched, 286+). Процессор устанавливает этот бит при каждом переключении задач. Он также проверяет этот бит, когда интерпретирует команды сопроцессора, так как состояние последнего требуется сохранять только в случае запроса сопроцессора новой задачей. Бит TS может быть очищен загрузкой в регистр CR0, а также специальной командой CLTS(0).

ET - тип расширения (Extension Type, 386, 486). Показывает тип сопроцессора: 80287 (ET=0), 80387 или встроенный FPU i486DX (ET=1). В новых моделях бит зарезервирован и всегда содержит 1.

NE - ошибка сопроцессора (Numeric Error, 486+). Когда NE=1, процессору разрешается пользоваться внутренним ("родным") механизмом сигнализации ошибок с плавающей точкой. Когда NE=0, процессор эмулирует сигнализацию ошибок с плавающей точкой как у внешних сопроцессоров (80287, 80387), выставляя сигнал FERR#, который должен обрабатываться внешним контроллером прерываний(0).

WP - защита от записи (Write Protect, 486+). Защита от записи страниц с пометкой "read-only" при обращениях с уровня супервизора.

AM - маска выравнивания (Alignment Mask, 486+). Если CR0.AM=1 и EFLAGS.AC=1 и CR0.PE=1 и CPL=3, то производится контроль выравнивания. Т.е. при обращениях к памяти двойное слово обязательно должно начинаться с адреса, кратного 4, а 16-битное слово - с адреса, кратного 2, иначе генерируется нарушение контроля выравнивания (исключение #17).

NW - несквозная запись (Not Write-through, 486+). Используется для управления кэшированием(0).

CD - запрещение кэш-памяти (Cache Disable, 486+). Используется для управления кэшированием(1).

PG - страничная трансляция (Paging, 386+). Определяет, использует ли микропроцессор таблицы страниц для трансляции линейных адресов в физические. Страничная трансляция используется только в защищенном режиме, и попытка выставить этот бит в реальном режиме приводит к нарушению общей защиты (исключение #13)(0).

Status Register

Показывает текущее состояние x87FPU.

| 15 | 14 | 13 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| B | C3 | TOP | C2 | C1 | C0 | ES | SF | PE | OE | UE | ZE | DE | IE |

B - FPU занят

TOP - вершина стека

Флаги исключений

- точность

- переполнение

- деление на 0 ( не используется)

- денормализованный операнд

- неправильная операция

SF – ошибка стека( не используется)

ES – статус ошибки(не используется)

C3 C2 C1 C0- флаги состояния (с3,с2,с1 – не используются)

Control Register .

Содержит маски исключений и контролирует точность и методы округления.

| 15 14 13 | 12 | 11 10 | 9 8 | 7 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| X | RC | PC | PM | OM | UM | ZM | DM | IM |

X – контроль бесконечности

RC – контроль округления

PC - контроль точности

Маски исключений

- точность

- Underflow

- переполнение

- деление на 0(нет)

- денормализованный операнд

- неверная операция

TAG Register

Регистр отражает содержимое регистров стека FPU.

| 15 14 | 13 12 | 11 10 | 9 8 | 7 6 | 5 4 | 3 2 | 1 0 |

| TAG(7) | TAG(6) | TAG(5) | TAG(4) | TAG(3) | TAG(2) | TAG(1) | TAG(0) |

TAG значения

00 — используемый

01 — 0

10 — NaN, неподдерживаемый формат, бесконечность или денормализованный

11 — пустой

Регистры, предусмотренные архитектурой IA-32:

1) восемь 32-разрядных регистров общего назначения (РОН): EAX,

EBX, ECX, EDX, ESI, EDI, EBP, ESP;

2) шесть 16-разрядных сегментных регистров CS, SS, DS, ES, FS,

GS;

3) 32-разрядный указатель команд EIP;

4) 32-разрядный регистр флагов EFLAGS;

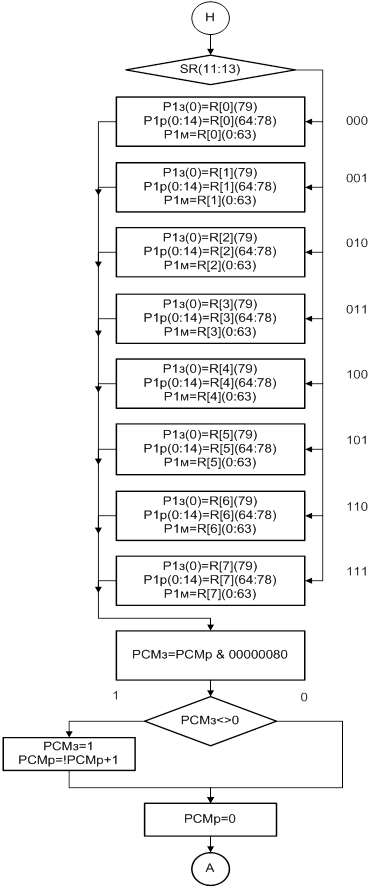

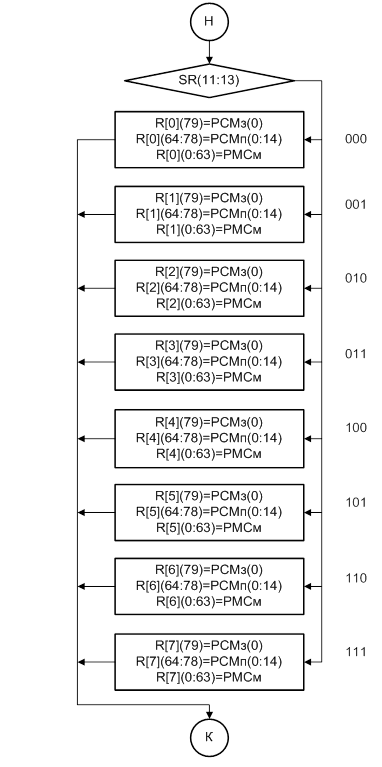

5) восемь 80-разрядных регистров данных R0-R7 для чисел с плавающей точкой, организованных в виде кольцевого стека;

6) 16-разрядные регистры блока с плавающей точкой: регистр тэгов

TW, регистры управления FPCR и состояния FPSR;

7) 32-разрядный системный регистр CR0.

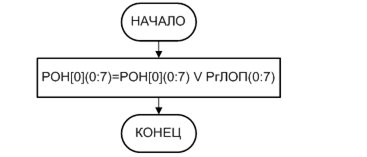

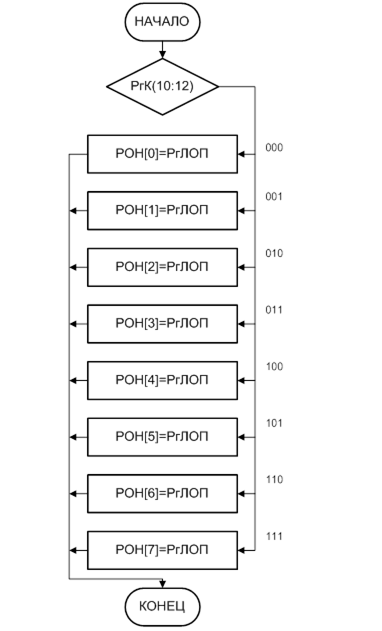

Регистры БОД

БОД БФТ содержит 16 – 32-х разрядных регистров, 8 из них РОНы, 6 – сегментные и 2 рабочих регистра – РгЛОП (регистр, куда извлекается левый операнд из памяти) и РгП ( регистр для правого операнда). Для упрощения понимания алгоритма сложения чисел с ПТ (команда FIADD) внесём синонимы рабочих регистров БФТ. Р1р ( порядок числа из ST) , РСМр (порядок числа из памяти)- это РгП.

Таблица 2.3 – Регистры БФТ

| Обозначение | Адрес Регистра | Комментарий |

| РОН[1] | 0000 | EAX |

| РОН[2] | 0001 | EDX |

| РОН[3] | 0010 | ECX |

| РОН[4] | 0011 | EBX |

| РОН[5] | 0100 | EBP |

| РОН[6] | 0101 | ESP |

| РОН[7] | 0110 | ESI |

| РОН[8] | 0111 | EDI |

| Seg[1] | 1000 | CS |

| Seg[2] | 1001 | SS |

| Seg[3] | 1010 | DS |

| Seg[4] | 1011 | ES |

| Seg[5] | 1100 | FS |

| Seg[6] | 1101 | CS |

| РгЛОП | 1110 | Рабочий |

| РгП | 1111 | Рабочий |

БОД БПТ содержит 16 – 64-х разрядных регистров. Все они являются рабочими.

Таблица 2.4 – Регистры БПТ

| Обозначение | Комментарий |

| Р1з | Рабочий |

| Р1м | Рабочий |

| РСМз | Рабочий |

| РСМм | Рабочий |

| СчТ | Рабочий |

| РПТ[5..16] | Рабочий |

Также в регистровую модель входят EFLAGS, CCП(CR0), EIP(CчАК), с разрядностью по 32 бита.

Дополнительно к регистровой памяти относятся РгК, буферный регистр РгБ, РгЧтОП, РгЗпОП. Отдельно размёщены стековые регистры ST, также TR, SR, TR.

Виды адресации

В архитектуре IA-32 определен большой и гибкий набор режимов адресации, используемых для доступа к отдельным элементам и областям памяти. Как минимум один операнд из двух, которые используются в команде, должен находиться в регистре. Регистр задается в поле Reg/OPcode байта ModR/M. В таблице 2.9 приведены значения байта ModR/M для 32-х битного режима. В таблице 2.10 приведены значения байта ModR/M для 16-и битного режима. Если второй операнд тоже содержится в регистре, этот регистр задается в поле R/M того же байта. Если же второй операнд находиться за пределами регистра, он может быть непосредственно задан в команде, такой вид адресации называется непосредственным, или же храниться в памяти. В таблице 2.7 показано, как задается второй операнд для 32-х разрядного режима. Такие типы адресации, как косвенная регистровая и регистровая определяются 2-х битовым полем ModR/M. В базовой индексной адресации применяется байт SIB. Коды коэффициентов масштабирования 1, 2, 4 и 8 соответствуют кодам 00, 01, 10, 11. В этом байте задаются базовый и индексный регистры. Аналогичное описание для 16-и битного режима приведено в таблице 2.8.

Непосредственная адресация (immediate). Операнд содержится прямо в команде. Это 8-разрядное, 16-разрядное или 32-разрядное число, длина которого определяется соответствующим битом в коде операции.

Прямая адресация (direct). Адрес операнда в памяти определяется заданным в команде смещением.

Регистровая адресация (register). Операнд содержится в одном из восьми регистров общего назначения, заданном в команде.

Косвенная регистровая адресация (register indirect). Адрес операнда в памяти содержится в одном из восьми регистров общего назначения, заданном в команде.

Базовая индексная (base with index). В команде задаются два из восьми регистров общего назначения и коэффициент масштабирования – 1,2,4 или 8. Регистры используются как базовый и индексный, а исполнительный адрес вычисляется следующим образом: содержимое индексного регистра умножается на коэффициент масштабирования, а к результату прибавляется содержимое базового регистра.

Таблица 2.5 – Режимы адресации, выбираемые байтами ModR/M SIB(32)

| Байты ModR/M |

Адресация | |

| Поле Mod B7 b6 | Поле R/M b2 b1 b0 | |

| 0 0 | Reg | Косвенная регистровая, EA=[Reg] |

| 1 1 | Reg | Регистровая, EA=Reg |

| Исключения | ||

| 0 0 | 1 0 1 | Прямая, EA=Disp32 |

| 0 0 | 1 0 0 | Базовая индексная(применяется байт SIB), EA=[Base]+[Index]×Scale. |

Таблица 2.6 – Режимы адресации, выбираемые байтами ModR/M SIB(16)

| Быйты ModR/M |

Адресация | |

| Поле Mod b7 b6 | Поле R/M b2 b1 b0 | |

| 0 0 | Reg | Косвенная регистровая, EA=[Reg] |

| 1 1 | Reg | Регистровая, EA=Reg |

| Исключения | ||

| 0 0 | 1 1 0 | Прямая, EA=Disp16 |

Общая структура процессора

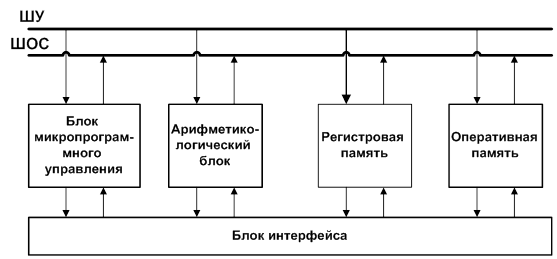

Структурная схема процессора представлена на Рис.3.1. В состав процессора входят: блок микропрограммного управления (БМУ), арифметико-логическое устройство(АЛУ), которое может разделяться на операционный блок с фиксированной точкой и операционный блок с плавающей точкой. Обмен между блоками и также связь между процессором и ОП осуществляется через блок интерфейса (БИНТ). Управляющие сигналы передаются из БМУ в АЛУ (БФТ и/или БПТ) и ОП по шине управления (ШУ). Осведомительные сигналы (ОС) из БФТ, БПТ и ОП поступают в БМУ по шине ШОС.

Рис.3.1.Структурная схема процессора

Блоки обработки данных

Блок с фиксированной точки

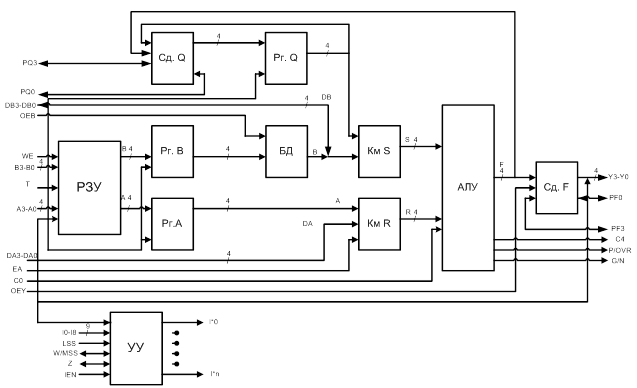

БФТ построен на 8 микропроцессорных секциях К1804ВС2, так как их разрядность 4 бита. Они дополнены 3 схемами ускоренного переноса К1804ВР1., которые уменьшают время вычислений при переносе разряда из одной МПС в другую.

В данной МПС находится РЗУ, содержащее 16 четырёх разрядных регистра. 8 из них будут использоваться как РОНы.

МПС содержит доступные снаружи буферы DY и DB. Корпус имеет 48 выводов. АЛУ выполняет 16 простых операций (7 арифметических, 7 логических, константа 0 и константа 1), а также 9 специальных функций, среди которых есть и многотактные операции (умножение, деление).

Источники операндов задаются сочетанием сигналов на управляющих входах  ,

,  и I0. Это могут быть РА, РВ, DA, DB, PQ в следующих сочетаниях: РА — РВ PA —DB, PA-PQ (EA = 0), DA — РВ, DA - DB, DA —PQ (

и I0. Это могут быть РА, РВ, DA, DB, PQ в следующих сочетаниях: РА — РВ PA —DB, PA-PQ (EA = 0), DA — РВ, DA - DB, DA —PQ (  = 1). В случаях РА — PQ и DA — PQ возможны варианты обмена по шине DB, работающей на выдачу (

= 1). В случаях РА — PQ и DA — PQ возможны варианты обмена по шине DB, работающей на выдачу (  = 0) либо выключенной (

= 0) либо выключенной (  = 1). БФТ связан с ОП, БМУ через шины данных DA, DB, DY, шину МК. На выходе МПс вырабатываются флаги результата: перенос С, переполнение V, знак N, признак нуля Z.

= 1). БФТ связан с ОП, БМУ через шины данных DA, DB, DY, шину МК. На выходе МПс вырабатываются флаги результата: перенос С, переполнение V, знак N, признак нуля Z.

БФТ применяется для выполнения операций над числами с фиксированной точкой.

Рис.3.2. Структурная схема МПС К1804ВС2

Рис.3.2. Структурная схема МПС К1804ВС2

Особенность сдвигателей заключается в том, что на них реализуются не только логические, но и арифметические сдвиги. Арифметические сдвиги не затрагивают знаковый разряд.

В РЗУ МПС К1804ВС2 можно записывать (по адресу В) либо результат АЛУ (сдвинутый или несдвинутый), либо данные с шины DY.

Выделение знакового разряда при арифметических сдвигах, особенности выполнения специальных функций приводят к тому, что МПС должна работать по-разному, в зависимости от того, в какой позиции она находится — старшей, средней или младшей. При создании многоразрядной схемы МПС программируется по занимаемой позиции. Для этого предназначены специальные выводы БИС: LSS и WRITE/MSS. Линия LSS — это вход задания младшей позиции: LSS = 0 — младшая МПС, LSS=1—средняя или старшая МПС. Двунаправленная линия WRITE/MSS имеет два значения: в младшей МПС (при LSS = 0) это выход WRITE для управления входом  (разрешение записи в РЗУ) всех секций; при LSS=1 эта линия становится входом выбора старшей МПС (MSS=0) или средней МПС (MSS = 1).

(разрешение записи в РЗУ) всех секций; при LSS=1 эта линия становится входом выбора старшей МПС (MSS=0) или средней МПС (MSS = 1).

Кроме рассмотренных выше управляющих входов, имеются входы  (разрешение выдачи результата АЛУ па шину DY) и

(разрешение выдачи результата АЛУ па шину DY) и  (разрешение записи в PQ). Выход признака нуля Z в некоторых специальных функциях используется как дополнительный управляющий вход. Так как выходы АЛУ N (знак) и OVR (переполнение) используются только в старшей МПС, а выходы

(разрешение записи в PQ). Выход признака нуля Z в некоторых специальных функциях используется как дополнительный управляющий вход. Так как выходы АЛУ N (знак) и OVR (переполнение) используются только в старшей МПС, а выходы  и

и  для формирования ускоренного переноса — только в средних и младшей МПС, то эти четыре сигнала мультиплексируются в две линии

для формирования ускоренного переноса — только в средних и младшей МПС, то эти четыре сигнала мультиплексируются в две линии  /N и

/N и  /OVR в зависимости от позиции МПС. Всего для управления секцией К1804ВС2 требуется 22 разряда микрокоманды (не считая управления переносом и сдвигами).

/OVR в зависимости от позиции МПС. Всего для управления секцией К1804ВС2 требуется 22 разряда микрокоманды (не считая управления переносом и сдвигами).

Таблица 3.1 - Стандартные функции, реализуемые МПС.

| Сигналы на входах выбора функции |

Функция АЛУ F | |||

| I4 | I3 | I2 | I1 | |

| 0 | 0 | 0 | 0 | Специальные функции при IO=0 |

| 0 | 0 | 0 | 0 | 1111 при IO=1 |

| 0 | 0 | 0 | 1 | S-R-1+CO |

| 0 | 0 | 1 | 0 | R-S-1+CO |

| 0 | 0 | 1 | 1 | R+S+CO |

| 0 | 1 | 0 | 0 | S+CO |

| 0 | 1 | 0 | 1 |  S+CO S+CO

|

| 0 | 1 | 1 | 0 | R+CO |

| 0 | 1 | 1 | 1 |  R+CO R+CO

|

| 1 | 0 | 0 | 0 | 0000 |

| 1 | 0 | 0 | 1 |  Ri^Si Ri^Si

|

| 1 | 0 | 1 | 0 |   Ri+Si Ri+Si

|

| 1 | 0 | 1 | 1 |  Ri+Si Ri+Si

|

| 1 | 1 | 0 | 0 |  Ri+Si Ri+Si

|

| 1 | 1 | 0 | 1 |  RiVSi RiVSi

|

| 1 | 1 | 1 |  0 0

| Ri^Si |

| 1 | 1 | 1 | 1 | RiVSi |

Таблица 3.2 - Специальные функции, реализуемые МПС.

Входы

Функция

Функция АЛУ F

Функция Сд. F

Состояние выводов

Функции Сд. Q и Рг. Q

Состояние выводов

I8

I7

I6

I5

PF3

PF0

PQ3

PQ0

W

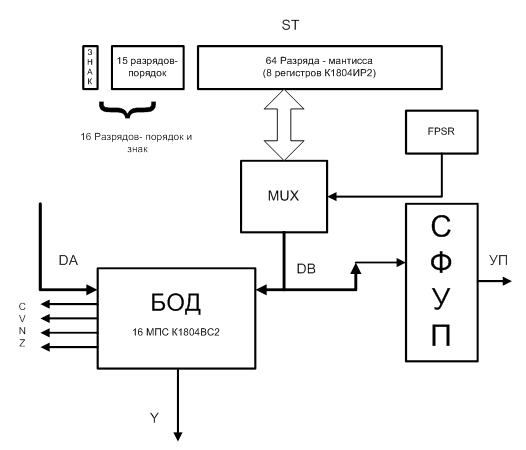

Блок с плавающей точкой

БПТ выполняет операции над числами с плавающей точкой, выполняет их приведение для последующей обработки.

БПТ построен на 16 МПС (К1804ВС2). Регистры РЗУ используются как рабочие. Всего РЗУ состоит из 16ти 64 разрядных регистров. Через мультиплексор из ST , а потом через шину DB, на БОД подаются 64 разряда мантиссы. Для определения вершины стека используется регистр SR. Через шину DY идёт обратная запись в стек 64 разрядов мантиссы. Через шину DA поступают данных из других источников данных. Схема ФУП используется для проверки условий перехода.

Построение БОД для плавающей точки и схема соединения аналогична БФТ.

Рис.3.3. Структурная схема БПТ

Управляющий автомат (УА)

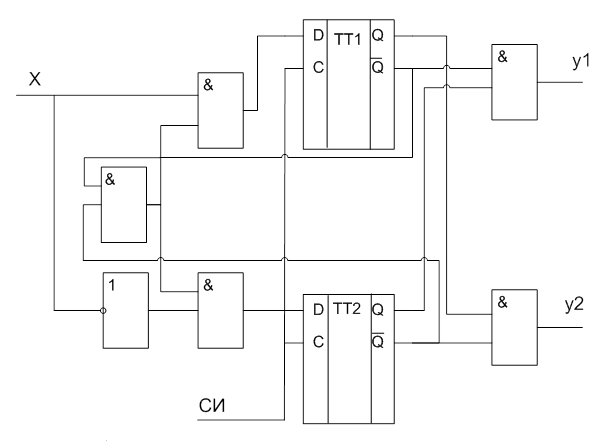

УА с жесткой логикой.

Управляющий автомат с жесткой логикой представляет собой конечный автомат, формирующий выходные сигналы управления в зависимости от текущего состояния и значений осведомительных входных сигналов.

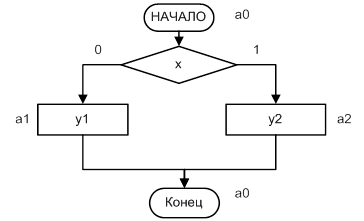

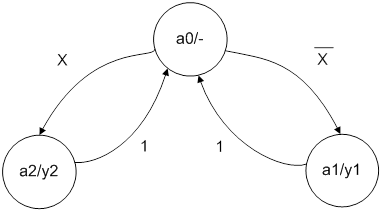

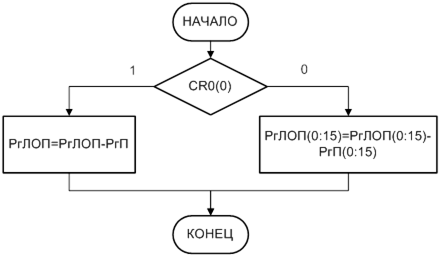

Составим управляющий автомат с жесткой логикой для выполнения команды SUB вычитания чисел в формате с фиксированной точкой.

Составляем отмеченную ГСА:

В условной вершине записываем элемент из множества логический условий X. В операторные вершины записываем операторы (микрооперации) y1 и y2 соответственно из множества микроопераций Y. Начальную и конечную вершины отмечаем символом a1, оставшиеся операторные вершины обозначаем а2 и а3.Находим пути перехода между операторными вершинами.

ГСА автомата имеет условную вершину: x - CR0 и 2 операторные вершины: a1 – Mem16 :=Mem16 - Reg[0..15], a2 – Mem32 :=Mem32 - Reg[0..31]

Рис. 3.4. ГСА алгоритма

Рис. 3.5. Граф автомата Мура

Так как имеется три состояния, то количество триггеров равно 2. (N=]log2n[)

Построение управляющего автомата будем осуществлять на D – триггере.

Таблица 3.3 - Структурная таблица.

| ai | Код ai | ai+1 | Код ai+1 | x | y | Сигналы возбуждения D1 D2 |

| Q1 Q2 | Q1 Q2 | |||||

| a0 | 0 0 | a1 | 0 1 |  x x

| 0 1 | |

| a0 | 0 0 | a2 | 1 0 | x | 1 0 | |

| a1 | 0 1 | a0 | 0 0 | 1 | y1 | 0 0 |

| a2 | 1 0 | a0 | 0 0 | 1 | y2 | 0 0 |

Функции переходов и выходов

D1 = !Q1!Q2 x

D2 = !Q1!Q2!x

y1 = !Q1Q2

y2 = Q1!Q2

Рис. 3.6. Автомат Мура

Регистровая память

Согласно регистровой модели и архитектуре регистровая память должна включать следующие регистры ССП ( СR0), EFLAGS, EIP – 32 разрядные, SR, TR, CR – 15 разрядные, ST() – 80 разрядные. РОНы реализованы внутри МПС, поэтому их описание не приводится. Также к регистровой памяти относятся регистры РгК, РгБ, РАОП, РгЗпОП, РгЧтОП.

32х разрядный регистр ССП(CR0) и регистр флагов EFLAGS, предусмотренные архитектурой IA-32, построены на 4 микросхемах К1804ИР2.

Счётчик команд EIP( 32 разряда) построен на четырёх микросхемах К1804ИР2. Счетчик адреса команд, входящий в EIP, представляет собой 23-разрядный регистр.

Status Register, TAG Register и Control Register также построены на 2 микросхемах К1804ИР2 каждый.

Регистр буфера представляет собой 56-разрядный регистр, который используется для предвыборки команды, с целью уменьшения количества обращений в ОП. Построен на 7 микросхемах К1804ИР2.

Регистры с плавающей точкой представляют собой 8 80-разрядных регистров, которые используются для хранения чисел с ПТ. Выполнены на 20 микросхемах К1804ИР2.

Регистр данных состоит из 32-разрядного регистра и служит для хранения операнда, извлеченного из ОП. Построен на 4 микросхемах К1804ИР2.

Описание К1804ИР2.

Микросхема К1804ИР2 – 8 разрядный параллельный регистр, предназначеннвй для применения в центральных процессорах.

Таблица 3.4 – Назначение выводов К1804ИР2.

| Вывод | Обозначение | Тип вывода | Функциональное назначение выводов |

| 1 | R | Вход | Обнуление регистра |

| 2 | DY0 | Выход | Данные, 0-й разряд |

| 3 | D0 | Вход | Данные, 0-й разряд |

| 4 | D1 | Вход | Данные, 1-й разряд |

| 5 | DY1 | Выход | Данные, 1-й разряд |

| 6 | DY2 | Выход | Данные, 2-й разряд |

| 7 | D2 | Вход | Данные, 2-й разряд |

| 8 | D3 | Вход | Данные, 3-й разряд |

| 9 | DY3 | Выход | Данные, 3-й разряд |

| 10 | C | Вход | Тактовый сигнал |

| 11 | GND | - | Общий |

| 12 | DY4 | Выход | Данные, 4-й разряд |

| 13 | D4 | Вход | Данные, 4-й разряд |

| 14 | D5 | Вход | Данные, 5-й разряд |

| 15 | DY5 | Выход | Данные, 5-й разряд |

| 16 | DY6 | Выход | Данные, 6-й разряд |

| 17 | D6 | Вход | Данные, 6-й разряд |

| 18 | D7 | Вход | Данные, 7-й разряд |

| 19 | DY7 | Выход | Данные, 7-й разряд |

| 20 | EZDY | Вход | Разрешение выходов данных |

| 21 | EWR | Вход | Разрешение записи |

| 22 | Uoc | - | Напряжение питания |

Оперативная память

Слово оперативной памяти составляет 8 байт.. Сама оперативная память рассматривается как черный ящик. Слово выбирается или записывается за одно обращение к памяти при помощи мультиплексоров и демультиплексоров. В состав ОП входят запоминающее устройство( РгЗпОП и РгЧтОП), регистр адреса. Чтение и запись в ОП инициируются сигналами ЧтОП и ЗпОп соответственно. 20 разрядный РгАОП, который хранит адрес команды, которая выполняется в текущий момент, построен на 5 микросхемах К1804ИР1. РгЧтОП и РгЗпОП построены на восьми 8 разрядных микросхемах К1804ИР2.

Блок интерфейса.

БИНТ служит для связи блоков процессора. Он состоит из мультиплексоров, лдемультиплексоров и логических схем согласующих передачу данных и управляющих сигналов.

Посредством БИНТ предоставляется возможность подачи на РгК необходимых разрядов из РгЧтОП или РгБ, осуществляется считывание необходимых байтов из РгК для обработки в БОД, выбор шин входных и выходных данных для БОД, запись в РгЗпОП слово, согласование работы РГЗпОП и ОП.

Также посредством БИНТ происходит выборка адресов регистров в БОД. Для пересылки данных из БПТ в БФТ и обратно также используется БИНТ. Управление БИНТ осуществляется подачей управляющих сигналов из БМУ. Для управления записью в регистры используются соответствующие линии. Выбор подаваемых данных на шины данных МПС также осуществляется посредством БИНТ. ( выбор источников для шин DA и DB)/

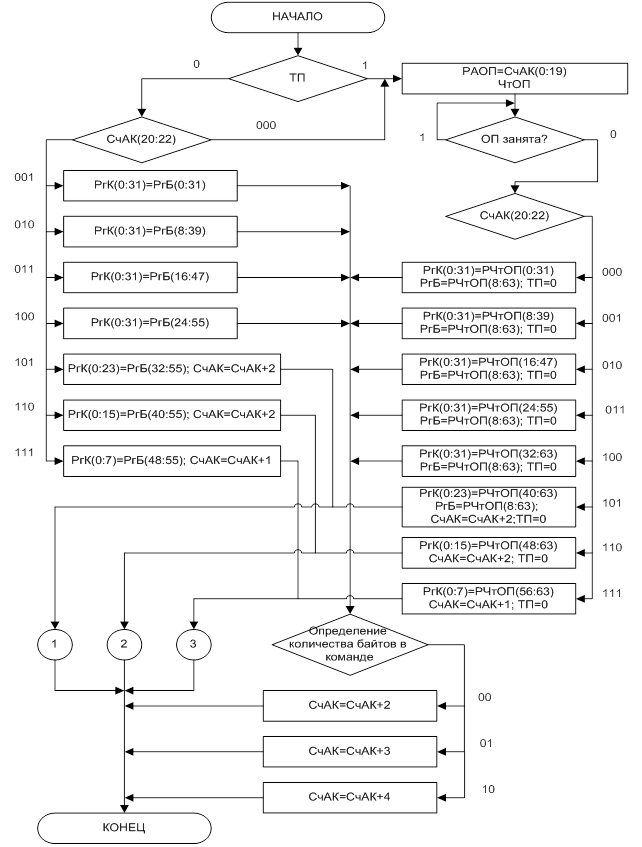

Выборка команд

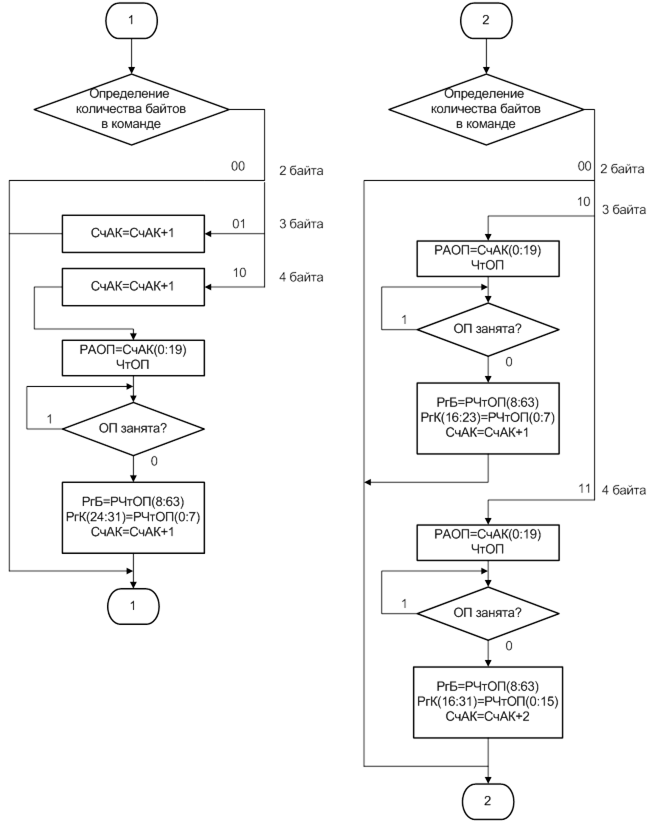

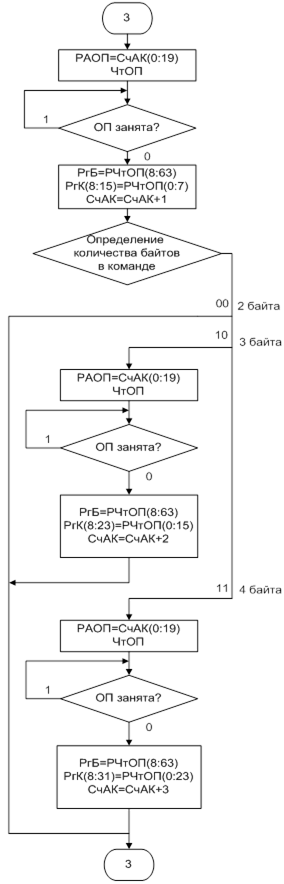

Перед началом выборки команды анализируется триггер перехода (ТП). Это позволяет определить, нужно ли обращаться к ОП или можно досчитать недостающую часть команды из регистра буфера (РгБ). При естественном порядке следования команд ТП принимает значение 0,в противном же случае он равен 1 ( например, при обработке прерываний происходит переход) и необходимо обращаться к ОП для считывания следующей команды. В зависимости от последних байтов СчАК, выбирается соответствующий начальный байт считывания из слова ОП. В случае, когда команда начинается с 5, 6 или 7 (нумерация с 0) байта, может возникнуть ситуация, что нужно будет досчитать команду с нового слова ОП, тогда в работу вступают алгоритмы 1, 2 и 3, где производится анализ по уже считанным байтам, что это за команда, её длина и определяется, нужно ли переходить на новое слово ОП. В зависимости от того, сколько байтов занимает команда ( блок условия определения количества байтов в команде), СчАК увеличивается на соответствующее значение.

Буфер позволяет значительно сократить количество обращений к ОП, так как в нём хранится конечная часть слова ОП, где находятся недостающие байты следующей команды.

Алгоритмы 1, 2 и 3 необходимы при ситуации, когда в регистр команд РГК загружено 3, 4 и 5 байтов команды соответственно и может оказаться , что нужно досчитать ещё 1, 2 или 3 байта.

Рис. 4.2. Выборка команды (первая стадия)

Рис. 4.3. Выборка команды (досчитывание 1 и 2)

Рис. 4.4. Выборка команды (досчитывание 3)

Рис. 4.5. Определение количества считываемых байтов

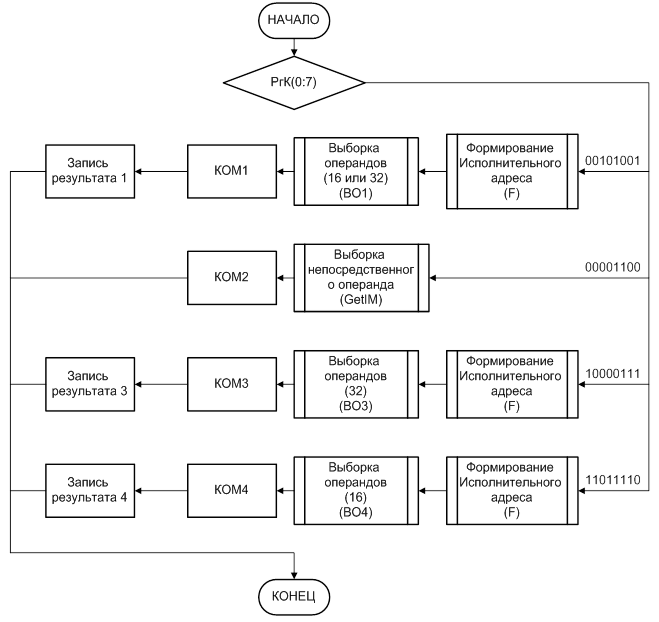

Порядок действий для каждой команды отличается, поэтому после декодирования происходит разветвление алгоритма. Необходимо заметить, что отличия не только в самой обработке данных, но и в алгоритмах их формирования, извлечения и записи результатов.

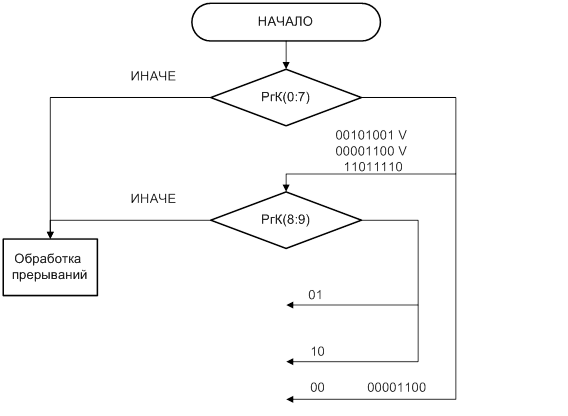

Рис. 4.6. Декодирование и определение последовательности действий для четырёх команд задания

Рис. 4.6. Декодирование и определение последовательности действий для четырёх команд задания

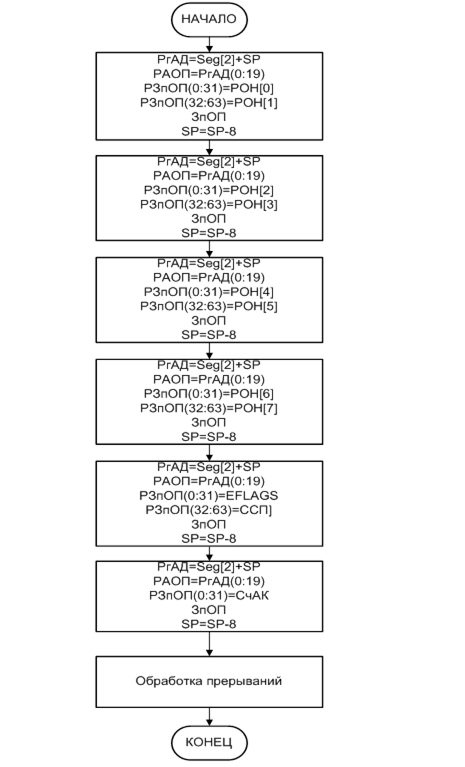

Обработка прерываний

При обработке прерываний сначала происходит сохранение сегментных регистров, затем РОНов и наконец регистра ССП, СчАК и регистра флагов EFLAGS в стек.

Рис. 4.7. Обработка прерываний

4.5 Выполнение четырех операций из индивидуального задания

Выполнение команд с фиксированной точкой не представляет особого труда, так как операции в них реализуются в МПС моего варианта (вычитание и логическое ИЛИ). Соответственно алгоритмы также не очень сложны. Команда обмена данными между регистром и памятью тоже реализуется в небольшом алгоритме. При написании алгоритмов учитывалось, что процессор может работать в разных режимах, поэтому анализировался регистр ССП.

Формирование признаков результата происходит на аппаратном уровне. Это не требует записи флагов на уровне микропрограммирования и не отражается на алгоритмах выполнения операций.

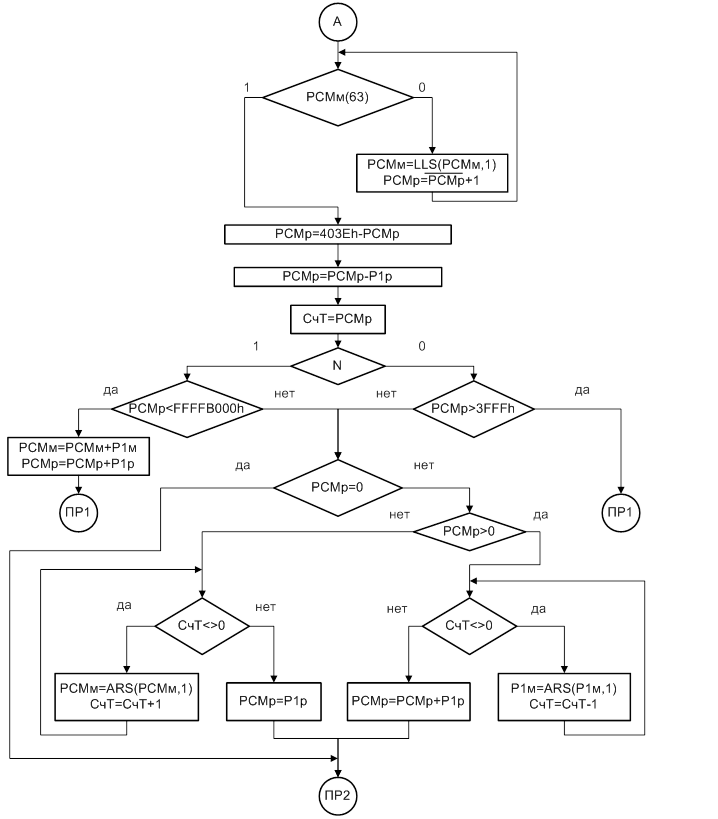

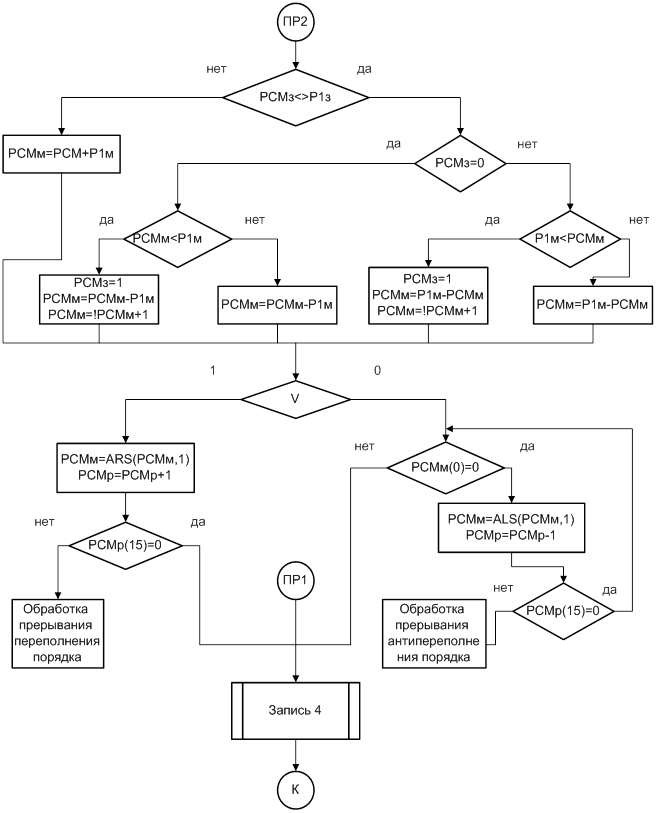

Составление же алгоритма для чисел с плавающей точкой потребовало более глубокого понимания и осмысления.

Мантисса и знаки обрабатываются в БПТ (РСМм, Р1м, РСМз, Р1з), порядок же обрабатывается в БФТ (для однообразия и внесения смысловой нагрузки для упрощения понимания алгоритма создадим соответствие Р1р, РСМр – это порядки в БФТ. Рр1 это РгП, РСМр - это РгЛОП ( операнд из памяти). Изначально в РСМр целое число со знаком.

Первым шагом является приведение целого числа к формату числа с ПТ: определение знака числа (находится ли в доп. коде и нужно ли преобразовывать в прямой, так как мантисса хранится в прямом коде), нахождение мантиссы порядка (сдвиг числа влево в подсчётом количества совершённых сдвигов).

Затем реализуется сам алгоритм сложения с учётом возможных особых случаев ( переполнение, антипереполнение порядка, потеря точности).

Кратко алгоритм можно описать так:

1. Производится выравнивание порядков чисел. Порядок меньшего (по модулю) числа принимается равным порядку большего числа, а мантисса меньшего числа сдвигается вправо на число S-ичных разрядов, равное разности порядков чисел.

2. Производится сложение мантисс, в результате чего получается мантисса суммы.

3. Порядок результата принимается равным порядку большего числа.

4. Полученная сумма нормализуется.

При сравнении порядков возможны пять случаев:

1) px-py>m (m— число разрядов мантиссы). В качестве результата суммирования сразу же может быть взято первое слагаемое, так как при выравнивании порядков все разряды мантиссы второго слагаемого принимают нулевое значение;

2) px-py>m. В качестве результата суммирования может быть взято второе слагаемое;

3) .px-py=0. Можно приступить к суммированию мантисс;

4) px-px=k1 (k1<m) Мантисса второго слагаемого сдвигается на разрядов вправо, затем производится суммирование мантисс;

5) py-px=k2 (k2<m) Перед выполнением суммирования мантисс производится cдвиг на разрядов вправо мантиссы первого слагаемого.

За порядок результата при выполнении суммирования принимается больший из порядков операндов.

Рис. 4.15. Выполнение команды КОМ1

Рис. 4.16. Запись результата КОМ1

Рис. 4.16. Запись результата КОМ1

Рис. 4.17. Выполнение команды КОМ2

Рис. 4.18. Выполнение команды КОМ3

Рис. 4.19. Запись результата КОМ3

Рис. 4.20. Довыборка операндов (ВО4)

Рис. 4.21. Выполнение команды КОМ4 (начало)

Рис. 4.21. Выполнение команды КОМ4 (начало)

Рис. 4.22. Выполнение команды КОМ4 (окончание)

Рис. 4.22. Выполнение команды КОМ4 (окончание)

Рис. 4.23. Запись результата КОМ4

Микропрограммное управление

Формат микрокоманды

Таблица 5.1 –Формат микрокоманды.

| Зона | Поле | Количество разрядов | Значение по умолчанию | |

| БФТ | MUXA MUXB ИСТ УВП АЛУ СДВ РЕЗ А В | 2 2 3 2 4 3 3 4 4 | 0 0 0 0 6 C 0 0 0 | |

| БПТ | ИСТ УВП АЛУ СДВ РЕЗ А В | 3 2 4 3 3 4 4 | 0 0 6 C 0 0 0 | |

| БМУ | УСА ФУ И АП УСЛ RLD БУ ВБ | 4 1 1 12 3 1 1 1 | E 1 0 0 0 1 0 1 | |

| БИНТ | БФТ | MUXDAФТ MUXDBФТ DMXDYФТ DMXDBФТ | 2 3 2 1 | 0 0 0 0 |

|

| БПТ | MUXDAПТ DMXDYПТ MUXDBПТ | 1 2 1 | 0 0 0 |

| ОП | MUXЗП DMXОП MUXБЧ MUXСА | 3 1 1 1 1 1 1 1 | 0 0 0 0 0 0 0 0 | |

| Рг | СчАК РгАД РгБ РгК | |||

| ОП | R/W РАОП РгЧтОП РгЗпОП CS | 1 1 1 1 1 | 0 0 0 0 0 | |

| CONST |

| 64 | 0 | |

Таблица 5.1 (продолжение)

Зона БФТ.

Зона состоит из семи полей.

Для адресных входов, в зависимости от того, откуда адреса A и B, разрешены не все возможные адреса. Таким образом, на вход А и B старшим битом всегда должен подаваться 0, если разрешён адресный вход из РгК. Так как в БФТ у меня находится только 2 рабочих регистра - 15 и 16 (оставшиеся отведены под сегментные регистры), то при адресации из РгМК на старшие адресные входы должны подаваться три единицы. Распределение адресов и соответствующих им регистров приведено в разделе 2 (2.4.5 Регистры БОД) .

Поля MUXA и MUXB управляют выбором адреса РЗУ, возможными значениями которого являются адрес регистра из БМУ, регистр из РгК (поле reg или поле r/m). “+” указывает на значение полей по умолчанию.

Таблица 5.2 – Поле MUXA..

| MUXA | Источник |

| 00 01 10 11 | Адрес из БМУ РгК(10:12) РгК(13:15) - |

Таблица 5.3 - Поле MUXB.

| MUXB | Источник |

| 00 01 10 11 | Адрес из БМУ РгК(10:12) РгК(13:15) - |

| ИСТ | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| EA OEB I0 | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

| Операнд R | РгA | РгA | РгA | РгA | DA | DA | DA | DA |

| Операнд S | РгB | РгQ | DB | РгQ | РгB | РгQ | DB | РгQ |

Таблица 5.4 - Поле ИСТ.

Таблица 5.5 - Поле УВП.

| УВП | Значение переноса |

| 00 01 01 11 | 0 1 C C |

Таблица 5.6 - Поле АЛУ.

| АЛУ | Операция АЛУ | |||

| 0 | 0 | 0 | 0 | Специальные функции при IO=0 |

| 0 | 0 | 0 | 0 | 1111 при IO=1 |

| 0 | 0 | 0 | 1 | S-R-1+CO |

| 0 | 0 | 1 | 0 | R-S-1+CO |

| 0 | 0 | 1 | 1 | R+S+CO |

| 0 | 1 | 0 | 0 | S+CO |

| 0 | 1 | 0 | 1 |  S+CO S+CO

|

| 0 | 1 | 1 | 0 | R+CO |

| 0 | 1 | 1 |  1 1

| R+CO |

| 1 | 0 | 0 | 0 | 0000 |

| 1 | 0 | 0 |  1 1

| Ri^Si |

| 1 | 0 | 1 | 0 |  Ri Ri  Si Si

|

| 1 | 0 | 1 | 1 | Ri  Si Si

|

| 1 | 1 | 0 | 0 | Ri^Si |

| 1 | 1 | 0 | 1 |  RiVSi RiVSi

|

| 1 | 1 | 1 | 0 |  Ri^Si Ri^Si

|

| 1 | 1 | 1 | 1 | RiVSi |

Таблица 5.7 - Поле СДВ.

| СДВ | Операция АЛУ | |||

| 0 | 0 | 0 | 0 | АС ALU вправо |

| 0 | 0 | 0 | 1 | ЛС ALU вправо |

| 0 | 0 | 1 | 0 | АС ALU, ЛС RGQ вправо |

| 0 | 0 | 1 | 1 | ЛС ALU, ЛС РгQ вправо |

| 0 | 1 | 0 | 0 | без сдвига |

| 0 | 1 | 0 | 1 | ЛС РгQ вправо |

| 0 | 1 | 1 | 0 | РгQ:=ALU |

| 0 | 1 | 1 | 1 | РгQ:=ALU |

| 1 | 0 | 0 | 0 | AC ALU влево |

| 1 | 0 | 0 | 1 | ЛС ALU влево |

| 1 | 0 | 1 | 0 | AС ALU, ЛС РгQ влево |

| 1 | 0 | 1 | 1 | ЛС ALU, ЛС РГQ влево |

| 1 | 1 | 0 | 0 | без сдвига |

| 1 | 1 | 0 | 1 | ЛС РгQ влево |

| 1 | 1 | 1 | 0 | расширение знака |

| 1 | 1 | 1 | 1 | без сдвига |

Таблица 5.7 (продолжение)

Таблица 5.8 - Поле РЕЗ.

| РЕЗ | OEY WE IEN | Передача информации |

| 0 1 2 3 4 5 6 7 | 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 | Y, РЗУ = СДВ; РгQ =АЛУ Y, РЗУ = СДВ Y = СДВ; РгQ = АЛУ Y = СДВ РЗУ = Y; РгQ = АЛУ РЗУ = Y РгQ = АЛУ Нет записи |

Зона БПТ.

Большинство полей в БПТ повторяют поля БФТ: ИСТ, УВП, АЛУ, СДВ, РЕЗ, А и В. Только для БПТ адрес считывается только из РгМК, в отличие от БФТ и в БПТ располагаются только рабочие регистры.

На адресные входы A и B может подаваться любая четырёх битная комбинация, так как все регистры в БПТ рабочие, а стек вынесен за пределы БПТ.

Таблица 5.9 – Значение полей А/В.

| Значение | Регистр |

| 0000 | Р1з |

| 0001 | Р1м |

| 0010 | РСМз |

| 0011 | РСМм |

| 0100 | СчТ |

| 0101 | РПТ1 |

| 0110 | РПТ2 |

| 0111 | РПТ3 |

| 1000 | РПТ4 |

| 10001 | РПТ5 |

| 1010 | РПТ6 |

| 1011 | РПТ7 |

| 1100 | РПТ8 |

| 1101 | РПТ9 |

| 1110 | РПТ10 |

| 1111 | РПТ11 |

Зона БМУ.

Поле УСА ( управление следующим адресом) принимает значение E по умолчанию, что соответствует последовательному выполнению команд. Для условного перехода в него записывается значение 3.

Поле П разрешает безусловный переход по адресу, записанному в АП.

Поле УСЛ отвечает за выбор условия перехода.

ФУ - фиксация флагов.

И - инверсия условия.

RLD – разрешение записи в Cч/РгА.

ВБ - выбор секции, для которой анализируются условия. 0 – для БФТ, 1 - для БПТ.

АП – адрес перехода. Адрес перехода размещён в отдельном поле, а не с поле CONST, так как поле CONST может использоваться для записи какой-либо константы и одновременно нужно организовать переход по адресу. Поэтому эти поля разделены.

| УСЛ | Переход | |

| 000 | Переход по паритету | PF0 = 1 |

| 001 | При равенству 0 | Z =1 |

| 010 | При отрицат. знак | N = 1 |

| 011 | При переполнении | V = 1 |

| 100 | При переносе | C = 1 |

| 101 | Если меньше | N + V = 1 |

| 110 | Если меньше или равно | Z v (N + V ) = 1 |

| 111 | Если меньше или равно без знака | C v Z = 1 |

Таблица 5.10 - Поле УСЛ.

Зона БИНТ.

Поле БФТ БИНТ

Источником данных для шины DA БФТ могут быть поле CONST из РгМк, операнд из РгЧтОП, передаваемый через мультиплексор MUXРежЧ, а также выход БПТ через DMXDYПТ.

Таблица 5.11 – MUXDAФТ.

| MUXDAФТ | Источник |

| 00 | CONST из РгМК |

| 01 | MUXРежЧ |

| 10 | DMXDYПТ |

Источником данных для шины DB БФТ может быть непосредственный операнд из РгК(8:15), СчАК( для инкремента), смещение из РГК(16:23) или РгК(16:31) и порядок из БПТ через MUXSTPor.

Таблица 5.12 – MUXDBФТ.

| MUXDBФТ | Источник |

| 000 | РгК(8:15) |

| 001 | СчАК |

| 010 | РгК(16:23) |

| 011 | РгК(16:31) |

| 100 | MUXSTPor |

Выходом БФТ могут быть шина DA БПТ через MUXDAПТ, РгАД, СчАК или РГЗпОП через MUXЗП

Таблица 5.13 – DMXDYФТ.

| DMXDYФТ | Направление |

| 00 | MUXDAПТ |

| 01 | РгАД |

| 10 | СчАК |

| 11 | MUXЗП |

Выходом шины DB может быть либо РгЗпОП через MUXЗП, либо разряд порядка мантиссы для стекового регистра через DMXSTPor

Таблица 5.14 – DMXDBФТ.

| DMUXDBФТ | Направление |

| 0 | MUXЗП |

| 1 | DMXSTPor |

Поле БПТ БИНТ

Источником данных для шины DA БПТ могут быть поле CONST из РгМк, и выход Y БПТ через DMXDYФТ.

Таблица 5.15 – MUXDAПТ.

| MUXDAПТ | Источник |

| 0 | CONST из РгМК |

| 1 | DMXDYФТ |

Выходами шины DY БПТ могут быть входная шина DA БФТ через MUXDAФТ, разряды стека, где хранится мантисса ( через DMXSTMan) и разряды стека, где хранится знак ( через DMXSTZn)

Таблица 5.16 – DMXDYПТ.

| DMXDYПТ | Направление |

| 00 | MUXDAФТ |

| 01 | DMXSTMan |

| 10 | DMXSTZn |

Входаvи шины DB могут быть либо мантисса через MUXSTMan или знак через MUXSTZn.

Таблица 5.17 – MUXDBПТ.

| MUXDBПТ | Направление |

| 0 | MUXSTMan |

| 1 | MUXSTZn |

Поле ОП БИНТ

Входами мультиплексора записи MUXЗП могут быть выходы шины DB, DY,СчАК ( при сохранении при прерывании) и ССП( CR0) по той же причине.

Таблица 5.18 – MUXЗП.

| MUXЗП | Источник |

| 000 | DMXDBФТ |

| 001 | DMXDYФТ |

| 010 | СчАК |

| 011 | ССП (CR0) |

| 100 | EFLAGS |

Таблица 5.18 (продолжение)

Запись в РгК может вестись либо напрямую из РгЧтОП, либо через РгБ. Для выбора необходимых байтов используется MUXЧ после которого и идёт запись в РгК. Иначе же ведётся запись из РгБ через соответствующие мультиплексоры.

Таблица 5.19 – DMXОП.

| DMXОП | Направление |

| 0 | РгБ |

| 1 | MUXЧ |

Входом записи РгК могут быть РгБ через MUXБ или РгЧтОП через MUXЧ. Выбор источника осуществляется в MUXБЧ

Таблица 5.20 – MUXБЧ.

| MUXБЧ | Источник |

| 0 | MUXБ |

| 1 | MUXЧ |

Мультиплексор MUXСА выбирает, откуда будет произволиться запись в РАОП – из СчАК или РгАД.

Таблица 5.21 – MUXСА.

| MUXСА | Источник |

| 0 | СчАК |

| 1 | РгАД |

Также в поле БИНТ есть поле Рг. В нём определяется в какие из регистров возможна запись. Это регистры СчАК, РгК, РгАД, РгБ.

Зона ОП

Поле используется для управления записи или считывания данных из ОП.

Сигнал CS определяет выбрана ли ОП или нет. Сигналы R/W задают соответственно чтение из ОП в РгЧтОП или запись в РгЗпОП соответственно.

Также зона разрешает запись.

Таблица 5.22 – Зона ОП

| CS | R/W | Режим работы ОП |

| 0 | 0 | нет доступа |

| 0 | 1 | нет доступа |

| 1 | 0 | ОП := РгЗпОП |

| 1 | 1 | РгЧтОП := ОП |

Зона CONST

Зона используется для определения константы, например для операций сравнения в условиях или для выделения битов по маске.

Заключение

В ходе выполнения курсового проекта были приобретены навыки проектирования операционного и управляющего автоматов процессора ЭВМ. Результатом проектирования стал разработанный 32-разрядный секционированный микропроцессор с архитектурой IA-32, построенный в базисе МПС К1804ВС2 способный выполнять четыре команды: SUB, OR, XCHG и FIADD. Также были приобретены навыки составления технической документации и выполнения чертежей по нормам ЕСКД.

На мой взгляд, одним из достоинств данного курсового проекта является то, что микропроцессор изучался и проектировался полностью, а не какой-либо его отдельный блок. Тем самым были определены и поняты связи и взаимодействие его компонентов, неотделимость их друг от друга. Особенно важными для этого оказались последние стадии проекта, где разрабатывались алгоритмы цикла работы процессора и 3 схемы из технического задания.

Литература

1. Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 1: Basic Architecture, 470 p. 253665.pdf

2. Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 2A: Instruction Set Reference, A-M, 758 p. 253666.pdf

3. Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 2B: Instruction Set Reference, N-Z, 618 p. 253667.pdf

4. Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 3A: System Programming Guide, Part 1, 646 p. 253668.pdf

5. ГОСТ 2.105-95. Единая система конструкторской документации. Общие требования к текстовым документам.

6.Хамахер К., Вранешич З., Заки С. Организация ЭВМ. – 5-е изд.- С-Пб.: Издательская группа BHV, 2003. - 848 с. - ISBN 5-8046-0162-8.

Введение

Интенсивное развитие микроэлектроники и повышения степени интеграции открыли новое направление в ВТ - создание микропроцессоров и микрокомпьютеров. Появились вычислительные системы с малым уровнем потребления энергии и универсальными возможностями, которые позволяют решать задачи управления объектами различной физической природы. На основе их применения снижаются затраты на автоматизацию основных технических и вспомогательных процессов. В результате будет решена задача комплексной автоматизации производства во всех отраслях. Это позволит увеличить производительность труда, уменьшить себестоимость выпускаемой продукции и значительно сократить ручные операции в промышленности. Однако для широкого развития работ в данном направлении необходимо готовить значительное число инженеров - системотехников, умеющих создавать и применять микропроцессоры и микрокомпьютеры. Кроме того, следует выпускать и много инженеров - математиков, разрабатывающих соответствующее программное обеспечение. Для их обучения необходимо иметь учебные пособия, посвященные аппаратным и программным средствам современной вычислительной техники.

Цель курсового проекта состоит в приобретении практических навыков в проектировании операционного и управляющего автоматов процессора ЭВМ в соответствии с заданными в техническом задании архитектурными особенностями, а также в разработке технической документации, представленной пояснительной запиской и чертежами, выполненными в соответствии с ЕСКД.

Задание на КП

Аспекты разработки процессора

Объектом курсового проектирования является процессор цифровой ЭВМ широкого назначения. Проектируемый процессор должен реализовывать заданную совокупность машинных команд, соответствующих вычислительным системам с архитектурой IA-32. Процесс разработки процессора включает следующие основные шаги:

1) ознакомление с системой заданных машинных команд и архитектурой IA-32,

2) синтез структуры операционных автоматов блоков обработки данных в базисе микропроцессорных секций (МПС) или программируемых логических интегральных схем (ПЛИС),

3) синтез управляющих автоматов с жесткой и микропрограммируемой логикой,

4) разработка математического обеспечения в виде алгоритмов реализации цикла работы процессора и выполнения заданного набора команд,

5) формирование микрокоманды и составление микропрограммы выполнения операции из заданного набора над числами с плавающей точкой,

6) разработка электрических схем (структурной, функциональной и принципиальной) и оформление пояснительной записки.

Исходные данные для проектирования

Набор команд: 18, 57, C2, E2.

Таблица 1. 1 - Команды процессора

| Номер команды | Код операции | Операция | Описание |

| Операции над целыми числами (арифметические) | |||

| 18 | 29h | Sub Mem16, Reg16 Sub Mem32, Reg32 | Mem16 – Reg16->Mem16 Mem32 – Reg32->Mem32 |

| Операции над целыми числами (логические и сдвиги) | |||

| 57 | 0Ch | OR AL, im8 | Al or im8->AL |

| Операции пересылки | |||

| C2 | 87h | XCHG Mem32, Reg32 | Mem32->Tmp Reg32->Mem32 Tmp->Reg32 |

| Операции над числами с плавающей точкой | |||

| E2 | DB/0h | FIADD m16int | m16int+ST(0)->ST(0) |

Таблица 1.2 - Параметры процессора и оперативной памяти

| Ёмкость оперативной памяти, Мб | 8 |

| Длина слова оперативной памяти, байт | 8 |

| Базис реализации процессора | МПС К1804 ВС2 |

| Способ адресации | Базовая EA (0:15) |

Архитектура процессора

Форматы команд

Дата: 2019-12-10, просмотров: 445.