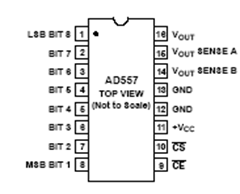

ЦАП формирует цифровой вход предела верхней температуры из аналогового кода, взятого с регистра записи. В качестве ЦАП испольем микросхему AD557.

Регистр чтения

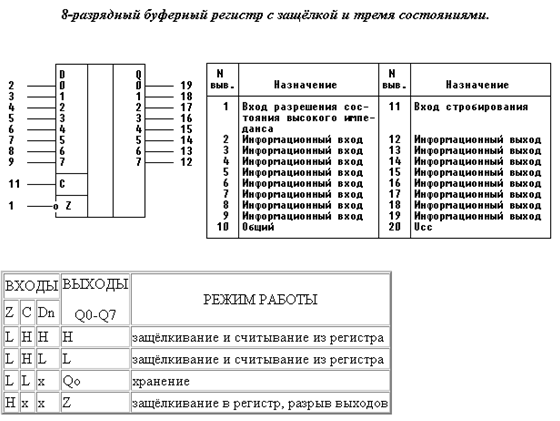

Для передачи данных от АЦП на шину используется микросхема 54AC373/2A.

| T°C | Icc,мкА | Направление Прохождения Сигнала | Ttip, нс | Tmax, нс | Тип корпуса |

| -55...125° | < 8 | D→Q | 8,5 | 12,5 | 20LCC |

Для управления регистром используются сигналы V. На этот вывод будет подаваться строб чтения данных –RD. При появлении на входе С регистра лог.1 в регистр записывается информация о состоянии температуры на датчике. При подачи на вход V лог. 1 регистр выводит информацию на выходы.

Транслятор прерывания

Для управления аппаратными прерываниями во всех типах IBM PC в прошлом использовались микросхемы программируемого контроллера прерываний Intel 8259. В современных компьютерах данная микросхема интегрирована в состав их контроллера прерываний. Поскольку в каждый момент времени может поступить не один запрос, микросхема имеет схему приоритетов. В IBM PC AT имеется 15 уровней приоритетов и 1 уровень для каскадирования контроллеров прерываний. Обращения к соответствующим уровням обозначаются сокращениями от IRQ0 до IRQ15, которые означают сигналы запросов на прерывание. Максимальный приоритет соответствует уровню 0. Уровни IRQ0-IRQ7 обрабатываются первой микросхемой 8259, а добавочные 8 уровней обрабатываются второй микросхемой 8259; этот второй набор уровней имеет приоритет между IRQ2 и IRQ3. Запросы на прерывание 0-7 соответствуют векторам прерываний от 8H до 0FH; прерывания 8-15 обслуживаются векторами от 70H до 77H.

Для разрабатываемого адаптера выбираем зарезервированный уровень прерываний IRQ10. Данному уровню соответствует вектор 72h.

Для осуществления прерываний от устройств ввода/вывода должно выполняться два условия:

1) Формирователь прерываний должен иметь тристабильный выход. 2) Запрос на прерывание должен программно сниматься.

В данной работе формирователь запросов на прерывания построим из D-триггера, на вход синхронизации которого будет подаваться сигнал готовности АЦП –Z0.

В качестве D-триггера используется микросхема КР15554ТМ2.

Описание временных диаграмм

Начало цикла записи/чтения устройства ввода/вывода начинается с такта T – такта статуса. Он, как и другие такты, длится 125 нс. В этом первом такте по заднему фронту сигнала SysCLK (сигнал системного тактового генератора) формируется сигнал BALE (сигнал стробирования адресных разрядов, разрешение защелкивания адреса). По переднему фронту сигнала BALE начинается установка адреса на линиях SA0-SA9 (это значащие линии для проектируемого устройства).

Суммарная временная задержка распространения сигнала через селектор адреса составляет 47,5 нс: 6 нс для элемента DD1, 35 нс для элемента DD4, 6,5 нс для элемента DD5.

Если с магистрали пришла команда записи -IOW, то через время задержки на элементах DD2.3 (6 нс), DD7.1 (14 нс), равной 20 нс, формируется передний фронт сигнала WR, по которому происходит фиксация данных подаваемых с шины на вход регистра DD3. После времени задержки на микросхеме DD3 (6,7 нс) записанные данные поступают на управляющие выводы АЦП.

После снятия команды записи формируется задний фронт сигнала WR.

Если с магистрали пришла команда чтения -IOR, то через время задержки на элементах DD2.4 (6 нс) и DD7.2 (14 нс), равное 20 нс, формируется передний фронт сигнала RD, по которому происходит фиксация данных на выходах формирователя DD11, DD12 и сброс запроса на прерывание. Команда чтения данных используется во время выполнения процедуры обработки прерывания. Через время задержки на элементе DD11, DD12, равное 7 нс, сигнал чтения разрешает выдачу байта на шину. Фиксация данных при чтении происходит по заднему фронту команды чтения, т.е. для правильной работы устройства необходимо обеспечить выставление и удержание байта до заднего фронта -IOR и удержание данных после его снятия в течении 7 нс.

Временные диаграммы чтения и записи приведены в графической части записки (листы 3,4).

Дата: 2019-07-31, просмотров: 327.