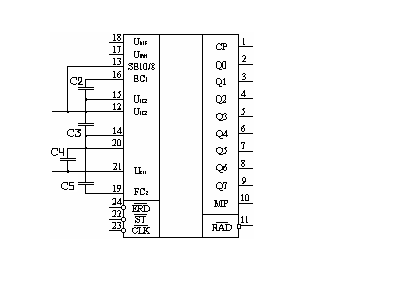

Мы используем микросхему быстродействующего функционально законченного АЦП последовательного приближения К1108ПВ1А предназначенную для преобразования аналогового сигнала в двоичный параллельный цифровой код.

Микросхема расчитана на преобразование однополярного входного напряжения в диапазоне от 0 до 3 В, при максимальной частоте преобразования 1,33 МГц для восьмиразрядного режима.

Для работы АЦП К1108ПВ1А требуется несколько внешних керамических конденсаторов и источники напряжения Ucc1 = 5 В ± 5% и Ucc2 = -5,2 В±5%. Мощность потребляемая от источников питания, не превышает 0,85 Вт. Конденсатор С5 необходим для частотной коррекции ОУ и фильтрации помех.

Для работы в восьмиразрядном режиме вход SE10/8 соединяется с шиной отрицательного источника питания Ucc2 .

Цикл преобразования в режиме восьмиразрядного АЦП состоит из 10 тактов (восемь рабочих в процессе кодирования и по одному служебному в начале и конце цикла преобразования).

Цикл начинается с первым отрицательным фронтом тактового импульса после поступления команды ST. Во время первого служебного такта осуществляется сброс регистров и установление напряжения на входе селектора опорных уровней.

В течение следующих восьми тактов происходит кодирование аналогового сигнала при условии, что он зафиксирован на входе АЦП.

На десятом такте код из регистра хранения переписывается в выходной регистр, после чего формируется сигнал готовности данных. Появление на выходе RAD сигнала логический 0 свидетельствует о смене информации в выходном регистре и ее хранении весь следующий цикл преобразования.

Для считывания информации необходимо подать на вход ERD сигнал логический 0.

Запуск АЦП считается устойчивым, если сигнал ST подается в течение одного периода тактовой частоты с момента начала очередного цикла (t = 1мкс).

К ТТЛ ЦИС микросхема К1108ПВ1А подключается без дополнительных устройств сопряжения.

Рис.3. ИС К1108ПВ1А

Назначение выводов ИС

1. Цифровой выход CP

2. Цифровой выход

3. Цифровой выход

4. Цифровой выход

5. Цифровой выход

6. Цифровой выход

7. Цифровой выход

8. Цифровой выход

9. Цифровой выход

10. Цифровой выход MP

11. Готовность данных RAD

12. Напряжение питания Ucc2

13. Укороченный цикл SE10/8

14. Общий (цифровая земля)

15. Напряжение питания Ucc2

16. Коррекция СУ EC1

17. Аналоговый вход UIRN

18. Внешний ИОН UREF

19. Коррекция ОУ ИОН FC2

20. Общий (аналоговая земля)

21. Напряжение питания Ucc1

22. Запуск ST

23. Тактовый вход CLK

24. Разрешение считывания ERD

Микросхема К1108ПВ1А имеет следующие характеристики

( Ucc1 = 5,25 В; Ucc1 = -5,25 В; U1вых ³ 2,4 В; U0вых £ 0,4 В; Iпотр сс1 £ 50 мА;

Iпотр сс2 £ 130 мА; I0вх £ 2,5 мА; I1вх £ 0,4 мА; I0вых ³ 3,2 мА; I1вых ³ 0,1 мА; tздр £ 60 нс )

Потребляемая мощность микросхемы К1108ПВ1А равна:

Pпотр £ 850 мВт

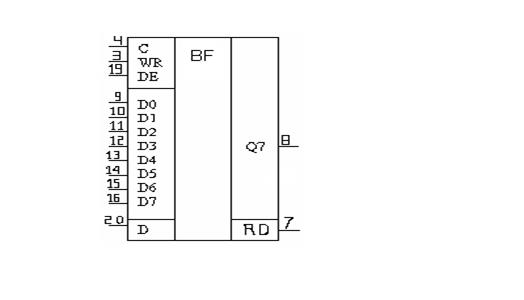

Буфер FIFO

Преобразователь параллельного цифрового кода в последовательный код построен на базе микросхемы Hitachi MBF1250. Микросхема Hitachi MBF1250 – это буфер типа FIFO(First Input First Output) с размером матрицы 128Кx8 и, по сути дела представляет собой последовательно соединённые параллельные восьмиразрядные регистры сдвига. Микросхема работает в двух режимах: когда на входе управления появляется сигнал высокого уровня, он запускает первый генератор, систему управления АЦП, при этом происходит запись восьмиразрядных кодов из АЦП в буфер; во втором режиме, когда сигнал управления сообщает об отсутствии информации на входе АЦП, происходит остановка работы первого генератора и самого АЦП, при этом запускается второй генератор, синхронизирующий работу буфера, производящего выгрузку данных. Назначение выводов:

Рис.4. Буфер Hitachi MBF1250

1. Питание Ucc

2. Общий GND

3. Запись ®WR Вход D4

4. Тактовый вход C Вход D5

5. Вход D6

6. Вход D7

7. Разрешение на чтение

8. Прямой выход Q7

9. Вход D0

10. Вход D1

11. Вход D2

12. Вход D3

13. Вход D4

14. Вход D5

15. Вход D6

16. Вход D7

19. Задержка такта DE

20. Последовательный вход D®

Дата: 2019-07-30, просмотров: 310.