Эквивалентные схемы элементов, представленных выше, можно получить, используя только PMOS-транзисторы. Однако наибольший интерес представляет совместное применение PMOS и NMOS-транзисторов. Такая технология наиболее популярна сегодня и называется CMOS-технологией. Она обеспечивает максимальное быстродействие работы элементов при низком энергопотреблении по сравнению со всеми другими технологиями.

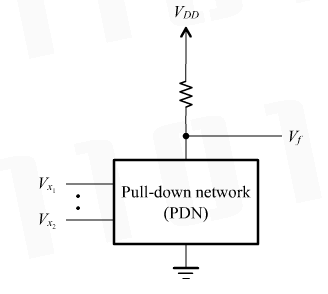

В NMOS-цепях логические функции реализовались комбинацией соединений NMOS-транзисторов, объединенных с токоограничивающим элементом.

Т.к. все элементы, построенные на NMOS-транзисторах реализуют отрицательные функции (НЕ, ИЛИ-НЕ, И-НЕ), то их можно условно представить так, как показано на блок-схеме рисунка 1.9

.

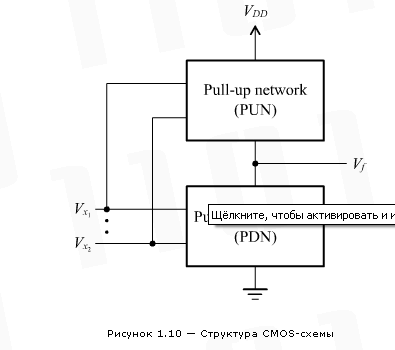

При этом все транзисторные цепи объединены в блок PDN (Pull-down Network) – блок отрицательной логики. Для реализации прямых логических функций необходимо соединение двух отрицательных элементов, что снижает быстродействие всего элемента в целом. Концепция CMOS-цепей основана на реализации прямых функций (И, ИЛИ) на PMOS-транзисторах таким образом, что блоки прямой логики (PUN – Pull-up Network) и блоки отрицательной логики (PDN — Pull-down Network) являются дополнениями друг друга. Тогда логическая схема, реализующая типичный логический элемент, будет иметь вид, представленный на рисунке 1.10.

Для любой комбинации входных сигналов PDN устанавливает уровень логического нуля на выходе Vf , или PUN устанавливает на этом выходе уровень логической единицы. PDN и PUN имеют равное количество транзисторов, которые размещены так, что эти два блока работают параллельно. Там, где PDN включает NMOS-транзисторы, соединенные последовательно, PUN строится на PMOS-транзисторах, соединенных параллельно, и наоборот.

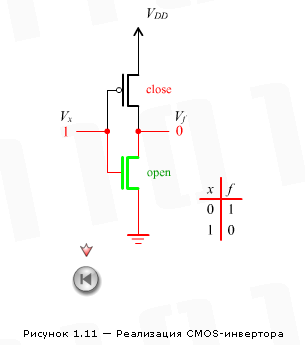

Самый простой пример CMOS-схемы — инвертор, показан на рисунке 1.11.

Когда сигнал Vx=0V, транзистор T2 закрыт, а транзистор T1 открыт. Следовательно, Vf=5V, и так как T2 закрыт, ток через транзисторы не течет. Когда Vx=5V, то T2 открыт, а T1 закрыт. Таким образом, Vf=0V, и тока в цепи по прежнему не будет, т.к. транзистор T1 закрыт . Это свойство справедливо для всех CMOS-цепей – логические элементы практически не потребляют ток в статическом режиме. Ток в таких цепях будет протекать только во время переключения элементов (вот почему, с ростом частоты работы устройств, построенных по этой технологии, возрастает и энергопотребление). Вследствие этого, CMOS-схемы стали наиболее популярной технологией при реализации цифровых логических устройств.

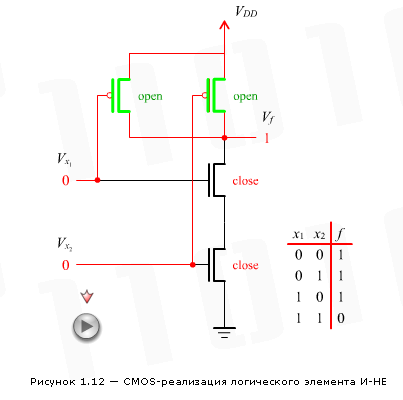

Рисунок 1.12 представляет принципиальную электрическую схему логического элемента И-НЕ CMOS. Реализация этого элемента подобна NMOS-схеме, представленной на рисунке 1.5 за исключением того, что токоограничивающий резистор был заменен блоком PUN, состоящим из двух PMOS-транзисторов, соединенных параллельно. Таблица истинности на рисунке показывает состояние каждого из этих четырех транзисторов для каждой логической комбинации вводов x1 и x2. Легко проверить, что данная схема реализует логическую функцию И-НЕ. В статическом состоянии отсутствует путь для протекания тока от VDD к Gnd.

Схема на рисунке 1.12 может быть получена исходя из логического выражения, которое определяет логическую функцию И-НЕ,  . Это выражение определяет состояния, при которых f = 1; следовательно, оно определяет поведение блока PUN. Так как этот блок состоит из PMOS-транзисторов, которые открываются при подаче на их входы логического нуля, входная переменная xi открывает транзистор, если xi=0. По правилу де Моргана мы имеем:

. Это выражение определяет состояния, при которых f = 1; следовательно, оно определяет поведение блока PUN. Так как этот блок состоит из PMOS-транзисторов, которые открываются при подаче на их входы логического нуля, входная переменная xi открывает транзистор, если xi=0. По правилу де Моргана мы имеем:

Таким образом f = 1, когда либо вход x1, либо вход x2 имеют значение логического нуля, что означает что PUN должен иметь два PMOS-транзистора, соединенных параллельно. Блок PDN должен дополнять функцию f, которая имеет вид: f = x1x2

Функция f = 1, когда оба входа x1 и x2 равны 1, поэтому блок PDN должен иметь два NMOS-транзистора, соединенных последовательно.

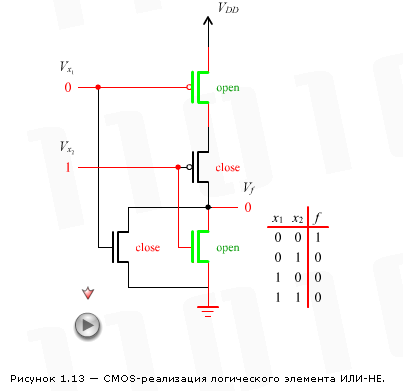

Схема для CMOS-реализации элемента ИЛИ-НЕ может быть получена из логического выражения:

Функция f = 1 в том случае, если x1 и x2 равны 0 одновременно. Тогда PUN состоит из двух PMOS-транзисторов, соединенных последовательно. Блок PDN, который реализует функцию f = x1 + x2, состоит из двух NMOS-транзисторов, соединенных параллельно, что и показано на рисунке 1.13.

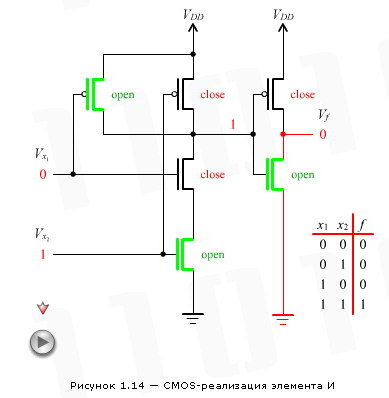

Элемент И в CMOS-реализации представляет собой последовательное соединение логического элемента И-НЕ и инвертора, как показано на рисунке 1.14. Точно так же элемент ИЛИ строится путем соединения элемента ИЛИ-НЕ с инвертором.

Вышеупомянутая процедура для получения СMOS-схем применяется для реализации большинства логических функций.

Дата: 2019-07-23, просмотров: 738.