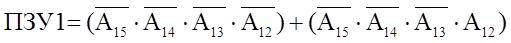

Схема 1. Построение функции для ПЗУ

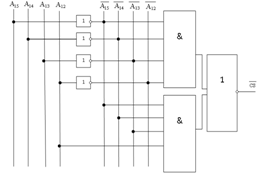

Схема 2. Построение функции для ПЗУ 2

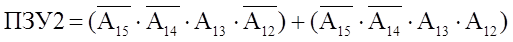

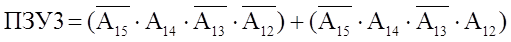

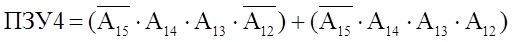

Схема 3. Построение функции для ПЗУ

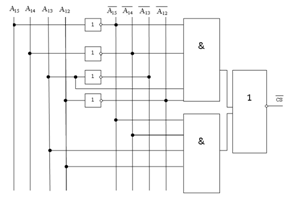

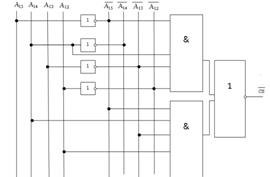

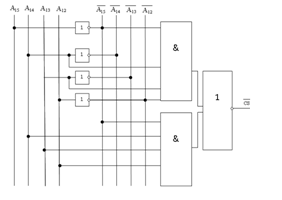

Схема 3. Построение функции для ПЗУ 4

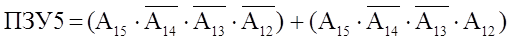

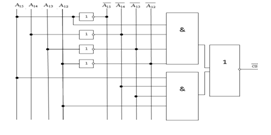

Схема 5. Построение функции для ПЗУ 1

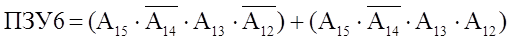

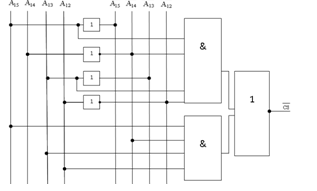

Схема 6. Построение функции для ПЗУ 1

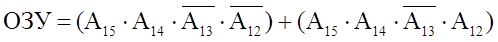

Схема 7. Построение функции для ОЗУ 1

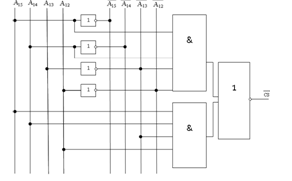

В качестве анализа четырех старших разрядов шины адреса можно использовать дешифратор двоично-десятичный, который получив двоичный код на входе активирует выход с соответствующим номером. Выходы дешифратора для каждой микросхемы объединяем функцией И.

Схема 8. Построение с помощью дешифратора

2.3 Расчет и планирование адресного для устройств ввода-вывода .

Для устройств ввода-вывода планирование адресов выполняется аналогично.

Таблица 14. Расположение микросхем устройств ввода-вывода по адресам.

| 00h 03h | ВН59 |

| 04h 05h | ВИ53 |

| 06h 07h | ВВ51 |

| 08h 09h | ВВ79 |

| AFh FFh | Не используется |

Следующим этапом следует расчет и построение дешифрации адресов устройств ввода-вывода.

Таблица 15. Расчет адресов памяти

| А15 | А14 | А13 | А12 | А11 | А10 | А9 | А8 | А7 | А6 | А5 | А4 | А3 | А2 | А1 | А0 | ||

| ВН59 | 00h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 01h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | |

| ВИ53 | 02h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 03h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | |

| ВВ51 | 04h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 05h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | |

| ВВ79 | 06h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 07h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | |

| Не исп. | 08h | ||||||||||||||||

| FFh |

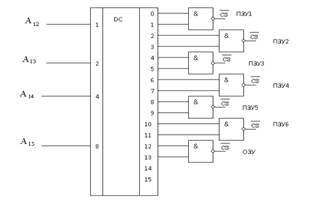

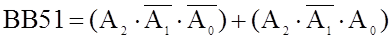

2.4 Построение схем дешифрации адресов устройств ввода-вывода

Схема 8. Построение функции для ВВ51

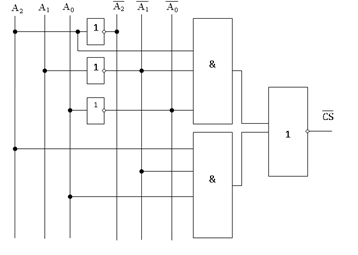

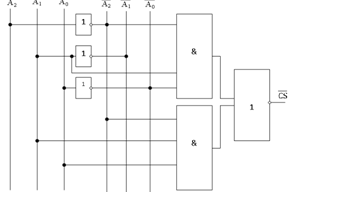

Схема 9. Построение функции для ВИ53

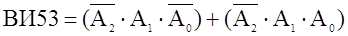

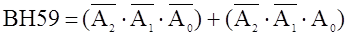

Схема 10. Построение функции для ВН59

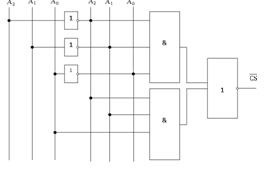

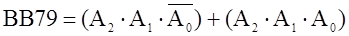

Схема 11. Построение функции для ВВ79

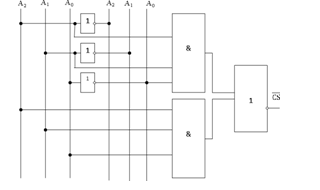

В качестве анализа четырех старших разрядов шины адреса можно использовать дешифратор двоично-десятичный, который получив двоичный код на входе активирует выход с соответствующим номером.

Выходы дешифратора для каждой микросхемы объединяем функцией И.

Схема 12. Построение с помощью дешифратора.

|

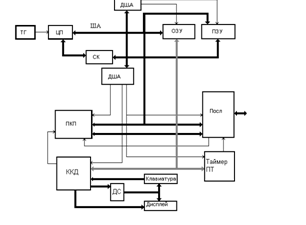

3. Структурная схема.

Таблица 16. Перечень элементов структурной схемы

| № п/п | Обозначение | Тип элемента | Тип микросхемы |

| 1 | ТГ | Генератор тактовых импульсов | КР580ГФ24 |

| 2 | ЦП | Центральный процессор | КР580ВМ80 |

| 3 | ДША | Дешифратор адреса | |

| 4 | ОЗУ | Оперативное запоминающее устройство | К537РУ17 |

| 5 | ПЗУ | Постоянное запоминающее устройство | К573РФ6 |

| 6 | СК | Системный контроллер | КР580ВК28 |

| 7 | ПКП | Программируемый контроллер прерывания | КР580ВН59 |

| 8 | ПИ | Программируемый последовательный интерфейс | КР580ВВ51 |

| 9 | ТП | Таймер | КР580ВН53 |

| 10 | ККД | Контроллер клавиатуры и дисплея | КР580ВВ79 |

| 11 | ДС | Схема управления дисплеем | К514ИД2 |

Структурная схема определяет основной состав изделия, его назначение и взаимосвязь.

Тактовый генератор (ТГ) формирует сигнал системного сброса RESET для установки ЦП и других устройств в начальное состояние, а так же импульсы для синхронизации работы устройств. Своими сигналами генератора тактовых импульсов обеспечивает требуемую последовательность работы всех устройств микропроцессорной системы.

Микропроцессор формирует адресную шину ША мультиплексированную шину данных ШД с шиной управления ШУ. Для увеличения нагрузочной способности шины адреса используется буферный регистр.

Демультиплексирование осуществляет системный контроллер СК, формируя на своих выходах шину данных ШД и управляющие сигналы.

Выборку микросхем памяти ОЗУ и ПЗУ, в зависимости от состояния адресных линий ША, осуществляет дешифратор ДС.

Микропроцессорная система содержит контроллер последовательного интерфейса, передатчики и приемники, которые синхронизируются независимо друг от друга сигналами от интервального таймера ПТ. Контроллер последовательного интерфейса занимает две линии прерывания, которые обслуживают контроллер прерываний ПКП.

При поступлении прерывания контроллер ПКП формирует сигнал микропроцессору, а тот в свою очередь, если прерывания разрешены, формирует сигнал.

Функции ввода с клавиатуры и отображения информации на индикаторах обеспечивает контроллер ККД.

Таблица 17. Состав принципиальной схемы.

| № | Микросхема | Обозначение на схеме |

| 1 | КР580ВМ80 | DD1 |

| 2 | КР580ГФ24 | DD2 |

| 3 | К1533АП5 | DD3, DD4 |

| 4 | КР580ВК28 | DD5 |

| 5 | К573РФ5 | DD7 |

| 6 | К155ЛН1 | DD8 |

| 7 | КР537РУ17 | DD9 |

| 8 | К155ИД3 | DD10 |

| 9 | КР580ВВ51 | DD17 |

| 10 | КР580ВВ79 | DD18 |

| 11 | К155ЛИ6 | DD22 |

| 12 | К514ИД2 | DD25, |

| 13 | CD8-BW30R6-A11 | HL1 |

| 14 | Разъем последовательного интерфейса | XC4 |

Центральное процессорное устройство включает в себя микропроцессор ВМ80 в минимальном окружении дополнительных микросхем:

1) Тактовый генератор ГФ24, который синхронизируется кварцевым резонатором с частотой 18 МГц. Вход RDYIN подключен через сопротивление 1 кОм для формирования высокого уровня на этом выходе. Вход RESIN подключен к кнопке с нормально разомкнутыми контактами, RC цепь предназначена для формирования сигнала RESET в момент включения МПС и для защиты от дребезга контактов кнопки. В цепь кварцевого резонатора включена емкость 20 нФ для запуска генератора в момент подачи напряжения.

2) Буферные регистры АП5 предназначены для увеличения нагрузочной способности шины адреса (System Address Bus) микропроцессора.

3) Системный контроллер ВК28 формирует на своих выходах системную шину данных (System Data Bus) и шину управления (System Control Bus). Его входы STSTB, HLDA, WR, DBIN подключены к соответствующим выходам микропроцессора и тактового генератора. Вход BUSEN заземлен.

К сформированным шинам подключаются остальные контроллеры, а также модули памяти ПЗУ и ОЗУ. Выборку контроллеров осуществляют дешифраторы DD10, DD11.

В проектируемой МПС обслуживание прерываний осуществляет один контроллер ВН59. Он подключается к 8-разрядной системной шине данных (ШД), а также к шине управления (ШУ). Для адресной выборки внутренних регистров используется линия адреса А0 от шины адреса (ША). К входам IR0-IR7 подключаются контроллеры, которым необходимы прерывания. Так как каскадирования не требуется, поэтому инверсный вход SP/EN заземляется.

Формирование трех 8-битных двунаправленных интерфейса Port A, B, C осуществляет контроллер ВВ55. Его выводы подключаются к соответствующим линиям ШД, ША, ШУ. Данный контроллер работает в режиме M1, поэтому линии PA0-7 и PB0-7 работают ввод и вывод соответственно, а линии PC0-7 используются для управляющих сигналов.

Функции ввода с 128-клавишной клавиатуры и отображения информации на одном 8-разрядном цифровых дисплеях HL1 выполняет контроллер ВВ79. Для сканирования клавиатуры контроллер формирует двоичный код на линиях SL0-SL3, анализируя при этом состояние линий RL0-RL7. Преобразование двоичного кода в кодовые последовательности М0-М15 выполняет дешифратор столбцов DD24, DD27. Выходы этих дешифраторов подключены к разрядам 7-сегментных индикаторов, а также к линиям клавиатуры. Непосредственное управление индикаторами с общим анодом осуществляют дешифраторы К514ИД2, преобразующие двоичный код с линий PA0-PA2, PB0-PB2 в 7-сегментный код. Линии PA3, PB3 подключены напрямую на вывод H индикаторов, который относится к светодиоду десятичной точки. Вход S подключается к выходу BD контроллера для гашения индикаторов.

Заключение

В данном курсовом проекте была получена МПС на базе комплекта КР580. Данная МПС обладает относительно небольшим быстродействием. Она позволяет решать задачи, связанные с управлением разнообразными технологическими операциями. Разработанная система позволяет подключать устройства, которые требуют динамического изменения временных и частотных характеристик их входных сигналов. Присутствие в этой МПС программируемого параллельного интерфейса КР580ВВ55 предусматривает три канала, к которым можно подключать УВВ, обменивающихся 8-разрядными словами, а также позволяет гибко манипулировать этими каналами, изменяя их предназначение. КР580ВМ80 является микропроцессором с фиксированным набором команд, что облегчает составление программ. Объем ПЗУ позволяет записать достаточно функциональную программу, расширяя тем самым возможности данной МПС.

Список используемой литературы

1. Большие интегральные схемы запоминающих устройств: Справочник. – М.: Радио и связь, 1990.

2. Калабеков Б.А.. “Цифровые устройства и микропроцессорные системы”. Москва 2003г.

3. Г. И. Пухальский. “Проектирование микропроцессорных систем”. Санкт-Петербург 2001г.

4. Справочник, М.: Редакция, 1991 – 196 c. Интегральные микросхемы зарубежных стран и их аналоги производства СССР.

5. Интернет-сайт: http://www.computer-museum.ru.

6. Интернет-сайт: http://www.wikipedia.org.ru

Дата: 2019-05-29, просмотров: 389.