Содержание

Введение

1. Описание применяемых элементов

1.1 Микропроцессор КР580ВМ8

1.2 Генератор тактовых импульсов КР580ГФ2

1.3 Контроллер прерываний КР580ВН5

1.4 Системный контроллер КР580ВК28

1.5 Программируемый последовательный интерфейс КР580ВВ51

1.6 Контроллер клавиатуры и дисплея КР580ВВ79

1.7 Микросхема ОЗУ К537РУ17

1.8 Микросхема ПЗУ К573РФ6

1.9 Микросхема дешифратора К155ИД3

1.10 Микросхема К514ИД2

1.11 Буферный регистр 1533АП5

2. Расчетная часть

2.1 Расчет и планирование адресного пространства памяти

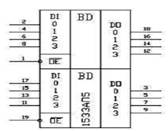

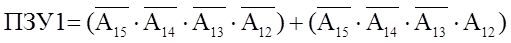

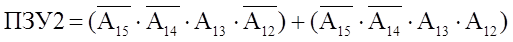

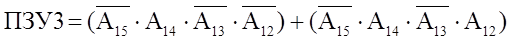

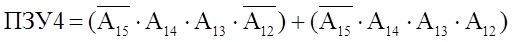

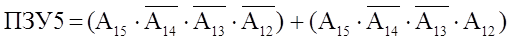

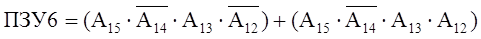

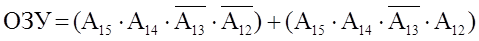

2.2 Построение схем дешифрации адресов памяти

2.3 Расчет и планирование адресного для устройств ввода-вывода

2.4 Построение схем дешифрации адресов устройств ввода-вывода

3. Структурная схема

4. Принципиальная схема

Заключение

Список используемой литературы

Введение

В данном курсовом проекте рассмотрен микропроцессорный комплект серии КР580. Этот набор микросхем, аналогичен набору микросхем Intel 82xx. Представляет собой 8-разрядный комплект на основе n-МОП технологии. Система команд СМ1800, ГОСТ 11305.910-80. Большинство микросхем является аналогами чипов серии MCS-85 фирмы Intel.

В настоящее время для построения различных микропроцессорных систем, устройств обработки информации и различных устройств вычислительной техники широко используются микропроцессорные системы на базе серии КР580.

В комплект КР580 входит:

- Микропроцессор КР580ВМ80;

- Системный контроллер КР580ВК28;

- Параллельный интерфейс КР580ВВ55;

- Контроллер прерываний КР580ВМ59;

- Контроллер клавиатуры и дисплея КР580ВВ79.

Хотя этот микропроцессорный комплект был создан в восьмидесятых годах, он широко используется до сих пор и изучается в различных образовательных заведениях так как, изучив его, можно понять работу более сложных микропроцессорных систем.

Микропроцессор КР580 используется в различных системах с не высокими требованиями к производительности, и в тех системах, когда использование более мощных процессоров экономически не выгоден.

Данный курсовой проект необходим, для того чтобы учащиеся изучили основные элементы микропроцессорного комплекта, поняли их работу, научились самостоятельно строить микропроцессорные системы, научились находить неполадки и устранять их.

Описание используемых элементов

Микропроцессор кр580вм80

Процессор содержит 4500 транзисторов по технологии 6 мкм n-МДП Тактовая частота процессора КР580ВМ80 - 2 МГц. Каждая команда выполняется за 1..5 машинных циклов, каждый из которых состоит из 3..5 тактов. Средняя производительность 200..300 тыс. операций в секунду на частоте 2 МГц. Микропроцессор имеет раздельные 16-разрядную шину адреса и 8-разрядную шину данных. 16-разрядная шина адреса обеспечивает прямую адресацию внешней памяти объемом до 64 Кбайт и 256 устройств ввода/вывода.

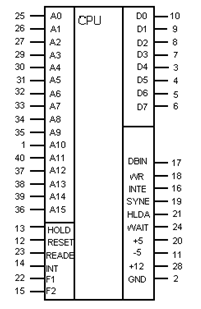

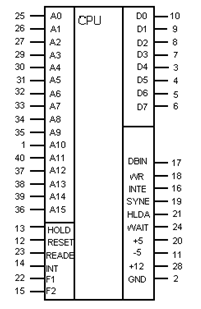

Рисунок 1. Условное обозначение микросхемы КР580ВМ80

Таблица 1.Назначение выводов микропроцессора КР580ВМ80

| Вывод | Обозначение | Назначение выводов |

| 6,5,4,3,7,8,9,10 | D0-7 | Двунаправленная шина данных |

| 25,26,27,29,30,31,32,33,34,35, 1,40,37,38,39,36 | А0-15 | Шина адреса |

| 15,22 | F1, F2 | Тактовые сигналы |

| 13 | HOLD | Запрос захвата шин |

| 14 | INT | Запрос прерывания |

| 23 | READY | Готовность |

| 12 | RESET | Сигнал системного сброса |

| 16 | INTE | Разрешение прерывания |

| 17 | DBIN | Ввод с шины данных |

| 18 | WR | Запись |

| 19 | SYNC | Сигнал синхронизации |

| 21 | HLDA | Подтверждение захвата шин |

| 24 | WAIT | Ожидание или подтверждение состояния ожидания |

| 11 | -5V | -5В |

| 20 | +5V | +5В |

| 28 | + 12V | + 12В |

| 2 | GND | Общий |

Контроллеры интерфейса RS 232

Микросхема КР580ВВ51

Микросхема КР580ВВ51-универсальна синхронный приемопередатчик, предназначен для аппаратной реализации последовательного протокола обмена между микропроцессором КР580ВМ80 и каналами последовательной передачи дискретной информации.

Микросхема преобразует параллельный код, получаемый от центрального процессора, в последовательный поток символов со служебными битами и выдает этот поток в последовательный канал связи с различной скоростью, а также выполняет обратное преобразование: последовательный поток символов в параллельный 8-разрядное слово.

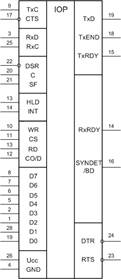

Рисунок 4.1. Условное обозначение микросхемы КР580ВВ51

Таблица 4. Назначение выводов микросхемы КР580ВВ51

| Вывод | Обозначение | Назначение вывода |

| 1, 2, 5-8, 27, 28 | D2-D7, D0, D1 | Канал данных - обмен информацией между микропроцессором и микросхемой |

| 3 | RxD | Приемник микросхемы |

| 4 | GND | Общий |

| 9 | TxC | Синхронизации передачи |

| 10 | WR | Запись информации |

| 11 | CS | Выбор микросхемы |

| 12 | CO/D | Управление (данные) |

| 13 | RD | Чтение информации |

| 14 | RxRDY | Готовность приемника |

| 15 | TxRDY | Готовность передатчика |

| 16 | SYNDET/BD | Двунаправленный трех - стабильный программируемый ввод/вывод |

| 17 | CTS | Готовность внешнего устройства принять данные |

| 18 | TxEND | Конец передачи |

| 19 | TxD | Передатчик микросхемы |

| 20 | C | Синхронизация |

| 21 | SR | Установка исходного состояния |

| 22 | DSR | Готовность внешнего устройства передать данные |

| 23 | RTS | Запрос приемника внешнего устройства на прием данных |

| 24 | DTR | Запрос передатчика внешнего устройства на прием данных |

| 25 | RxC | Синхронизация приема |

| 26 | Ucc | Напряжение питания +5В |

Таблица 4.1. Таблица истинности сигналов микросхемы КР580ВВ51

| Сигналы на входах |

Направление и вид информации | |||

| СО/D | RD | WR | CS | |

| 1 | 1 | 0 | 0 | Канал данных системы управление |

| 0 | 1 | 0 | 0 | Канал данных системы данных |

| 1 | 0 | 1 | 0 | Канал данных системы состояния |

| 0 | 0 | 1 | 0 | Канал данных системы данных |

| Х | 1 | 1 | 0 | Высокоомныое состояние канала данных |

| Х | Х | Х | 1 | |

Таймер КР580ВИ53

Микросхема КР580ВИ53 -трехканальное программируемое устройство (таймер), предназначено для организации работы микропроцессорных систем в режиме реального времени. Программируемый таймер реализован в виде трех независимых 16-разрядных каналов с общей схемой управления. Каждый канал может работать в шести режимах.

Управляющее слово определяет режим работы канала, тип счета, формат чисел.

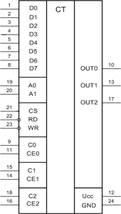

Рисунок 4.2. Условное обозначение микросхемы КР580ВИ53

Таблица 4.3. Назначение выводов микросхемы КР580ВИ53

| Вывод | Обозначение | Назначение выводов |

| 1-8 | D7-D0 | Канал данных |

| 9, 15, 18 | C0, C1, C2 | Синхронизация каналов 0-2 |

| 10, 13, 17 | OUT0, OUT1, OUT2 | Сигналы каналов 0, 1, 2 |

| 11, 14, 16 | CE0, CE1, CE2 | Сигналы каналов 0, 1, 2 |

| 12 | GND | Общий |

| 19, 20 | A0, A1 | Сигналы выбора каналов 0, 1, 2 |

| 21 | CS | Выбор микросхемы |

| 22 | RD | Чтение |

| 23 | WR | Запись |

| 24 | Ucc | Напряжение питания 5В |

Микросхема ОЗУ К537РУ17

Статическое асинхронное ОЗУ на основе КМОП-структур.

По заданию ОЗУ нам необходимо 8 кбайт. Следовательно, нам необходимо поставить 1 штуку.

Классификационные параметры К537РУ17:

· Информационная емкость – 64 Кбит = 8 Кбайт

· Организация - 8К*8

· Время выборки адреса - не более 200 нс.

· Выход - три состояния

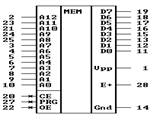

Рисунок 7. Условное обозначение микросхемы К537РУ17

Таблица 7. Назначение выводов микросхемы К537РУ17

| Выводы | Назначение | Обозначение |

| 2,3-10, 21,23,24,25 | Адресные входы | А12,А7-А0 А10,А11,А9,А8 |

| 11-13, 15-19 | Входы-выходы данных | DO0-DO2, DO3-DO7 |

| 20,26 | Выбор микросхемы | -CE1,CE2 |

| 22 | Разрешение по выходу | -OE |

| 27 | Сигнал записи - считывания | -WE |

| 28 | Напряжение питания | Ucc |

| 1 | Свободный | --- |

| 14 | Общий | 0 В |

Таблица 7.1. Таблица истинности микросхемы К537РУ17

| CE1 | CE2 | -OE | WE | A0-A12 | DO0-DO7 | Режим работы |

| M | M | X | X | X | Roff | Хранение |

| L | H | X | L | A | L | Запись 0 |

| L | H | X | L | A | H | Запись 1 |

| L | H | L | H | A | Данные в прямом коде | Считывание |

| L | H | H | H | A | Roff | Запрет выхода |

Примечание: М - Любая комбинация уровней или сигналов, отличная от - CE1=L, CE2=H.

Микросхема ПЗУ К573РФ6

По заданию 48 кбайт – не обходимо 6 штук.

Для стирания записанной информации микросхему нужно извлечь из контактного устройства, замкнуть все ее выводы полоской фольги и поместить под источник УФ освещения, обеспечив ее обдув. Однако стирание можно произвести , не извлекая микросхему из контактного устройства, но тогда нужно отключить напряжение питания и сигналы. Типовые источники стирающего излучения - дуговые ртутные лампы и лампы с парами ртути в кварцевых баллонах: ДРТ-220, ДБ-8 и др. Излучение проникает к кристаллу РПЗУ через прозрачное окно в крышке корпуса. Время стирания 30...60 минут.

Для предохранения от случайного стирания информации окно в крышке корпуса закрывается специальной пленкой.

Рисунок 8. Условное обозначение микросхемы К573РФ6

Таблица 8. Назначение выводов микросхемы К573РФ6

| Выводы | Назначение | Обозначение |

| 2-10, 21,23,24,25 | Адресные входы | А0 – A12 |

| 11-13, 15-19 | Входы-выходы данных | DO0-DO2, DO3-DO7 |

| 20,26 | Выбор микросхемы | -CE0,CE1 |

| 22 | Разрешение по выходу | -OE |

| 27 | Сигнал записи - считывания | -WE |

| 28 | Напряжение питания | E+ |

| 1 | Свободный | --- |

| 14 | Общий | Gnd |

Таблица 8.1. Таблица истинности К573РФ6

| A | CE | OE | РК | Upр | Ucc | |

| Хранение | X | Uн | X | X | E+ | +5В |

| Считывание | А | 1Л | 1Л | Ш | E+ | +5В |

| Контроль записи | А | 1Л | 1Л | Ш | + 19В | +5В |

| Запись слова | А | Ш | Ш | Ш | +19В | +5В |

Буферный регистр 1533АП5

Для увеличения нагрузочной способности шины адреса микропроцессора и согласования этих шин с памятью и внешними устройствами необходимы шинные формирователи. В этой МПС в качестве шинного формирователя шины адреса используются буферные регистры 1533АП5 (рис. 11.). Шина адреса имеет 16 разрядов, так как этот регистр имеет 8 разрядов, для построения буфера потребуется 2 микросхемы. Одна микросхема формирует буфер для разрядов шины адреса А0-А7, а другая — А8-А15. Назначение выводов приводится в таблице 16.

Рисунок. 11. Условное обозначение буферного регистра 1533АП5 с нумерацией выводов

Таблица 11. Назначение выводов БИС 1533АП5

Выводы

2, 4, 6, 8, 17, 15, 13, 11

Информационные выходы. Подключаются к соответствующим разрядам внешней шины

Входной сигнал “Разрешение выхода”. Если OE=0, то информационные выходы перекл. в высокоимпедансное состояние

Расчетная часть

2.1 Расчет и планирование адресного пространства памяти

По заданию необходима ПЗУ объемом 48 кбайт, взята микросхема объемом на 8 кбайт, следовательно, необходимо поставить таких 6 микросхем.

По заданию ОЗУ необходимо 8 кбайт. Взята микросхема объемом 8 кбайт.

Так как микропроцессор начинает выполнять программы с адреса 0 (после включения или сброса), то по этому начиная с адреса 0 должна быть, установлена ПЗУ, в которую записывается программа для начала работы устройства. В оставшейся части адресов памяти располагается ОЗУ.

Таблица 12. Расположение микросхем памяти по адресам

| Адрес | Тип памяти |

| 0000h 1FFFh | ПЗУ1 |

| 2000h 3FFFh | ПЗУ2 |

| 4000h 5FFFh | ПЗУ3 |

| 6000h 7FFFh | ПЗУ4 |

| 8000h 9FFFh | ПЗУ5 |

| A000h BFFFh | ПЗУ6 |

| C000h DFFFh | ОЗУ |

| E000h FFFFh | Устройством не используется |

Следующим этапом следует расчет и построение дешифрации адресов .

Таблица 13. Расчет адресов памяти

| А15 | А14 | А13 | А12 | А11 | А10 | А9 | А8 | А7 | А6 | А5 | А4 | А3 | А2 | А1 | А0 | ||

| ПЗУ1 | 0000h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1FFFh | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ПЗУ2 | 2000h | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 3FFFh | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ПЗУ3 | 4000h | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 5FFFh | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ПЗУ4 | 6000h | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 7FFFh | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ПЗУ5 | 8000h | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 9FFFh | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ПЗУ6 | А000h | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| BFFFh | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ОЗУ | C000h | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| DFFFh | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| Нет устр-в | E000h | ||||||||||||||||

| FFFFh |

Заключение

В данном курсовом проекте была получена МПС на базе комплекта КР580. Данная МПС обладает относительно небольшим быстродействием. Она позволяет решать задачи, связанные с управлением разнообразными технологическими операциями. Разработанная система позволяет подключать устройства, которые требуют динамического изменения временных и частотных характеристик их входных сигналов. Присутствие в этой МПС программируемого параллельного интерфейса КР580ВВ55 предусматривает три канала, к которым можно подключать УВВ, обменивающихся 8-разрядными словами, а также позволяет гибко манипулировать этими каналами, изменяя их предназначение. КР580ВМ80 является микропроцессором с фиксированным набором команд, что облегчает составление программ. Объем ПЗУ позволяет записать достаточно функциональную программу, расширяя тем самым возможности данной МПС.

Список используемой литературы

1. Большие интегральные схемы запоминающих устройств: Справочник. – М.: Радио и связь, 1990.

2. Калабеков Б.А.. “Цифровые устройства и микропроцессорные системы”. Москва 2003г.

3. Г. И. Пухальский. “Проектирование микропроцессорных систем”. Санкт-Петербург 2001г.

4. Справочник, М.: Редакция, 1991 – 196 c. Интегральные микросхемы зарубежных стран и их аналоги производства СССР.

5. Интернет-сайт: http://www.computer-museum.ru.

6. Интернет-сайт: http://www.wikipedia.org.ru

Содержание

Введение

1. Описание применяемых элементов

1.1 Микропроцессор КР580ВМ8

1.2 Генератор тактовых импульсов КР580ГФ2

1.3 Контроллер прерываний КР580ВН5

1.4 Системный контроллер КР580ВК28

1.5 Программируемый последовательный интерфейс КР580ВВ51

1.6 Контроллер клавиатуры и дисплея КР580ВВ79

1.7 Микросхема ОЗУ К537РУ17

1.8 Микросхема ПЗУ К573РФ6

1.9 Микросхема дешифратора К155ИД3

1.10 Микросхема К514ИД2

1.11 Буферный регистр 1533АП5

2. Расчетная часть

2.1 Расчет и планирование адресного пространства памяти

2.2 Построение схем дешифрации адресов памяти

2.3 Расчет и планирование адресного для устройств ввода-вывода

2.4 Построение схем дешифрации адресов устройств ввода-вывода

3. Структурная схема

4. Принципиальная схема

Заключение

Список используемой литературы

Введение

В данном курсовом проекте рассмотрен микропроцессорный комплект серии КР580. Этот набор микросхем, аналогичен набору микросхем Intel 82xx. Представляет собой 8-разрядный комплект на основе n-МОП технологии. Система команд СМ1800, ГОСТ 11305.910-80. Большинство микросхем является аналогами чипов серии MCS-85 фирмы Intel.

В настоящее время для построения различных микропроцессорных систем, устройств обработки информации и различных устройств вычислительной техники широко используются микропроцессорные системы на базе серии КР580.

В комплект КР580 входит:

- Микропроцессор КР580ВМ80;

- Системный контроллер КР580ВК28;

- Параллельный интерфейс КР580ВВ55;

- Контроллер прерываний КР580ВМ59;

- Контроллер клавиатуры и дисплея КР580ВВ79.

Хотя этот микропроцессорный комплект был создан в восьмидесятых годах, он широко используется до сих пор и изучается в различных образовательных заведениях так как, изучив его, можно понять работу более сложных микропроцессорных систем.

Микропроцессор КР580 используется в различных системах с не высокими требованиями к производительности, и в тех системах, когда использование более мощных процессоров экономически не выгоден.

Данный курсовой проект необходим, для того чтобы учащиеся изучили основные элементы микропроцессорного комплекта, поняли их работу, научились самостоятельно строить микропроцессорные системы, научились находить неполадки и устранять их.

Описание используемых элементов

Микропроцессор кр580вм80

Процессор содержит 4500 транзисторов по технологии 6 мкм n-МДП Тактовая частота процессора КР580ВМ80 - 2 МГц. Каждая команда выполняется за 1..5 машинных циклов, каждый из которых состоит из 3..5 тактов. Средняя производительность 200..300 тыс. операций в секунду на частоте 2 МГц. Микропроцессор имеет раздельные 16-разрядную шину адреса и 8-разрядную шину данных. 16-разрядная шина адреса обеспечивает прямую адресацию внешней памяти объемом до 64 Кбайт и 256 устройств ввода/вывода.

Рисунок 1. Условное обозначение микросхемы КР580ВМ80

Таблица 1.Назначение выводов микропроцессора КР580ВМ80

| Вывод | Обозначение | Назначение выводов |

| 6,5,4,3,7,8,9,10 | D0-7 | Двунаправленная шина данных |

| 25,26,27,29,30,31,32,33,34,35, 1,40,37,38,39,36 | А0-15 | Шина адреса |

| 15,22 | F1, F2 | Тактовые сигналы |

| 13 | HOLD | Запрос захвата шин |

| 14 | INT | Запрос прерывания |

| 23 | READY | Готовность |

| 12 | RESET | Сигнал системного сброса |

| 16 | INTE | Разрешение прерывания |

| 17 | DBIN | Ввод с шины данных |

| 18 | WR | Запись |

| 19 | SYNC | Сигнал синхронизации |

| 21 | HLDA | Подтверждение захвата шин |

| 24 | WAIT | Ожидание или подтверждение состояния ожидания |

| 11 | -5V | -5В |

| 20 | +5V | +5В |

| 28 | + 12V | + 12В |

| 2 | GND | Общий |

Дата: 2019-05-29, просмотров: 402.